引言

在当今的电子设计领域,高速、高性能且低功耗的A/D转换器需求日益增长。ADC08D500作为一款备受瞩目的产品,以其独特的特性和出色的性能,在众多应用场景中发挥着重要作用。本文将深入剖析ADC08D500的各项特性、技术参数以及应用要点,为电子工程师们在设计过程中提供全面的参考。

文件下载:adc08d500.pdf

一、产品概述

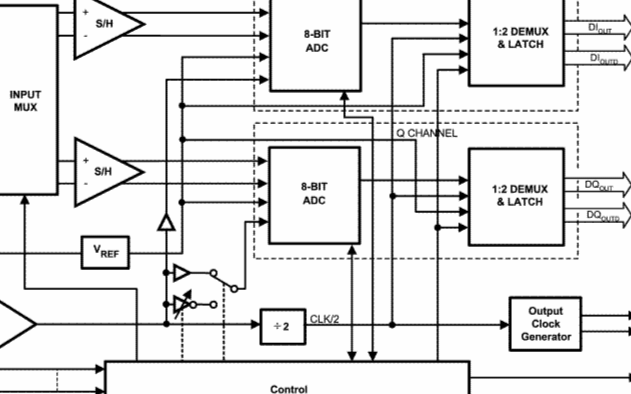

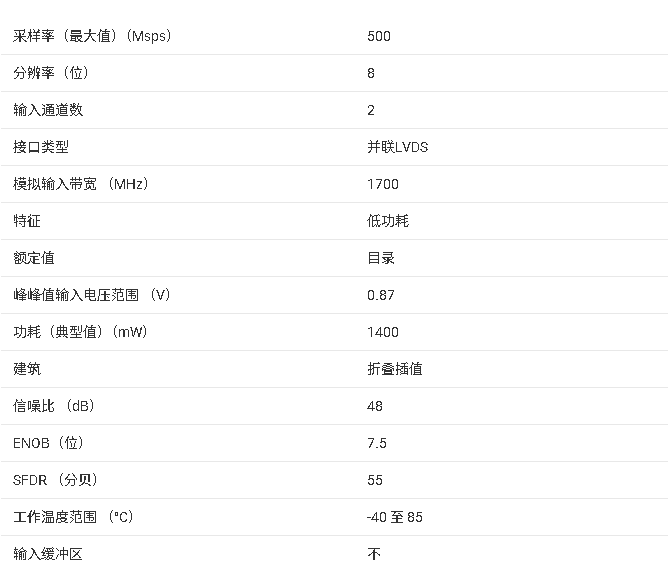

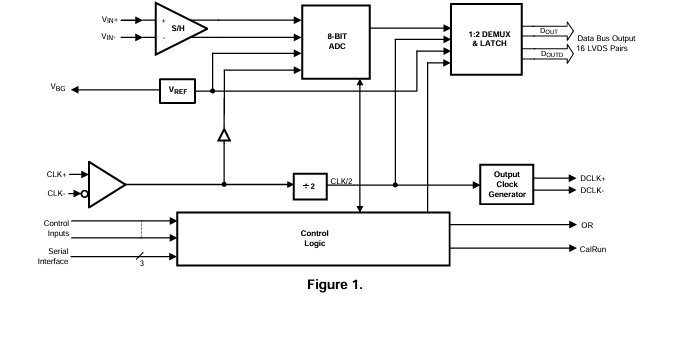

ADC08D500是一款双路、低功耗、高性能的CMOS模拟 - 数字转换器,能够以高达500 MSPS的采样率将信号数字化为8位分辨率。它采用了校准折叠和插值架构,实现了超过7.5个有效位,大大减少了比较器数量和功耗。同时,插值技术减少了前端放大器的需求,进一步降低了功率要求。片上校准还减少了折叠架构中常见的INL弯曲,最终实现了极快、高性能、低功耗的转换。

二、关键特性

2.1 内部采样保持

内部集成采样保持电路,确保在高速采样过程中准确捕获输入信号。

2.2 单电源供电

仅需单一的 +1.9V ±0.1V电源即可正常工作,简化了电源设计。

2.3 输出时钟模式选择

提供SDR(单数据速率)或DDR(双数据速率)输出时钟模式,满足不同应用场景的需求。

2.4 交错模式

支持交错模式,可将采样率提高一倍,达到2倍采样速率。

2.5 多ADC同步能力

能够精确同步多个ADC的采样时钟输入与DCLK输出关系,确保多个ADC在系统中的DCLK(和数据)输出同时转换。

2.6 无丢失码保证

在整个工作温度范围内确保无丢失码,保证了转换的准确性。

2.7 串行接口

提供串行接口,用于扩展控制和对输入满量程范围及偏移进行精细调整。

2.8 占空比校正采样时钟

采用占空比校正采样时钟,提高了时钟信号的稳定性和可靠性。

三、应用领域

3.1 直接RF下变频数字示波器

能够快速准确地将射频信号转换为数字信号,为示波器提供高精度的测量数据。

3.2 卫星机顶盒

在卫星信号接收和处理中,实现高速、准确的信号转换,确保图像和声音的高质量传输。

3.3 通信系统

为通信系统中的信号处理提供关键支持,保证信号的准确传输和处理。

3.4 测试仪器

在各种测试仪器中,提供高精度的模拟 - 数字转换,确保测试结果的准确性。

四、关键技术参数

4.1 分辨率与转换速率

分辨率为8位,最大转换速率可达500 MSPS(最小值),能够满足高速信号处理的需求。

4.2 误码率

典型误码率为 $10^{-18}$,意味着在长时间运行中,出现错误的概率极低,保证了数据的可靠性。

4.3 有效位数(ENOB)

在250 MHz输入时,典型ENOB为7.5位,表明转换器在高频输入下仍能保持较高的性能。

4.4 差分非线性(DNL)

典型DNL为 ±0.15 LSB,保证了转换的线性度。

4.5 功耗

- 工作状态下,典型功耗为1.4 W。

- 掉电模式下,典型功耗仅为3.5 mW,大大降低了系统的功耗。

五、功能详细解析

5.1 自校准功能

ADC08D500在上电时会自动进行自校准,用户也可以通过命令手动触发校准。校准过程会对100Ω模拟输入差分终端电阻进行微调,最小化满量程误差、偏移误差、DNL和INL,从而最大化SNR、THD、SINAD(SNDR)和ENOB。内部偏置电流也会在校准过程中进行设置。需要注意的是,自校准必须在上电时运行,并且在FSR引脚状态改变时需要重新运行。为了获得最佳性能,建议在上电20秒或更长时间后以及工作温度发生显著变化时进行自校准。

5.2 输入采集

数据在CLK+(引脚18)的下降沿进行采集,采集到的数据在13个时钟周期后(DI和DQ输出总线)或14个时钟周期后(DId和DQd输出总线)以数字形式出现在数字输出端。在数据输出之前,还存在一个额外的内部延迟 $t_{OD}$。只要时钟信号存在,ADC08D500就会持续进行转换。

5.3 控制模式

- 正常控制模式:用户可以通过几个控制引脚来实现大部分控制功能,如校准周期的启动、掉电模式的设置和满量程范围的设置。

-

扩展控制模式:通过串行接口访问基于寄存器的控制,提供了更多的高级功能。在扩展控制模式下,一些基于引脚的控制功能将被基于寄存器的控制所取代。需要注意的是,扩展控制模式不建议动态启用和禁用,用户应始终选择正常控制模式或扩展控制模式之一。

5.4 双边缘采样(DES)模式

DES模式允许将一个输入(I或Q通道)路由到两个ADC,实现对同一输入信号在时钟的两个边缘进行采样,从而使采样率达到输入时钟频率的两倍。在该模式下,输出以1:4解复用,每个输出总线的输出速率为输入时钟频率的一半。在非扩展模式下,只有“I”输入可以在DES模式下采样;在扩展模式下,用户可以选择采样的输入。此外,ADC08D500还包括自动时钟相位背景校准功能,可自动连续调整I和Q通道的时钟相位,提供最佳的双边缘采样ENOB性能。

5.5 电源管理

- 正常工作状态:当Power Down引脚(PD)为低电平时,ADC08D500处于活动状态。

- 掉电模式:当PD引脚为高电平时,设备进入掉电模式,输出引脚保持PD引脚变高之前的最后一次转换结果,设备功耗降至最低水平。PDQ引脚为高电平时,“Q”通道将进入掉电模式,而“I”通道保持活动状态。需要注意的是,在返回正常操作时,流水线中会包含无意义的信息。

六、应用信息

6.1 参考电压

ADC08D500的参考电压来自1.254V的带隙参考,通过引脚31($V_{BG}$)提供给用户,输出电流能力为 ±100 μA。如果需要更多电流,建议对其进行缓冲。内部带隙参考电压的标称值为650 mV或870 mV,由FSR引脚决定。在扩展控制模式下,可以通过配置寄存器调整满量程输入电压。

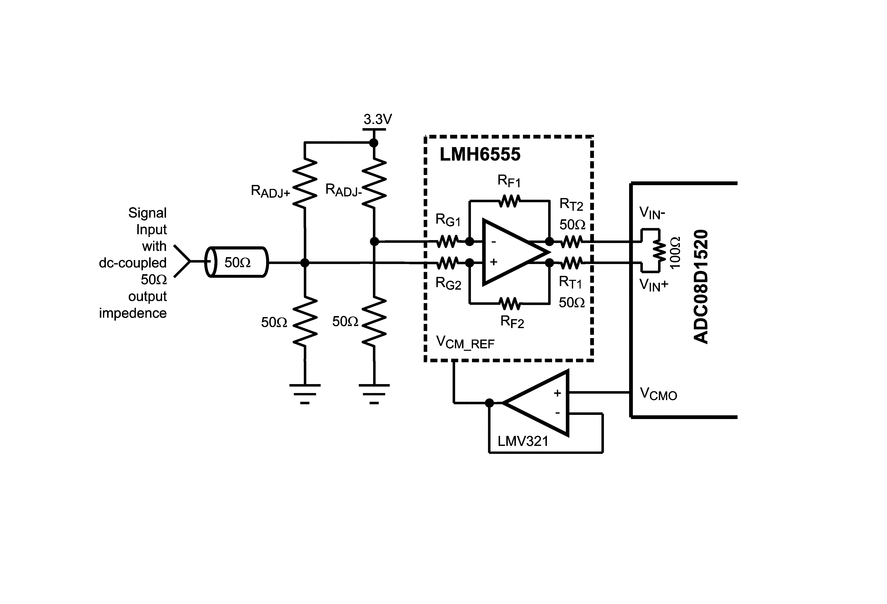

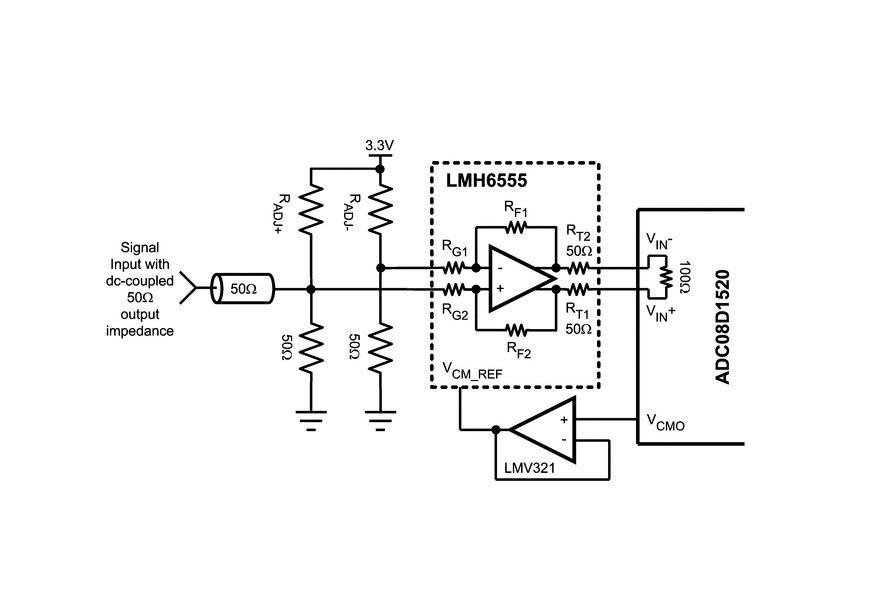

6.2 模拟输入

- 输入范围选择:模拟输入为差分输入,满量程输入范围可以通过FSR引脚选择为650 mVp-p或870 mVp-p,在扩展控制模式下,还可以通过串行接口将其调整为560 mVp-p至840 mVp-p之间的值。为了获得最佳性能,建议在扩展控制模式下将满量程范围保持在595 mVp-p至805 mVp-p之间。

- 输入耦合方式:输入信号可以采用交流耦合或直流耦合方式。在交流耦合时,$V{CMO}$输出必须接地;在直流耦合时,需要提供与$V{CMO}$输出相匹配的共模电压。

-

单端输入处理:ADC08D500不支持直接处理单端输入信号,建议使用合适的巴伦连接变压器将单端信号转换为差分信号后再输入到ADC。

6.3 时钟输入

- 时钟信号要求:ADC08D500的时钟输入为差分LVDS输入(CLK+和CLK-),必须使用差分、交流耦合的时钟信号驱动。时钟信号的频率应在电气特性表规定的范围内,并且时钟信号的高低时间应保持在规定的比例(20/80%)内,以确保ADC的性能。

-

时钟抖动要求:高速、高性能的ADC如ADC08D500需要非常稳定的时钟信号,最小化相位噪声或抖动。允许的抖动是输入频率和输入信号电平的函数,具体计算公式为 $t{J(MAX)}=\left(V{IB(P-P)} / V{IBFSR}\right) \times\left(1 /\left(2^{(N+1)} × \pi × f{IN}\right)\right)$,其中 $t{J(MAX)}$ 是所有抖动源的均方根总和,$V{IN(P-P)}$ 是模拟输入信号的峰 - 峰值,$V{INFSR}$ 是ADC的满量程范围,“N” 是ADC的分辨率位数,$f{IN}$ 是ADC模拟输入的最大输入频率。

6.4 数字输出

ADC08D500将每个ADC的输出数据解复用为两个LVDS输出总线,每个总线的字速率为ADC输入时钟速率的一半,需要将两个总线进行复用才能获得完整的转换结果。输出时钟对(DCLK+/-)可用于锁存LVDS输出,数据在DCLK的上升或下降沿输出由OutEdge引脚决定。此外,还支持DDR(双数据速率)时钟模式,在该模式下,每个DCLK边缘都会输出一个数据字,将DCLK频率降低到输入时钟频率的1/4。

七、设计注意事项

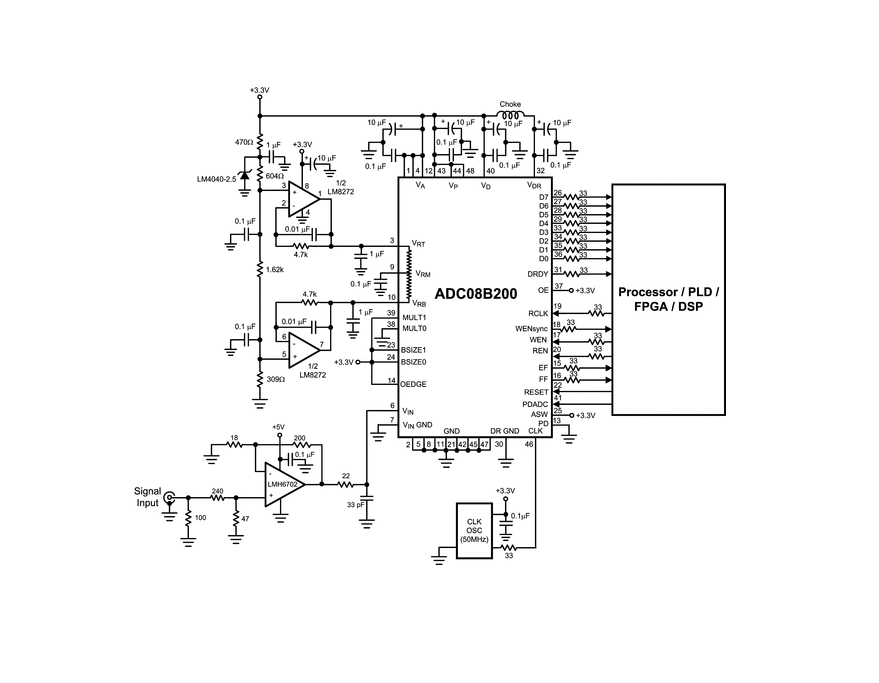

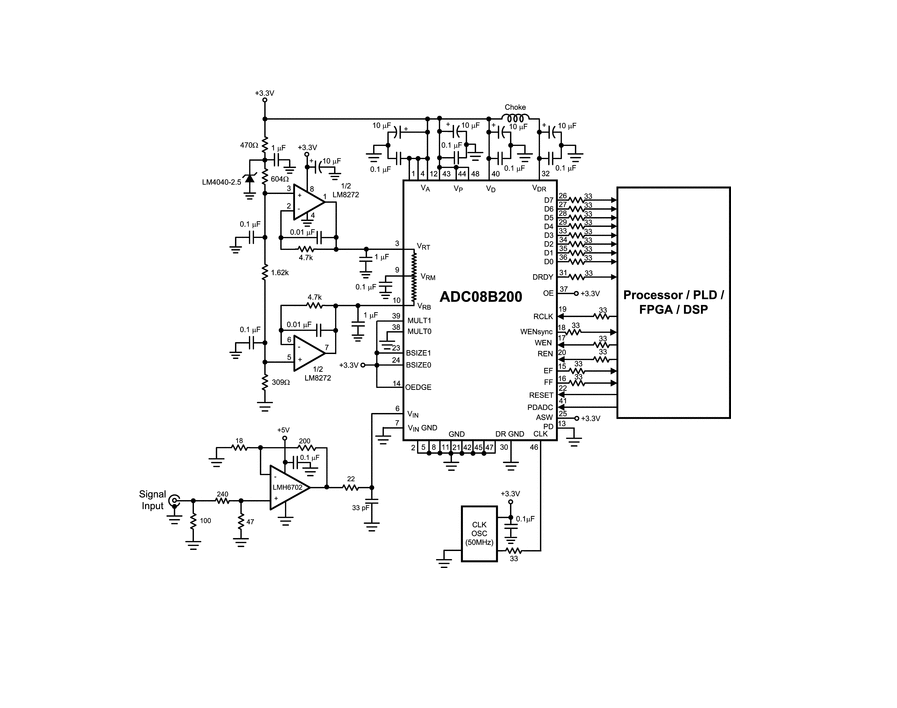

7.1 电源旁路

A/D转换器在工作时会产生足够的瞬态电流,如果电源旁路不足,可能会导致电源电压波动,影响转换器的性能。因此,建议在A/D转换器电源引脚附近(距离不超过1英寸,即2.5 cm)放置一个33 μF的电容,并在每个$V_{A}$引脚附近尽可能靠近放置一个0.1 μF的电容。优先选择无引脚芯片电容,因为它们的引脚电感较低。

7.2 电源电压限制

ADC08D500的电源电压应严格控制在1.9V ±0.1V范围内,任何引脚的电压都不应超过电源电压或低于地电压150 mV,即使是在瞬态情况下也不允许。在电源上电和关断过程中,要确保驱动输入引脚的电路电源与ADC08D500的电源同步上升,避免出现电压尖峰损坏器件。建议使用具有过冲保护功能的电源电路,如使用LM317线性调节器(输入电源电压为4V至5V)或LM1086线性调节器(使用3.3V电源),并在调节器输出端连接一个100Ω的电阻,以提供最小输出电流,防止上电时出现尖峰。

7.3 热管理

尽管ADC08D500在低功耗方面表现出色,但由于其高速运行,仍需要注意热管理。为了确保设备的可靠性,建议将芯片温度控制在最高130°C以下。ADC08D500的封装背面有一个暴露的焊盘,这是主要的散热路径,同时也能提供良好的电气接地。在PCB设计中,应在封装的足迹内包含一个热焊盘图案,将暴露的焊盘焊接到该图案上,以确保良好的热传导。热焊盘图案应至少与封装暴露焊盘的尺寸相同(5 x 5 mm),并与地电气连接。为了进一步降低结温,可以在PCB的另一侧设置一个约2平方英寸(6.5平方厘米)的铜区域,并使用热过孔将其与热焊盘图案连接起来。建议使用9至16个热过孔,过孔的直径为0.30至0.33 mm,间距为1.2 mm,并进行桶形电镀,以避免焊接过程中焊料吸入过孔,导致热阻增加。

7.4 布局和接地

正确的接地和信号布线对于确保准确的转换至关重要。建议使用单一的接地平面,而不是将接地平面分为模拟和数字区域。由于数字开关瞬变主要由高频分量组成,总接地平面的铜重量对逻辑产生的噪声影响较小,而总表面积更为重要。应将模拟电路与数字电路保持良好的分离,避免数字电路的噪声耦合到敏感的模拟电路中。

7.5 时钟信号处理

为了获得最佳的动态性能,应确保ADC时钟信号的低均方根抖动。建议将ADC时钟线尽可能缩短,远离其他信号,并将其视为传输线进行处理。其他信号可能会引入抖动到时钟信号中,而时钟信号如果不与模拟路径隔离,也可能会将噪声引入到模拟路径中。

7.6 串行接口使用

在使用串行接口时,必须确保在使用前至少对所有8个用户寄存器进行一次写入,写入默认值或所需值。首次写入DES Enable寄存器(Dh)时,必须加载默认值(0x3FFFh)。只有在所有寄存器都写入一次后,才能加载其他所需的设置,包括启用DES。

八、常见应用陷阱及避免方法

8.1 寄存器写入问题

在扩展控制模式下使用串行接口时,必须确保所有8个用户寄存器都至少写入一次默认值或所需值。特别是首次写入DES Enable寄存器(Dh)时,要加载默认值(0x3FFFh),否则可能会导致设备无法正常工作。

8.2 输入电压范围

为了确保设备的可靠性,任何输入电压都不应超过电源引脚电压150 mV或低于地引脚电压150 mV。即使是瞬态情况下超过这些限制,也可能导致设备故障或可靠性受损。在高速数字电路中,经常会出现下冲超过地电压1V的情况,因此需要控制高速线路的阻抗并将其终端匹配到特性阻抗,以控制过冲。

8.3 模拟输入共模电压

在直流耦合模式下,输入共模电压必须保持在$V{CMO}$输出的50 mV范围内,并且要跟踪$V{CMO}$输出随温度的变化。如果输入共模电压与$V_{CMO}$的偏差超过50 mV,会导致失真性能下降。

8.4 放大器选择

在选择用于驱动ADC08D500的高频放大器时要格外小心,因为许多高速放大器的失真可能会比ADC本身更高,从而导致整个系统的性能下降。

8.5 参考电压驱动

参考电压旨在提供固定的两个不同满量程值(650 mVp-p和870 mVp-p),过度驱动$V_{BG}$引脚不会改变满量程值,但可能会影响设备的正常运行。

8.6 时钟信号问题

- 时钟电平:ADC时钟电平不应超过操作额定表中规定的电平,否则可能会导致输入偏移发生变化。

-

时钟抖动:使用具有过大抖动的时钟源、过长的时钟信号走线或其他信号耦合到时钟信号走线,都会导致采样间隔变化,从而增加输出噪声并降低SNR性能。

8.7 散热问题

为了确保设备的可靠性,必须提供足够的散热措施,可以通过充足的气流或在电路板中内置简单的散热片来实现。同时,要确保封装背面的暴露焊盘接地良好,以获得最佳性能。

九、总结

ADC08D500以其高性能、低功耗和丰富的功能,为电子工程师们提供了一个优秀的A/D转换解决方案。在设计过程中,工程师们需要充分了解其各项特性和技术参数,注意应用中的各种细节和陷阱,以确保设备的正常运行和系统的高性能。希望本文能够为工程师们在使用ADC08D500进行设计时提供有价值的参考。

-

CMOS

+关注

关注

58文章

6184浏览量

241539 -

MSPS

+关注

关注

0文章

562浏览量

28770 -

A/D转换器

+关注

关注

1文章

142浏览量

11593 -

前端放大器

+关注

关注

0文章

13浏览量

9511

发布评论请先 登录

ADC08D500,pdf datasheet (High

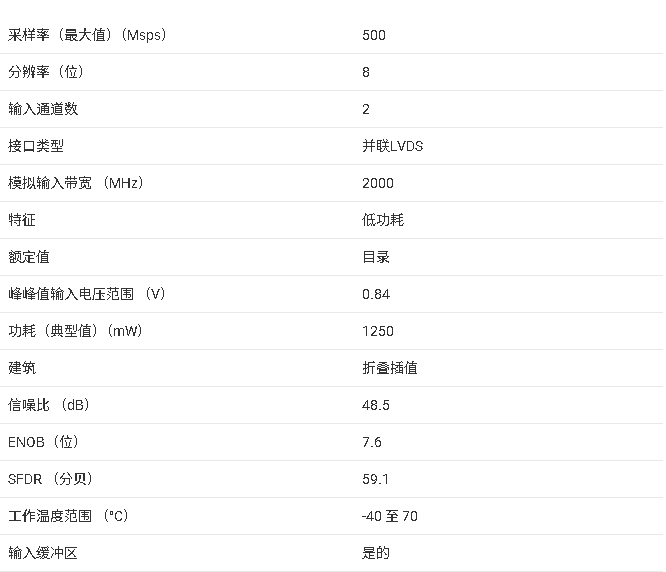

模数转换器ADC08D1500的性能特点及应用分析

ADC08D500双通道、低功耗、高性能CMOS模数转换器数据表

深入解析ADC08D1520:高性能8位ADC的卓越之选

深入解析ADC081S101:高性能8位单通道A/D转换器

深入解析ADC08D500:高性能低功耗8位500 MSPS A/D转换器

深入解析ADC08D500:高性能低功耗8位500 MSPS A/D转换器

评论