倾佳电子碳化硅MOSFET驱动电压解析:-5V的必要性及-5V/+18V作为技术能力检验标准的深层原因

倾佳电子(Changer Tech)是一家专注于功率半导体和新能源汽车连接器的分销商。主要服务于中国工业电源、电力电子设备和新能源汽车产业链。倾佳电子聚焦于新能源、交通电动化和数字化转型三大方向,并提供包括IGBT、SiC MOSFET、GaN等功率半导体器件以及新能源汽车连接器。

倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

倾佳电子杨茜咬住SiC碳化硅MOSFET功率器件三个必然,勇立功率半导体器件变革潮头:

倾佳电子杨茜咬住SiC碳化硅MOSFET模块全面取代IGBT模块和IPM模块的必然趋势!

倾佳电子杨茜咬住SiC碳化硅MOSFET单管全面取代IGBT单管和大于650V的高压硅MOSFET的必然趋势!

倾佳电子杨茜咬住650V SiC碳化硅MOSFET单管全面取代SJ超结MOSFET和高压GaN 器件的必然趋势!

执行摘要

倾佳电子深入分析了碳化硅(SiC)MOSFET应用中采用-5V关断驱动电压的工程意义,并阐释了为何-5V/+18V的驱动电压组合已成为检验,特别是国产SiC MOSFET制造商,技术能力与制造工艺成熟度的行业主流标准。

分析表明,-5V关断电压并非可选项,而是保障系统鲁棒性的工程必要措施。其核心意义在于:

对抗低阈值电压($V_{GS(th)}$):SiC MOSFET普遍具有较低的$V_{GS(th)}$(部分器件在恶劣情况下低至1V),0V关断的噪声裕量极低 。

抑制米勒(Miller)寄生开通:在硬开关拓扑(如半桥)中,极高的$dv/dt$速率会通过米勒电容($C_{gd}$)在关断器件的栅极上感应出正向电压尖峰,-5V驱动能提供足够的安全裕量以防止这种“串扰”导致的寄生开通 。

抑制$di/dt$引起的寄生开通:高$di/dt$与共源电感($L_s$)相互作用产生的感应电压同样会干扰栅源电压,-5V的低阻抗驱动路径能有效钳位此噪声 。

与此同时,+18V的开通电压是实现器件最佳性能(即最低导通电阻$R_{DS(on)}$)所必需的。SiC MOSFET的跨导($g_m$)相对较低,需要比传统硅基IGBT(+15V)更高的栅压来充分形成沟道 1。采用+18V而非+15V,能显著降低导通损耗,避免因高$R_{DS(on)}$导致的额外热应力 。

本报告的核心论点在于,-5V/+18V这一组合之所以成为“技术能力基准”,是因为它不单纯是性能和鲁棒性的优化点,更是对SiC MOSFET最核心、最脆弱的部件——栅极氧化层(Gate Oxide)——的“双重压力测试”。

+18V的挑战:在高温下施加高正栅压(+18V)会引发正偏压温度不稳定性(PBTI),导致电子陷获,使$V_{th}$随时间正向漂移(增大),进而恶化$R_{DS(on)}$ 。

-5V的挑战:在高温下施加负栅压(-5V)会引发负偏压温度不稳定性(NBTI),导致空穴陷获,使$V_{th}$随时间负向漂移(减小) 5。

NBTI的危害尤为阴险,它会逐渐侵蚀掉-5V驱动所提供的安全裕量,使器件在寿命后期($V_{th}$降低后)更容易发生寄生开通。研究指出,-5V的负压恰恰会加速NBTI效应 。

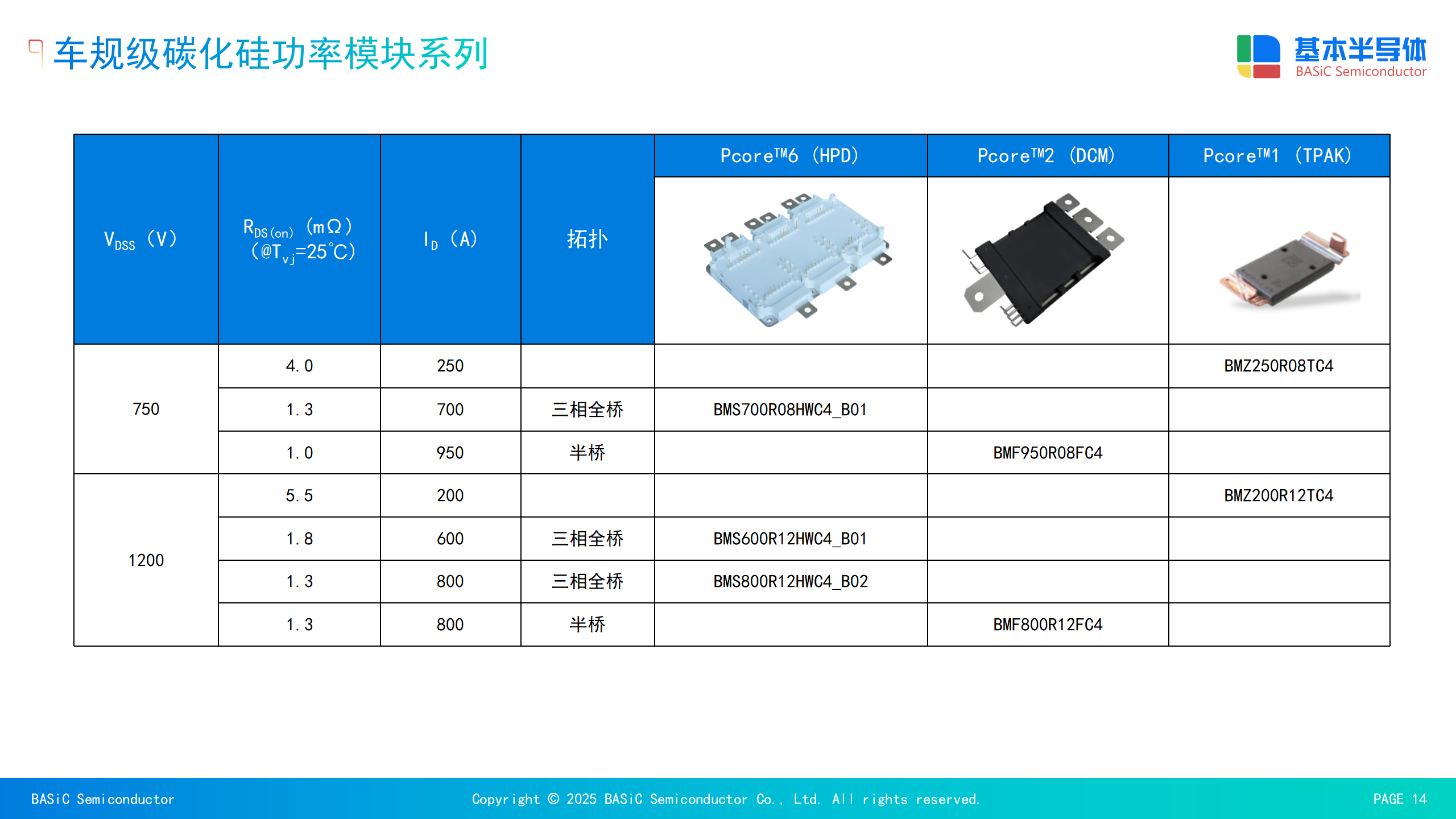

因此,一个制造商敢于推荐-5V/+18V的驱动范围(如所附资料中的国产厂商BASiC Semiconductor在其产品B3M010C075Z、B3M013C120Z和B3M020140ZL的数据表中明确推荐$V_{GSop}$为-5/18 V),实质上是在声明其拥有高度成熟的制造工艺。这表明该制造商有能力精确控制SiC/SiO2界面的缺陷密度,使其栅极氧化层能够*同时*承受PBTI和NBTI的双重长期压力,而$V_{th}$漂移仍保持在可控范围内。这种栅氧可靠性,是区分“实验室级”器件与“工业/车规级”器件的根本标志,也是检验国产SiC厂商技术能力的核心标准 。

第1部分:-5V驱动电压的意义:保障系统鲁棒性的工程必要性

在SiC MOSFET的应用中,尤其是在高频、高压的硬开关拓扑(如半桥、全桥)中,采用-5V的负电压($V_{GS(off)}$)进行关断,是确保系统在高压和高动态应力下可靠运行的关键设计决策。

1.1 0V关断的固有风险:低阈值电压($V_{GS(th)}$)的挑战

SiC MOSFET与传统的硅(Si)器件在物理特性上存在显著差异。其中最突出的一点是其栅极阈值电压$V_{GS(th)}$相对较低。在某些情况下,SiC MOSFET的$V_{GS(th)}$在最坏工况下(例如高温)可能低至1V或2V 。

如果采用传统Si MOSFET的0V关断策略,栅极驱动器仅将$V_{GS}$拉至0V。这意味着系统抵抗栅极噪声的“噪声裕量”(Noise Margin)仅为$V_{GS(th)}$本身(即1V至2V)。在功率变换器这种充满电磁噪声的环境中,如此低的噪声裕量是极其危险的。

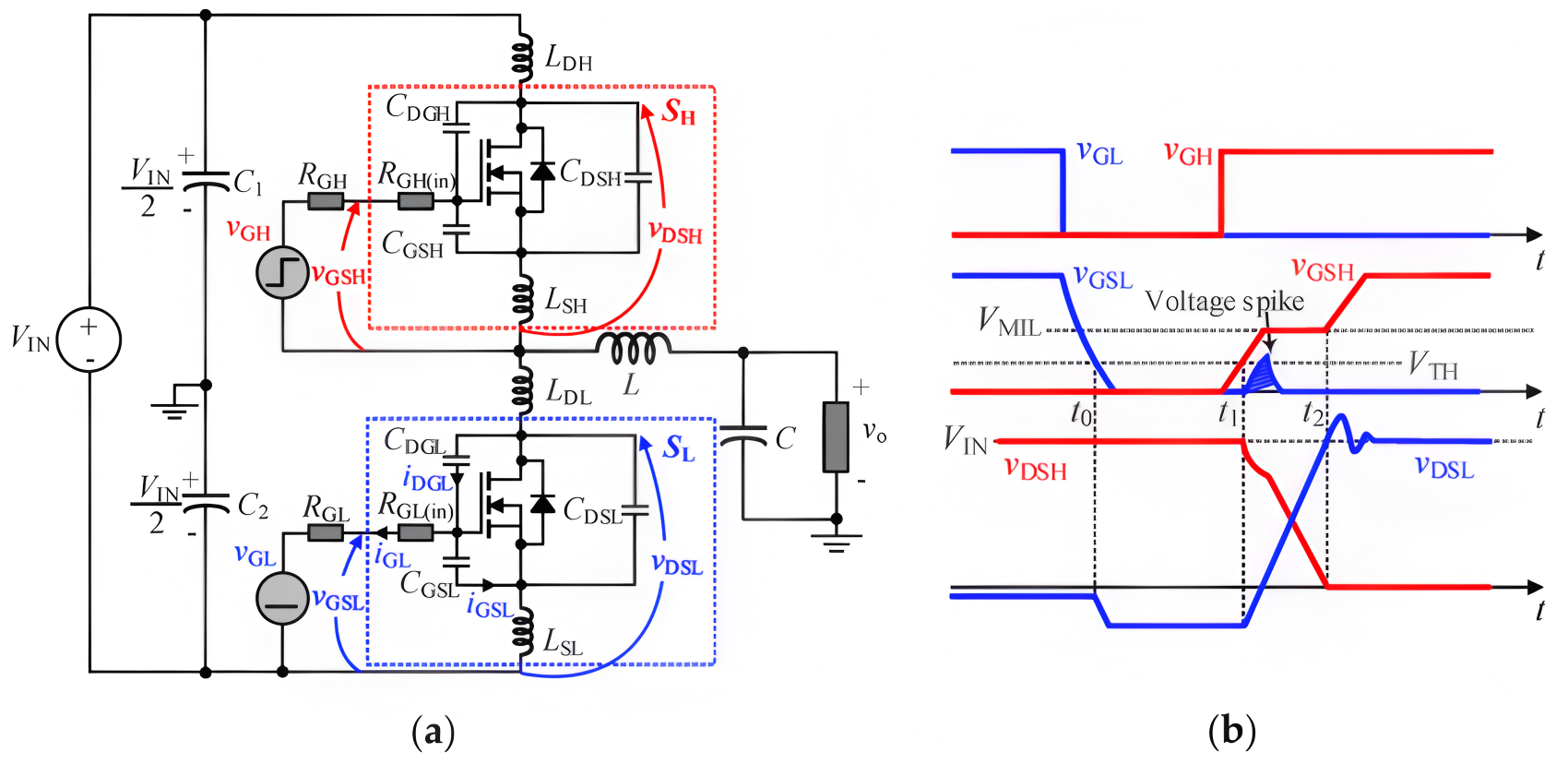

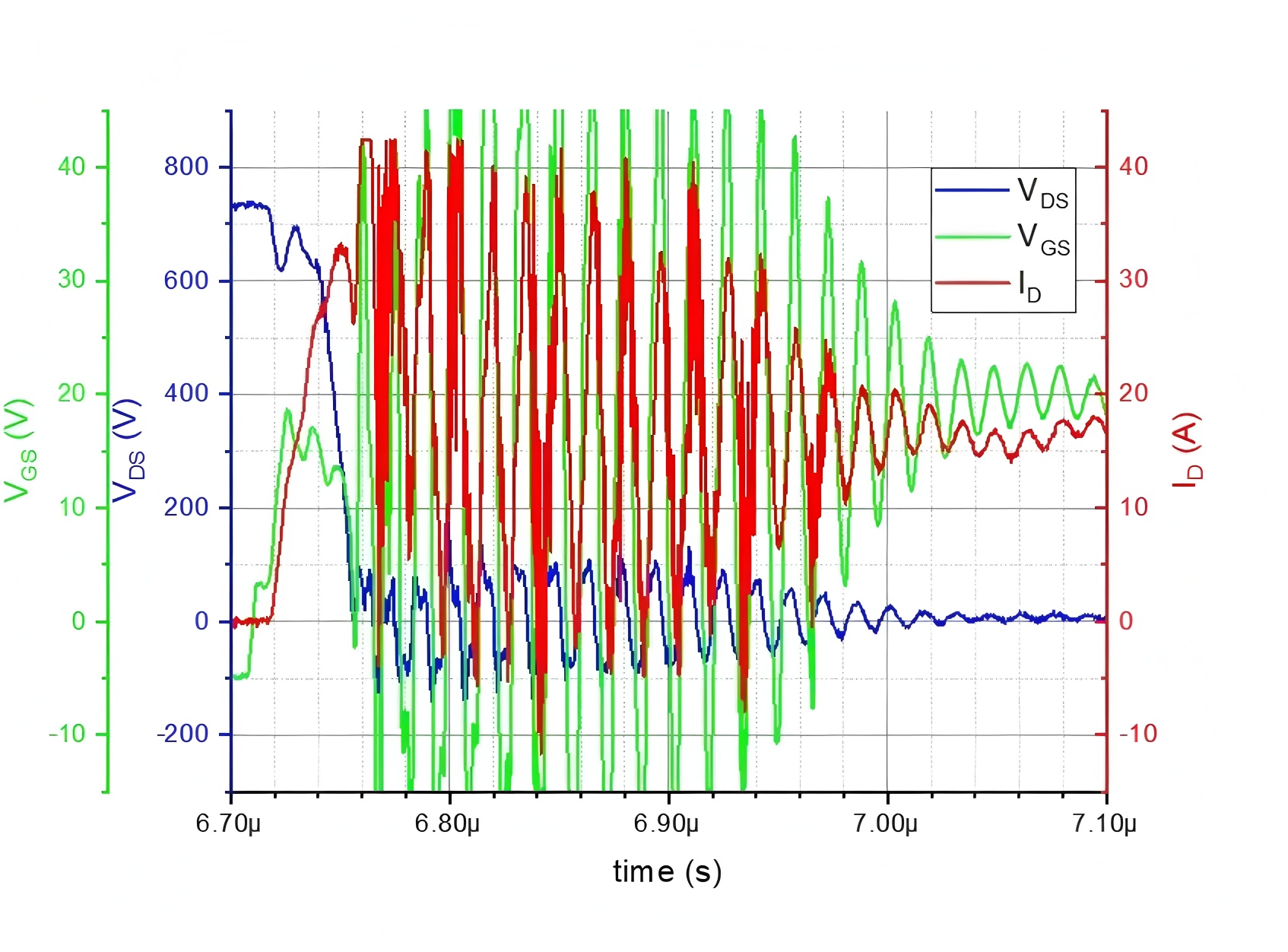

1.2 威胁一:高$dv/dt$与“米勒”寄生开通(Crosstalk)

在半桥拓扑中,当下管(LS)MOSFET快速开通时,其漏源电压$V_{DS}$迅速下降;与此同时,处于关断状态的上管(HS)MOSFET的$V_{DS}$会经历一个极高压摆率($dv/dt$)的上升($dv/dt$可高达100 V/ns或更高)。

这一剧烈的$dv/dt$变化会通过HS器件的米勒电容($C_{gd}$,即数据表中的$C_{rss}$)感应出一个瞬态电流(米勒电流 $I_{miller} = C_{gd} times dv/dt$)2。该电流从漏极流向栅极,然后通过外部栅极关断电阻($R_{G(off)}$)流向地。这在$R_{G(off)}$上产生了一个瞬时的正向电压尖峰:

$$V_{spike} = I_{miller} times R_{G(off)}$$

如果这个$V_{spike}$的峰值超过了该器件的$V_{GS(th)}$,这个本应处于“关断”状态的HS器件将会被错误地“寄生开通”(Parasitic Turn-on)。这种现象被称为“串扰”(Crosstalk)。上管和下管同时导通(哪怕是瞬时的)将导致桥臂直通(Shoot-through),这是功率系统中的灾难性故障。

-5V解决方案:

采用-5V的负压关断,极大地提升了噪声裕量。例如,若$V_{GS(th)} = 2.5V$,0V关断的裕量仅为2.5V。而采用-5V关断, $V_{spike}$必须克服从-5V到+2.5V的全部电压,即裕量提升至7.5V。这为抵抗米勒效应提供了坚实的安全保障 。

1.3 威胁二:高$di/dt$与共源电感($L_s$)的干扰

另一个寄生开通机制源于极高的电流变化率($di/dt$)和封装的寄生电感。在开关过程中,主电流路径上的$di/dt$非常高。如果栅极驱动回路与主功率回路共享了一段寄生电感(即“共源电感”$L_s$),问题就会出现 。

当器件关断时,漏极电流$I_D$急剧下降($di/dt$为负)。根据电感方程$V = -L times di/dt$,这个快速变化的电流会在$L_s$上感应出一个电压。这个电压会叠加到栅源电压$V_{GS}$上,形成负反馈,阻碍器件关断 。

更危险的是,在桥式拓扑中,一个器件开通时(高$di/dt$)在环路杂散电感上引起的电压振荡,同样会耦合到另一个处于关断状态的器件的栅极上。

-5V解决方案:

一个采用-5V驱动的栅极驱动器,通常被设计为具有极低的输出阻抗(Sink Impedance)。它能以“强力钳位”的方式将栅极“钉死”在-5V电位。这使得$di/dt$感应的噪声电压更难在栅极上形成足够的尖峰,从而有效地抑制了由$di/dt$引起的栅极振荡和寄生开通。

1.4 确保栅极完全放电及优化体二极管性能

从器件物理角度来看,SiC MOSFET的栅极电荷($Q_G$)在$V_{GS} = 0V$时并未完全释放 。需要施加负压才能将沟道中的载流子完全耗尽,确保器件真正、快速地关断。

此外,在实际应用中,MOSFET的体二极管(Body Diode)经常在死区时间(Dead Time)内续流。数据表显示,体二极管的关键特性,如正向压降($V_{SD}$)、反向恢复电荷($Q_{rr}$)和反向恢复时间($t_{rr}$),其标准测试条件都是在$V_{GS} = -5V$下进行的。

例如,在所附的BASIC Semiconductor数据表中:

B3M010C075Z的体二极管特性($V_{SD}$, $t_{rr}$, $Q_{rr}$)均在$V_{GS}=-5V$条件下测试 。

B3M013C120Z的体二极管特性同样在$V_{GS}=-5V$条件下测试 。

B3M020140ZL的体二极管特性亦在$V_{GS}=-5V$条件下测试 6

施加-5V负压有助于改善体二极管的反向恢复性能,并使器件在第三象限的工作特性更加稳定。

第2部分:+18V驱动电压的依据:最大化器件性能与效率

如果说-5V关断是为了“安全”和“鲁棒”,那么+18V开通($V_{GS(on)}$)则是为了追求“性能”和“效率”。

2.1 克服SiC MOSFET的低跨导($g_m$)特性

跨导($g_m$)衡量了栅极电压$V_{GS}$对漏极电流$I_D$的控制能力。与Si MOSFET相比,SiC MOSFET(尤其是早期和平面栅工艺)的跨导相对较低 。

低跨导意味着需要施加更高的栅极驱动电压,才能使沟道充分“开通”(enhance),即达到器件设计所能提供的最低导通电阻($R_{DS(on)}$)。

2.2 低栅压驱动的性能惩罚

使用传统的+15V(甚至+12V)来驱动SiC MOSFET,会导致器件处于“未充分开通”状态,其$R_{DS(on)}$将远高于其标称值。

一份来自onsemi的分析(TND6237)提供了极具说服力的数据:对于某SiC MOSFET,在$I_D = 20A$时 :

当 $V_{GS} = 20V$ 时,$R_{DS(on)} = 188~mOmega$。

当 $V_{GS} = 12V$ 时,$R_{DS(on)} = 438~mOmega$。

数据显示,采用+12V驱动时的导通电阻是+20V驱动时的2.3倍。这意味着在相同电流下,导通损耗($P_{loss} = I_D^2 times R_{DS(on)}$)也将高出一倍以上。这种低效运行不仅浪费能量,更会导致器件严重发热,带来“热应力甚至可能的失效” 。

2.3 +18V:行业公认的性能基准点

虽然+15V是传统Si-IGBT的驱动标准 ,但它显然不适用于追求极致性能的SiC MOSFET。行业逐渐收敛于+18V至+20V的范围,将其作为SiC MOSFET的推荐开通电压 。

+18V成为了一个平衡点:它既能确保器件进入深度饱和区,获得接近最小值的$R_{DS(on)}$,又与栅极氧化层的极限电压(通常为+22V或+25V)保持了一定的安全裕量。

所附的国产厂商数据表(6)也印证了这一行业标准。它们都在$V_{GS}=18V$的条件下测量并标定了其产品的典型$R_{DS(on)}$值:

B3M010C075Z:$R_{DS(on).typ} = 10~mOmega @ V_{GS}=18V$ 。

B3M013C120Z:$R_{DS(on).typ} = 13.5~mOmega @ V_{GS}=18V$ 。

B3M020140ZL:$R_{DS(on).typ} = 20~mOmega @ V_{GS}=18V$ 。

深圳市倾佳电子有限公司(简称“倾佳电子”)是聚焦新能源与电力电子变革的核心推动者:

倾佳电子成立于2018年,总部位于深圳福田区,定位于功率半导体与新能源汽车连接器的专业分销商,业务聚焦三大方向:

新能源:覆盖光伏、储能、充电基础设施;

交通电动化:服务新能源汽车三电系统(电控、电池、电机)及高压平台升级;

数字化转型:支持AI算力电源、数据中心等新型电力电子应用。

公司以“推动国产SiC替代进口、加速能源低碳转型”为使命,响应国家“双碳”政策(碳达峰、碳中和),致力于降低电力电子系统能耗。

需求SiC碳化硅MOSFET单管及功率模块,配套驱动板及驱动IC,请添加倾佳电子杨茜微芯(壹叁贰 陆陆陆陆 叁叁壹叁)

第3部分:-5V/+18V:检验制造商技术能力的“双重压力”基准

为何-5V/+18V这一特定组合,会成为检验(尤其是国产)厂商技术能力的“主流标准”?

答案在于,这个电压范围不仅仅是应用上的“最优解”,它同时构成了对SiC MOSFET制造工艺中最核心、最困难环节的**“双重压力测试”——这个环节就是栅极氧化层(Gate Oxide)的长期可靠性**。

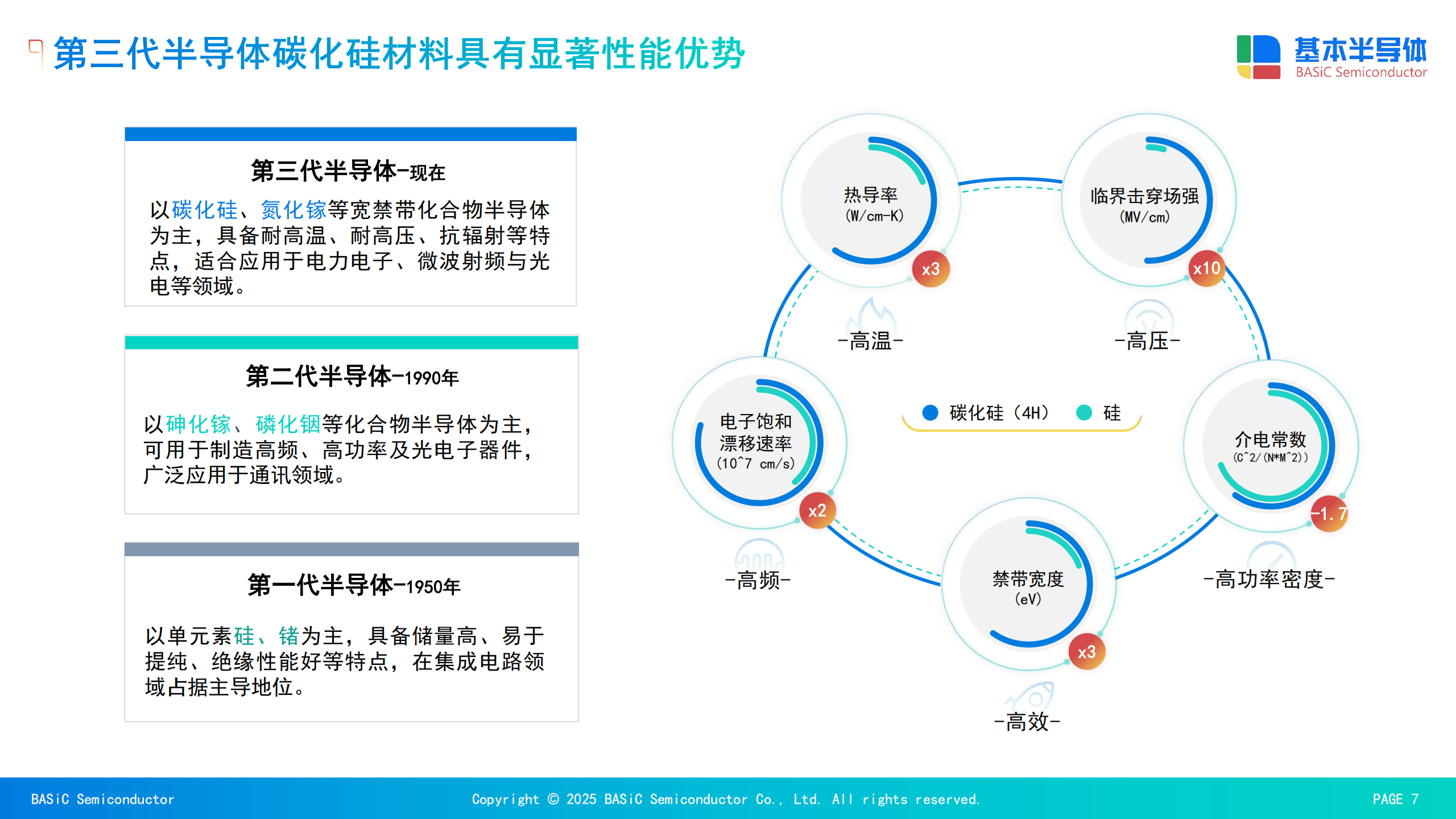

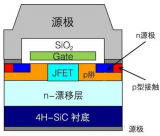

3.1 SiC MOSFET的核心挑战:栅极氧化层与BTI

SiC MOSFET的“阿喀琉斯之踵”(Achilles' heel)不在于SiC材料本身,而在于SiC与二氧化硅(SiO2)绝缘层之间的界面 5。相比成熟的Si/SiO2界面,SiC/SiO2界面在氧化过程中更容易产生缺陷、界面陷阱和固定电荷 。

这些缺陷是导致SiC MOSFET长期可靠性问题的根源,即偏压温度不稳定性(Bias Temperature Instability, BTI)。BTI效应是指器件在栅极长时间施加电压(偏压)和高温下,其阈值电压$V_{th}$会发生“漂移”(Drift)。

BTI的严重程度,以及$V_{th}$漂移的可控性,是直接衡量制造商制造工艺(如氧化、氮化、退火工艺)成熟度的指标。

3.2 压力测试 #1:+18V与正偏压温度不稳定性(PBTI)

机理:当栅极长时间承受高温、高正偏压(如+18V)时,沟道中的电子会被能量“泵入”并“陷落”在SiC/SiO2界面或氧化层内部的缺陷中 。

后果:这些被陷落的负电荷(电子)会屏蔽栅极的正电场。为了在栅极下感应出同样的沟道,就需要施加更高的栅压。其宏观表现为**$V_{th}$随时间正向漂移(增大)** 。

危害:在实际应用中,驱动器仍然只提供+18V。但如果器件的$V_{th}$从2.5V漂移到了4.5V,其有效过驱动电压($V_{GS} - V_{th}$)就减小了。如第2部分所述,更低的过驱动电压意味着**更高的$R_{DS(on)}$** 。这导致器件在寿命后期效率下降、发热增加,进一步加速BTI漂移,形成恶性循环,甚至可能导致热失控 。

基准检验:制造商推荐+18V驱动,等同于承诺其栅氧工艺足够“纯净”,能够承受PBTI的长期压力,确保$R_{DS(on)}$在全寿命周期内的稳定性。

3.3 压力测试 #2:-5V与负偏压温度不稳定性(NBTI)

机理:当栅极长时间承受高温、负偏压(如-5V)时(例如器件处于关断状态时),界面附近会发生空穴陷获,或产生新的界面态 。

后果:这些陷落的正电荷(空穴)或界面态使得栅极更容易“吸引”电子形成反型层(沟道)。其宏观表现为**$V_{th}$随时间负向漂移(减小)**。

危害(核心洞察):NBTI带来的$V_{th}$负漂比PBTI更危险。它会直接侵蚀掉系统设计师依赖-5V所建立的安全裕量。

设想一个场景:一个新器件$V_{th}=2.5V$,采用-5V关断,拥有7.5V的噪声裕量。经过长期NBTI(由-5V本身加速)后 ,其$V_{th}$漂移至1.0V。此时,其噪声裕量已降至 $1.0V - (-5V) = 6.0V$。 $V_{th}$越低,器件越接近“常开型”(D-mode),其抵抗米勒寄生开通的能力被大幅削弱,系统在寿命后期将面临极高的桥臂直通风险。

研究表明,-3V的负压足以实现电子的“去陷获”,而-5V则会显著增加NBTI效应,尤其是在高温下 。

3.4 综合论证:-5V/+18V,成熟工艺的“试金石”

-5V/+18V的组合之所以成为检验技术能力的标准,原因在于它是一个“双重夹击”的压力测试:

它要求栅氧工艺必须同时抵抗两种相反的失效机理:既要抵抗+18V带来的PBTI($V_{th}$正漂),又要抵抗-5V带来的NBTI($V_{th}$负漂)。

它暴露了工艺控制的难度:在制造中,优化PBTI的工艺手段(如特定的氮化处理)有时可能会恶化NBTI,反之亦然。有能力将两种漂移都控制在极小范围(例如车规级要求的$Delta V_{th} < pm 1V$)内的制造商,才真正掌握了SiC栅氧的核心技术。

因此,当一个国产SiC制造商(如BASIC Semiconductor)在其数据手册中(6),不仅推荐$V_{GSop}$为-5/18 V,并且在表征关键参数(如$Q_G$, $E_{on}$, $E_{off}$)时 ,也明确使用-5V/+18V的测试条件时,这传递了一个强烈的市场信号:

该制造商自信其SiC/SiO2界面工艺已经成熟,其栅极氧化层的可靠性足以承受来自应用端(-5V的鲁棒性需求)和性能端(+18V的效率需求)的双重长期压力。这标志着其产品具备了与国际头部厂商(如Wolfspeed, Infineon, Rohm等)在同一可靠性基准上竞争的能力 。

第4部分:表格分析与数据佐证

为了直观地总结上述分析,以下表格基于所提供的研究资料,对-5V/+18V标准进行了数据确认和技术权衡。

表1:国产厂商数据表对-5V/+18V基准的采用佐证

该表证实了用户查询的前提,即-5V/+18V已成为国产厂商在产品表征和推荐中采用的标准。

| B3M010C075Z 6 | -5/18 V | -5/+18 V | -5/18 V |

| B3M013C120Z 6 | -5/18 V | -5/+18 V | -5/18 V |

| B3M020140ZL 6 | -5/18 V | -5/+18 V | -5/18 V |

| 器件型号 (厂商: BASIC Semi) | 推荐栅极电压 (VGSop) | 总栅极电荷 (QG) 测试条件 (VGS) | 开关能量 (Eon/Eoff) 测试条件 (VGS) |

|---|

表2:SiC MOSFET栅极驱动电压的技术权衡分析

该表总结了不同驱动电压选择在性能、鲁棒性和可靠性三个维度上的利弊,清晰地揭示了-5V/+18V为何是“最优”且“最严苛”的组合。

| 0V (关断) | (不适用) | 极差(噪声裕量极低,易寄生开通) 1 | NBTI 风险低,但被鲁棒性问题一票否决 |

| -5V (关断) | (不适用) | 优秀(高噪声裕量,强抗干扰) 2 | 高 NBTI 风险($V_{th}$ 负向漂移) 5 |

| +15V (开通) | 差(高 $R_{DS(on)}$,导通损耗高,效率低) 1 | (不适用) | PBTI 风险较低 |

| +18V (开通) | 优秀(低 $R_{DS(on)}$,导通损耗低,效率高) 1 | (不适用) | 高 PBTI 风险($V_{th}$ 正向漂移) 5 |

| 栅极驱动电压 | 性能影响 (导通电阻 RDS(on)) | 鲁棒性影响 (抗干扰/噪声裕量) | 长期可靠性风险 (BTI) |

|---|

表格分析结论:

表2清晰地显示,行业推荐的-5V/+18V标准,是一个主动选择的组合。它在“性能”维度(+18V)和“鲁棒性”维度(-5V)上均选择了“优秀”方案,但其代价是同时承担了两个维度上“高”的长期可靠性风险(NBTI 和 PBTI)。

第5部分:结论与战略意义

5.1 综合结论

本报告的分析得出结论,-5V/+18V驱动标准在SiC MOSFET领域具有双重且紧密关联的意义:

应用层面的最优解:-5V是应对高$dv/dt$、高$di/dt$和低$V_{th}$带来的寄生开通风险所必需的**鲁棒性保障** [;+18V是克服低$g_m$、实现最低$R_{DS(on)}$所必需的性能保障。

制造层面的试金石:这一组合构成了对SiC/SiO2栅氧界面最严苛的可靠性压力测试。它同时激发了PBTI(来自+18V)和NBTI(来自-5V)两种主要的$V_{th}$漂移机制 。

因此,一个SiC MOSFET制造商(无论是国际巨头还是国产厂商)能否在数据表上自信地推荐-5V/+18V作为标准工作条件,并提供在这些条件下表征的参数(如6所示),这已成为行业内用以评判其栅极氧化层工艺成熟度和长期可靠性控制能力的核心基准。

5.2 对国产SiC厂商的战略意义

随着新能源汽车、光伏储能、工业电源等市场对SiC器件的需求爆发,国产SiC厂商面临着巨大的机遇和挑战。采用-5V/+18V这一国际主流标准,对它们而言具有高度的战略意义:

对标国际,声明能力:这表明国产厂商不再局限于“参数达标”,而是开始在“长期可靠性”这一核心战场上与国际厂商正面竞争。这是其产品从“可用”走向“可靠”和“高端”的必经之路。

获取信任,进入高端市场:尤其是在汽车和高可靠性工业领域,客户对器件的长期可靠性(如$V_{th}$稳定性)的关注度甚至高于极限参数。能够提供符合此基准并辅以详尽BTI测试数据的厂商,将更快获得下游头部客户的信任。

5.3 对应用工程师的评估建议

对于负责评估和选用SiC MOSFET的系统设计师和元器件工程师,本报告提出以下建议:

“信任,但要核实”:数据表(如6)是制造商的“声明”或“承诺”。在评估任何厂商(尤其是新晋厂商)的SiC MOSFET时,不能仅满足于其推荐了-5V/+18V的驱动。

索取BTI数据:评估的“金标准”是向制造商索取详尽的长期可靠性数据。

关键评估点:要求制造商提供在最大结温下(例如$T_j = 175^{circ}C$)、1000小时以上的BTI压力测试报告,该报告必须同时包含:

PBTI测试:在$V_{GS} = +18V$ (或 $V_{GSmax}$) 压力下的$V_{th}$漂移曲线。

NBTI测试:在$V_{GS} = -5V$ (或 $V_{GSmin}$) 压力下的$V_{th}$漂移曲线。

一个工艺成熟的制造商将能够提供这些数据,并证明其$V_{th}$漂移(无论是正漂还是负漂)均被严格控制在极小的范围内。这些数据,才是检验一个SiC MOSFET厂商“技术能力”的真正主流标准。

审核编辑 黄宇

-

驱动电压

+关注

关注

0文章

100浏览量

14004 -

碳化硅MOSFET

+关注

关注

0文章

57浏览量

4949

发布评论请先 登录

倾佳代理的基本半导体碳化硅MOSFET分立器件产品力及应用深度分析

倾佳电子1400V碳化硅(SiC)MOSFET赋能新一代电力电子系统

倾佳电子碳化硅MOSFET驱动电压解析:-5V的必要性及-5V/+18V作为技术能力检验标准的深层原因

倾佳电子碳化硅MOSFET驱动电压解析:-5V的必要性及-5V/+18V作为技术能力检验标准的深层原因

评论