ADC12QJ1600-SEP是一款四通道、12位、1.6GSPS模数转换器(ADC)。低功耗、高采样率和 12 位分辨率使该器件适用于各种覆盖物-香奈儿通信系统。

6 GHz 的全功率输入带宽 (-3 dB) 支持对 L 波段和 S 波段进行直接射频采样。

*附件:adc12qj1600-sep.pdf

包括许多时钟功能以放宽系统硬件要求,例如带有集成压控振荡器 (VCO) 的内部锁相环 (PLL) 以生成采样时钟。提供四个时钟输出,用于对FPGA或ASIC的逻辑和SerDes进行时钟处理。为脉冲系统提供时间戳输入和输出。

JESD204C串行接口通过减少印刷电路板 (PCB) 布线量来减小系统尺寸。接口模式支持 2 至 8 通道(双通道和四通道设备)或 1 至 4 通道(用于单通道设备),SerDes 波特率高达 17.16Gbps,可为每个应用提供最佳配置。

特性

- 辐射耐受性:

- 空间增强塑料(太空 EP):

- 符合 ASTM E595 释气规范

- 供应商项目图纸 (VID) V62/22610

- 温度范围:–55°C 至 125°C

- 一个制造、组装和测试站点

- 晶圆批次可追溯性

- 延长产品生命周期

- 扩展产品变更通知

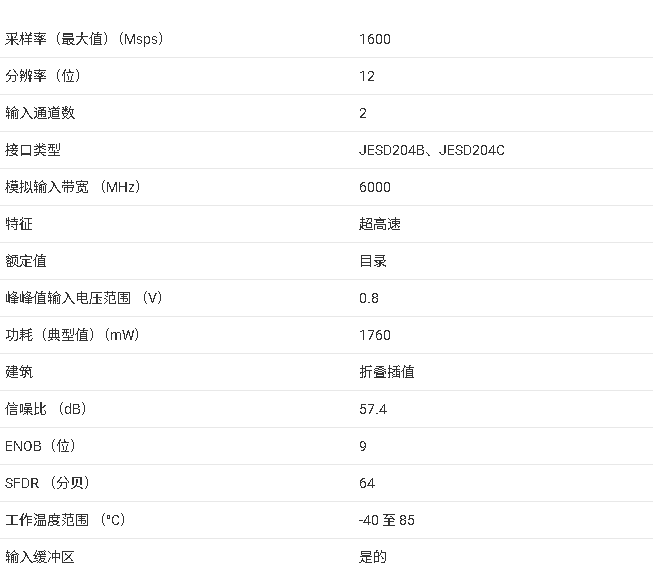

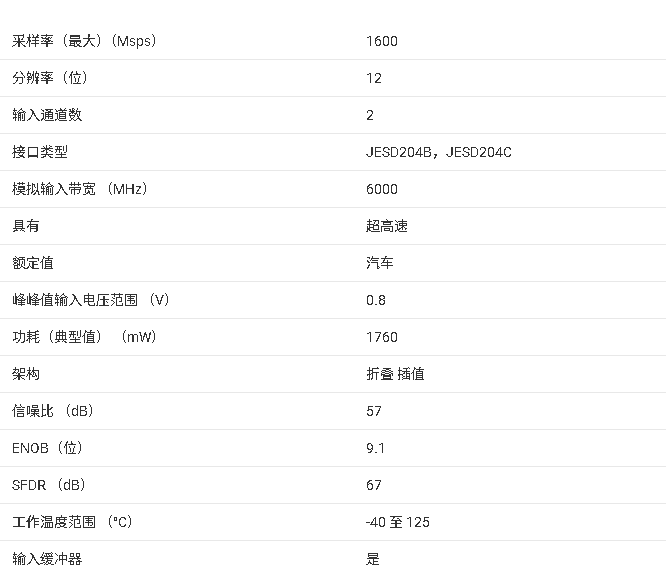

- ADC内核:

- 分辨率:12位

- 最大采样率:1.6GSPS

- 非交错架构

- 内部抖动可减少高阶谐波

- 性能规格 (–1dBFS):

- 信噪比 (100 MHz):57.4dBFS

- ENOB (100 MHz):9.1 位

- SFDR (100 MHz):64dBc

- 本底噪声 (–20 BFS):–147dBFS

- 满量程输入电压:800mVPP-DIFF

- 全功率输入带宽:6GHz

- JESD204C 串行数据接口:

- 总共支持 2 到 8 条 SerDes 通道

- 最特率:17.16Gbps

- 64B/66B 和 8B/10B 编码模式

- 子类 1 对确定性延迟的支持

- 与JESD204B接收器兼容

- 可选的内部采样时钟生成

- 内部 PLL 和 VCO (7.2 – 8.2GHz)

- SYSREF 窗口简化同步

- 四个时钟输出简化了系统时钟

- FPGA或相邻ADC的参考时钟

- SerDes 收发器的参考时钟

- 脉冲系统的时间戳输入和输出

- 功耗(1GSPS):1.9W

- 电源:1.1V、1.9V

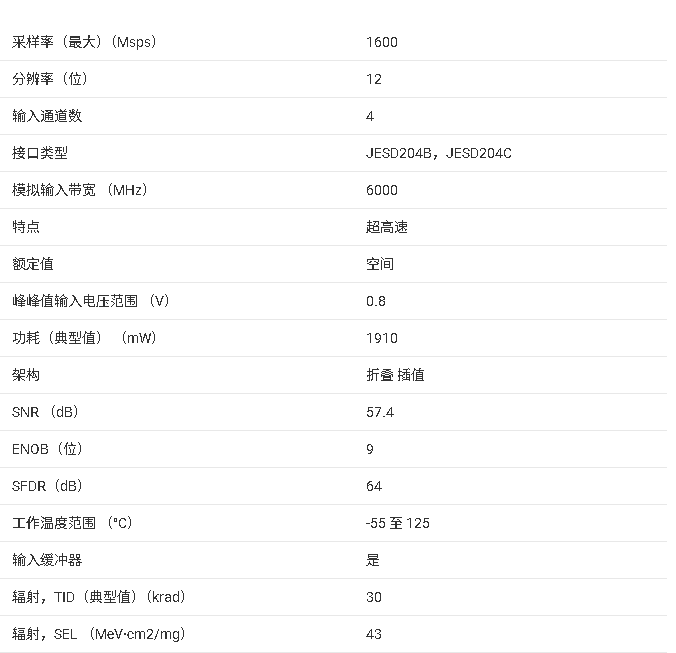

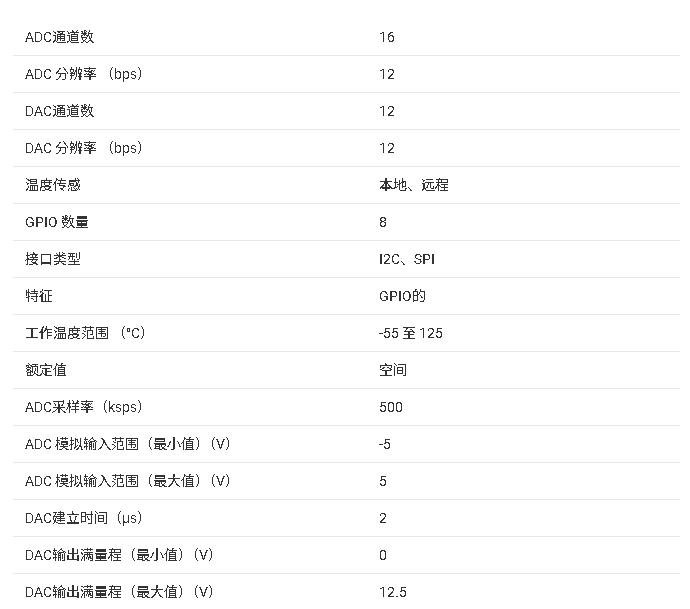

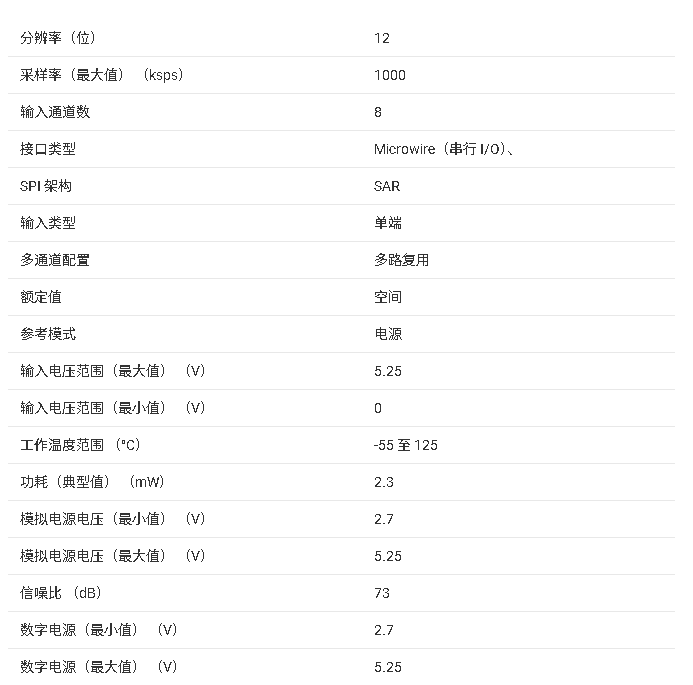

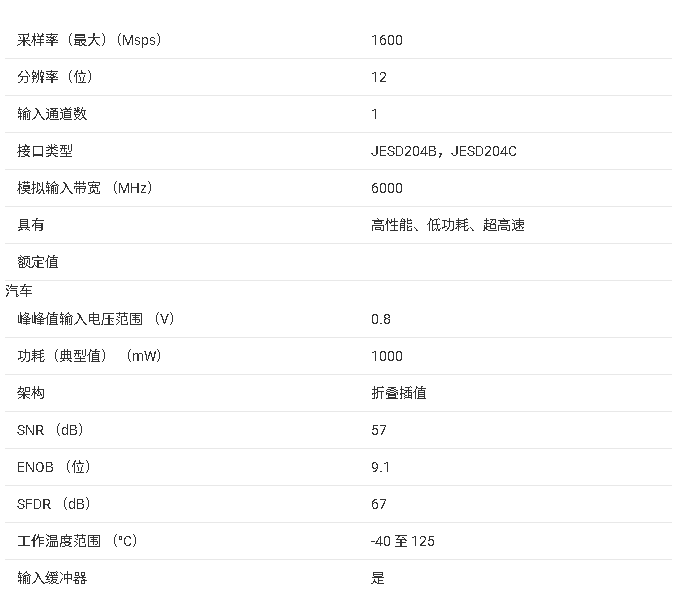

参数

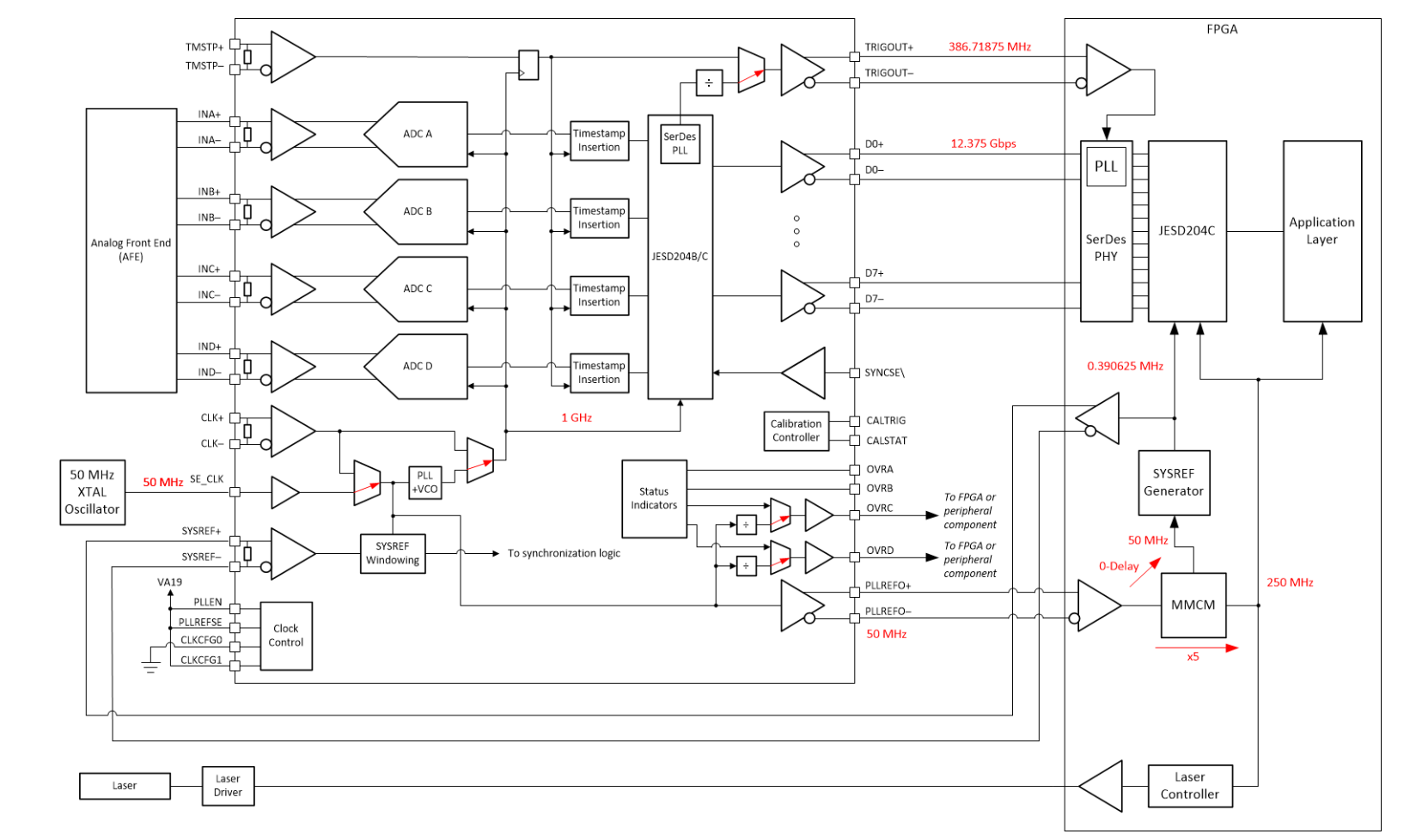

方框图

一、产品概述

ADC12QJ1600-SEP 是德州仪器(TI)推出的四通道 12 位 1.6GSPS 模数转换器(ADC) ,专为高可靠性、高频率场景设计,符合严苛的辐射耐受性要求,适配电子战(SIGINT、ELINT)、卫星通信(SATCOM)等关键领域。器件集成 JESD204C 高速串行接口,支持宽频带直接射频采样,兼具低功耗与高性能,采用 10mm×10mm 144 引脚 FCBGA 封装,工作温度范围覆盖 - 55°C 至 125°C,满足极端环境下的稳定运行需求。

二、核心特性

(一)辐射耐受性与可靠性

针对太空及高辐射环境优化,核心辐射指标如下:

- 总电离剂量(TID) :30krad(Si),可承受长期辐射暴露;

- 单粒子锁定(SEL) :43 MeV-cm²/mg,避免高能粒子导致的器件锁定;

- 单粒子翻转(SEU) :寄存器免疫设计,防止数据因粒子撞击异常;

- 材料与合规性 :采用太空增强型塑料封装(Space EP),符合 ASTM E595 释气规范,确保真空环境下无有害挥发物;

- 生命周期保障 :单一制造 / 组装 / 测试站点、晶圆批次可追溯,提供延长产品生命周期及变更通知服务。

(二)ADC 核心性能

- 精度与速率

- 分辨率:12 位,无失码;

- 最高采样率:1.6GSPS,非交错架构(避免交错失真);

- 线性度:积分非线性(INL)±1 LSB,微分非线性(DNL)±1 LSB,确保转换精度;

- 内置抖动功能:降低高次谐波,优化动态性能。

- 动态性能(-1dBFS 输入,100MHz 信号)

- 信噪比(SNR):57.4dBFS;

- 有效位数(ENOB):9.1 位;

- 无杂散动态范围(SFDR):64dBc;

- 噪声基底(-20dBFS):-147dBFS/Hz;

- 全功率输入带宽:6GHz,支持 L 波段(1-2GHz)、S 波段(2-4GHz)直接射频采样,无需额外下变频电路。

- 输入与输出特性

- 全量程输入电压:800mVPP-DIFF(差分),支持 480mVPP-DIFF 至 1040mVPP-DIFF 可调;

- 输入阻抗:内部 50Ω 差分端接,适配射频信号传输;

- 输出接口:JESD204C 串行接口,支持 2-8 路 SerDes 通道,最高波特率 17.16Gbps,减少 PCB 布线复杂度。

(三)时钟与同步功能

- 灵活时钟生成

- 内置 PLL 与 VCO(7.2-8.2GHz):支持从低频率参考时钟(50-500MHz)生成高速采样时钟,避免外部高频时钟布线干扰;

- 时钟输入选项:支持差分时钟(CLK±)或单端时钟(SE_CLK),差分输入内置 100Ω 端接;

- 多时钟输出:4 路时钟输出(PLLREFO±、TRIGOUT±、ORC、ORD),可作为 FPGA / 相邻 ADC 的参考时钟,简化系统时钟树设计。

- 同步与确定性延迟

- SYSREF 窗口化 :自动检测 SYSREF 与采样时钟的相位关系,无需严格外部时序约束,轻松实现多器件同步;

- JESD204C 子类 1 支持 :通过 SYSREF 复位本地多帧时钟(LMFC)/ 本地扩展多块时钟(LEMC),实现确定性延迟,满足多 ADC 协同场景;

- 时间戳功能:TMSTP± 差分输入标记特定采样点,TRIGOUT± 输出可重定时触发信号,适配脉冲系统同步需求。

(四)低功耗与工作模式

- 功耗优化 :1GSPS 采样率下典型功耗 1.9W,支持低功耗模式(采样率≤1GSPS 时启用),通过寄存器配置可进一步降低功耗(如关闭闲置通道、优化校准周期);

- 双工作模式 :

- 高性能模式:全采样率下保持最佳动态性能,适配高频率、高精度需求;

- 低功耗模式:牺牲部分动态性能换取功耗降低,适合对功耗敏感的场景。

三、器件信息与电气规格

(一)基本参数

| 参数 | 规格 | 单位 |

|---|---|---|

| 分辨率 | 12 | 位 |

| 最高采样率 | 1.6 | GSPS |

| 全功率输入带宽 | 6 | GHz |

| 输入电压范围(差分) | 480-1040(可调) | mVPP-DIFF |

| 工作电源 | VA11(1.1V)、VA19(1.9V)、VPLL19(1.9V)等 | V |

| 静态电流(1.1V 电源) | 典型值 367-760(依模式而定) | mA |

| 封装 | 144 引脚 FCBGA | 10mm×10mm |

(二)热特性

采用底部带散热焊盘的 FCBGA 封装,需将焊盘连接 AGND 优化散热,关键热阻参数如下:

| 热阻参数 | 数值 | 单位 |

|---|---|---|

| 结到环境(RθJA) | 20.9 | °C/W |

| 结到板(RθJB) | 6.54 | °C/W |

| 结到底部外壳(RθJC (bot)) | 8.7 | °C/W |

| 结到顶部外壳(RθJC (top)) | 1.0 | °C/W |

(三)ESD 防护

| ESD 测试标准 | 数值 | 单位 |

|---|---|---|

| 人体放电模型(HBM,AEC Q100-002) | 4000 | V |

| 带电器件模型(CDM,AEC Q100-011) | 750 | V |

四、功能模块详解

(一)模拟输入与校准

- 模拟输入电路

- 校准功能支持前景校准(Foreground)与背景校准(Background)两种模式,确保全温度范围性能稳定:

- 前景校准 :需暂停 ADC 采样,适合上电初始化或环境剧变后,校准线性度、增益与偏移;

- 背景校准 :通过冗余 ADC 核心(共 6 个核心,轮换校准)实现无中断校准,不影响正常数据输出;

- 低功耗背景校准(LPBG) :校准间隙关闭冗余核心,降低平均功耗,可通过 LP_SLEEP_DLY 调节休眠时长(最长 1.099×10¹² 个时钟周期);

- 偏移校准 :独立校准输入缓冲偏移,支持以中间码或冗余核心为参考,适配 AC/DC 耦合场景。

(二)JESD204C 串行接口

- 接口特性

- 编码模式:支持 64B/66B(高效率,低开销)与 8B/10B(兼容 JESD204B 接收器);

- 通道数:2-8 路 SerDes 通道(四通道模式),单通道模式支持 1-4 路,最高波特率 17.16Gbps;

- 确定性延迟:子类 1 支持,通过 SYSREF 同步 LMFC/LEMC,确保多器件延迟一致;

- 纠错与检错:支持 CRC-12 循环冗余校验(检错)、FEC 前向纠错(纠 9 位突发错误),提升链路可靠性。

- 工作模式(JMODE 配置) 通过 JMODE 寄存器(0x201)选择 16 种预设模式,覆盖不同分辨率、通道数与编码组合,典型模式如下:| JMODE | 分辨率 | 编码 | 通道数 | 采样率范围 |

| ------- | ----------------- | --------- | -------- | ---------------- |

| 0 | 12 位 | 8B/10B | 8 | 500-1600MSPS |

| 7 | 8 位 | 64B/66B | 4 | 500-1600MSPS |

| 8 | 12 位 | 64B/66B | 4 | 500-1386.7MSPS |

| 15 | 12 位(双通道) | 64B/66B | 8 | 500-1600MSPS |

(三)时钟与同步子系统

- PLL 与时钟生成

- 转换器 PLL(C-PLL):输入 50-500MHz 参考时钟,通过 VCO(7.2-8.2GHz)生成 1.6GSPS 采样时钟,支持分频比配置(P、V、N 分频器);

- SerDes PLL(S-PLL):从采样时钟生成 SerDes 输出时钟,可通过 TRIGOUT± 输出分频时钟(16/32/64 分频),为 FPGA 收发器提供参考;

- 时钟噪声抑制:VA11Q 与 VCLK11 噪声抑制功能(开启后增加约 20mA 电流),降低采样抖动与参考时钟杂散。

- SYSREF 同步

- 输入特性:差分 SYSREF±,支持 AC/DC 耦合,内置 100Ω 端接(LVPECL 模式为 50Ω);

- 窗口化功能:通过 SYSREF_POS 寄存器读取 SYSREF 与时钟的相位位置,SYSREF_SEL 选择最优采样点,无需外部时序校准;

- 多器件同步:SYSREF 可复位多 ADC 的 LMFC/LEMC,实现多通道相位一致。

(四)测试与监控功能

- 测试模式支持多种内置测试模式,用于系统调试与性能验证:

- PRBS 模式:PRBS7/9/15/23/31 伪随机序列,验证链路完整性;

- 斜坡模式:递增 octet 流,检查数据传输顺序;

- 时钟模式:16 位交替 1/0 序列(0x00FF),测试时钟恢复;

- 专用字符模式:K28.5(逗号字符)、D21.5(交替 0/1)等,用于码组同步测试。

- 状态监控

五、电气规格详解

(一)直流特性(典型值,TJ=50°C)

| 参数 | 测试条件 | 典型值 | 单位 |

|---|---|---|---|

| 输入失调电压(V_OFF) | CAL_OS=1 | ±0.6 | mV |

| 失调漂移 | 前景校准,CAL_OS=1 | 0.25 | µV/°C |

| 满量程电压(V_FS) | 默认配置(FS_RANGE=0xA000) | 800 | mVPP-DIFF |

| 满量程漂移 | 默认配置,前景校准 | -0.0015 | %/°C |

| 输入电阻(R_IN) | 差分端接 | 100 | Ω |

| 输入电容(C_IN) | 单端 | 0.6 | pF |

(二)交流特性(100MHz 输入,-1dBFS)

| 参数 | 测试条件 | 典型值 | 单位 |

|---|---|---|---|

| 信噪比(SNR) | 1.6GSPS,高性能模式 | 57.4 | dBFS |

| 无杂散动态范围(SFDR) | 1.6GSPS,高性能模式 | 64 | dBc |

| 二次谐波失真(HD2) | 1.6GSPS | -64 | dBFS |

| 三次谐波失真(HD3) | 1.6GSPS | -67 | dBFS |

| 建立时间 | 10%FSR | 8 | µs |

(三)功耗特性(典型值,TJ=50°C)

| 工作模式 | 采样率 | 总功耗(P_DIS) | 关键电源电流(IVA19/IVA11/IVD11) |

|---|---|---|---|

| 四通道,高性能 | 1.6GSPS | 3.22W | 788mA/702mA/734mA |

| 四通道,低功耗 | 1.0GSPS | 1.91W | 558mA/394mA/384mA |

| 掉电模式(PD=1) | - | 0.14W | 47mA/30mA/17mA |

六、典型应用与设计指南

(一)核心应用场景

- 电子战射频信号采样

- 应用原理:利用 6GHz 全功率带宽,直接采样 L/S 波段射频信号(1-4GHz),无需混频器,简化接收链路;

- 关键配置:启用 JESD204C 64B/66B 编码(减少链路开销)、FEC 纠错(提升抗干扰能力),通过背景校准维持宽温下性能稳定。

- 卫星通信(SATCOM)多通道接收

- 应用原理:四通道同步采样,支持多波束信号并行处理,SYSREF 同步确保多通道相位一致;

- 关键配置:启用 C-PLL 生成 1.2GSPS 采样时钟,PLLREFO± 为 FPGA 提供参考时钟,时间戳功能标记突发信号。

- 雷达信号处理

- 应用原理:1.6GSPS 高采样率捕捉窄脉冲信号,内置抖动功能抑制谐波,SFDR=64dBc 确保小信号检测能力;

- 关键配置:低功耗背景校准(LPBG),平衡性能与功耗,过范围检测(OVR)避免强信号饱和。

(二)硬件设计指南

- 电源与布线

- 电源域分离:模拟地(AGND)、数字地(DGND)、PLL 地(PGND)、SE_CLK 地(SE_GND)单点连接至公共地平面,避免串扰;

- 去耦设计:VDD(1.1V)引脚并联 0.1μF 陶瓷电容(靠近引脚),VPLL19(1.9V)并联 1μF+0.1μF 电容,降低电源噪声;

- 阻抗控制:JESD204C SerDes 线路匹配 50Ω 阻抗,长度匹配误差 < 1mm,减少信号反射。

- 时钟与同步设计

- 时钟输入:CLK± 建议 AC 耦合,若使用 DC 耦合需设置 LVPECL 模式(DEVCLK_LVPECL_EN=1),确保共模电压合规;

- SYSREF 配置:优先启用 SYSREF 窗口化(SYSREF_ZOOM=1),通过 SYSREF_POS 选择中间采样点,最大化时序余量;

- 多器件同步:多 ADC 共享同一 SYSREF 与参考时钟,PLLREFO± 级联时需注意信号衰减,建议每级添加缓冲。

- 校准与初始化流程

- 上电后等待 INIT_DONE(0x270 寄存器)置 1,确保器件初始化完成;

- 配置 C-PLL:设置 CPLL_RESET=1,编程 P/V/N 分频器(0x3D/0x3E/0x3F),启用 VCO 校准(VCO_CAL_EN=1),等待 VCO_CAL_DONE=1;

- 配置校准模式:若需无中断运行,设置 CAL_BG=1(背景校准)、LP_EN=1(低功耗校准);

- 配置 JESD204C:设置 JMODE(如 0x08,12 位 64B/66B)、启用 FEC(SHMODE=2),JESD_EN=1 启动接口;

- 同步 SYSREF:触发 SYSREF 信号,等待 ALIGNED(0x208 寄存器)置 1,确认延迟锁定。

-

振荡器

+关注

关注

28文章

4192浏览量

143170 -

adc

+关注

关注

100文章

7946浏览量

556896 -

通信系统

+关注

关注

6文章

1281浏览量

55232 -

模数转换器

+关注

关注

26文章

4104浏览量

130268

发布评论请先 登录

ADC12D1600和ADC12D1600RF这两种型号之间有什么区别?

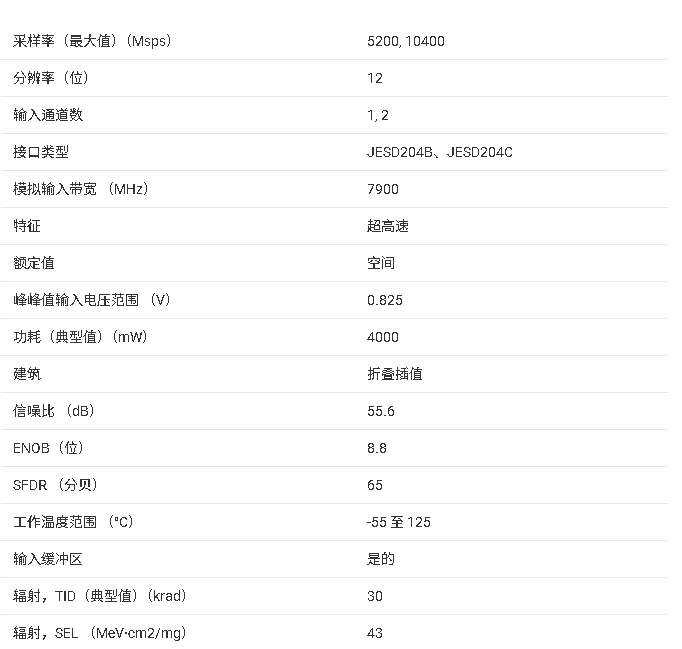

ADC12D1600QML-SP 12 位、2.0/3.2 GSPS 超高速 ADC

ADC12QJ1600-SEP四通道1.6GSPS 12位模数转换器(ADC)数据表

ADC12QJ1600-EP具有JESD204C接口的四通道1.6GSPS 12位模数转换器(ADC)数据表

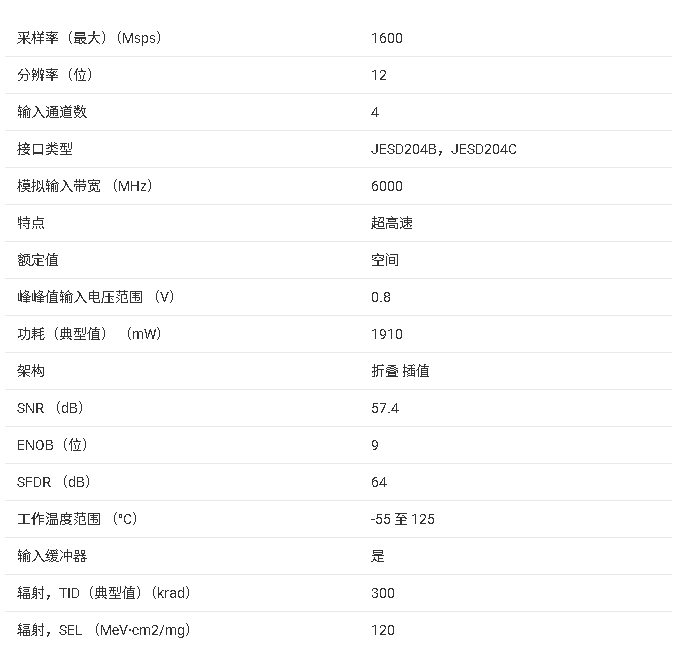

ADC12QJ1600-SP具有JESD204C接口的四通道1.6GSPS 12位模数转换器(ADC)数据

ADC12DJ5200-SEP双通道12位射频采样模数转换器(ADC)数据表

ADC12J2700EVM和ADC12J1600EVM用户指南

ADC12DJ5200-SEP 产品技术总结

ADC12QJ1600-SP 四通道高速模数转换器技术总结

AFE11612-SEP 技术文档总结

ADC128S102-SEP 技术文档总结

ADC12DJ1600 双通道、12位、1.6GSPS ADC技术手册

ADC12DJ1600-Q1 汽车、2通道、12位、1.6GSPS ADC技术手册

ADC12SJ1600-Q1 汽车、1通道、12位、1.6GSPS ADC技术手册

ADC12QJ1600-SEP 技术文档总结

ADC12QJ1600-SEP 技术文档总结

评论