介绍

阈值电压 (Vth)是 MOSFET (金属氧化物半导体) 的一种基本的电学参数。阈值电压 (Vth) 为施加到栅极的最小电压,以建立MOSFET漏极和源极端子之间的导电沟道。有几种方法可以确定阈值电压:根据器件的传输特性、漏极电流 (ld) 与栅极电压 (Vg) 曲线。在测试碳化硅 (SiC) MOSFET时,正向栅极电压扫描和反向栅极电压扫描都表现出滞后效应。这种效应主要是由于陷阱引起的,并导致阈值电压的偏移。这种阈值电压的差异会影响一些器件参数,如漏电流和导通电阻。

为了减小或降低阈值电压的滞后性,JEDEC (Joint Electron Device Engineering Council,联合电子器件工程委员会)引入了JEP183A标准为测量SiC MOSFET的阈值电压提供了指导。这个标准描述了如何确定阈值电压的方法,即:在产生漏极电流和栅极扫描电压之前用调节脉冲。

从Clarius+ V1.14软件套件发布开始,基于JEP183A标准的SiC MOSFET阈值电压测试已包含在4200A-SCS参数分析仪中。这些测试使用两个源测量单元 (SMU),通过Clarius软件执行。

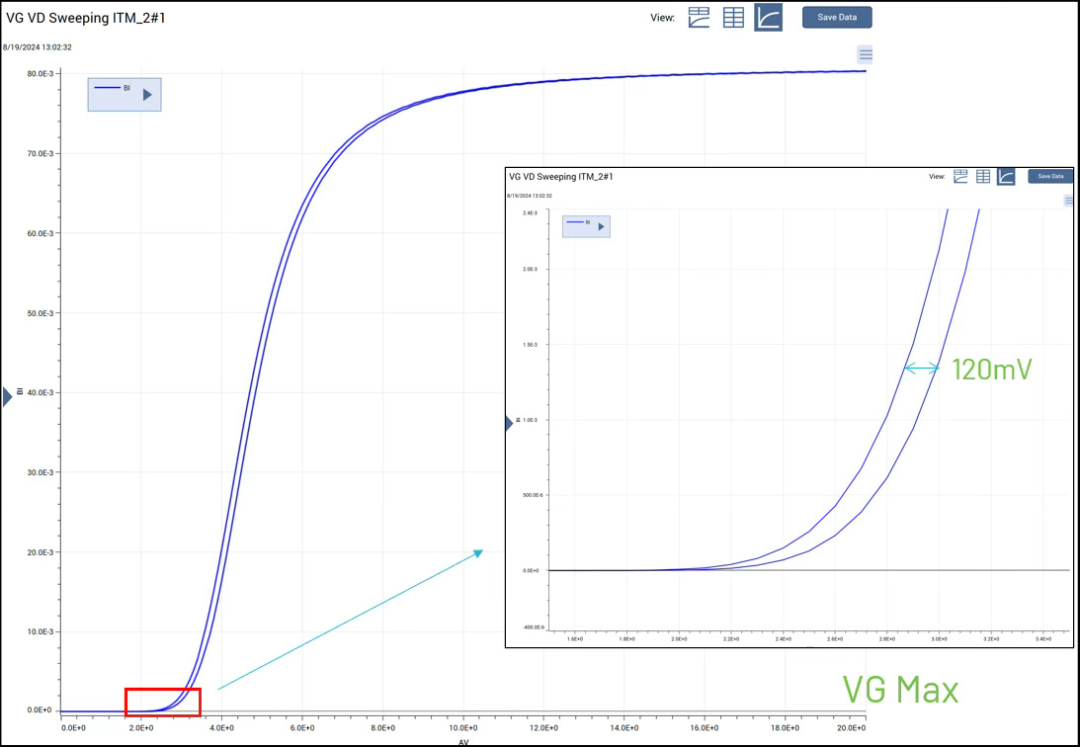

图1. 硅碳化物MOSFET的ld与Vg曲线表现出滞后效应

本应用说明讨论了:根据JEDEC JEP183A标准,使用4200A-SCS参数分析仪,对SiC MOSFET进行精确的阈值电压测量。

JEDEC JEP183A标准

JEDEC JEP183A标准“SiC MOSFET 阈值电压 (Vt)测量指南”解决了硅MOSFET上使用的传统测试方法所表现出的滞后效应。迟滞是由于SiC器件中SiC/SiO2界面中的陷阱数量增加引起的,这导致正向和反向扫描之间的传输曲线发生偏移。

可以通过将栅极电压从0V扫描到最大栅极电压,然后再扫描回0V来观察迟滞。图1所示的SiC MOSFET漏极电流与栅极电压曲线证明了这种效应。在本例中,观察到正向曲线和反向曲线之间存在约120mV的差异。这些扫描是使用Clarius交互式软件生成的。

为了解决滞后效应,将调节脉冲施加到栅极,以帮助在向下栅极电压扫描之前释放陷阱。JEDEC JEP183A标准建议将调节脉冲设置为最大栅极电压。

JEP183A标准描述了SiC MOSFET阈值电压测量的三种不同方法。所有方法最初都在栅极上输出调节脉冲,但随后施加栅极和漏极电压的方式不同。这三种推荐的测试方法是:

■扫描栅极电压和固定漏极电压法

■扫描栅极和漏极电压法

■固定栅极和漏极电压方法

这些方法的详细信息在JEP183A标准中进一步描述。Clarius库包括用于执行前两种方法以提取阈值电压的测试。以下段落解释如何使用这些Clarius库测试。

使用4200A-SCS进行SiC MOSFET阈值电压测量

设置和执行阈值电压测试涉及到器件的硬件连接并使用Clarius软件配置和执行测试。

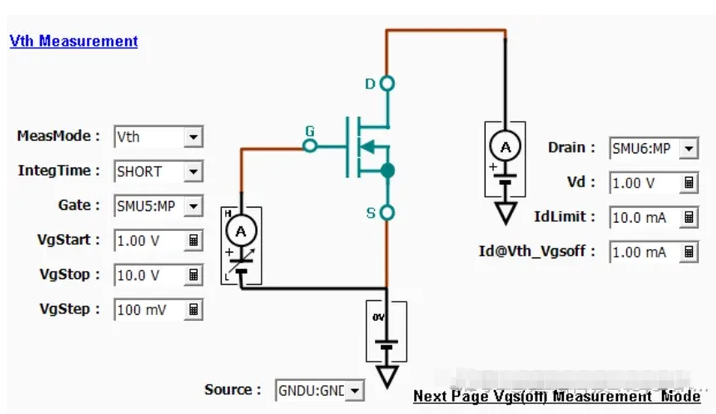

硬件连接

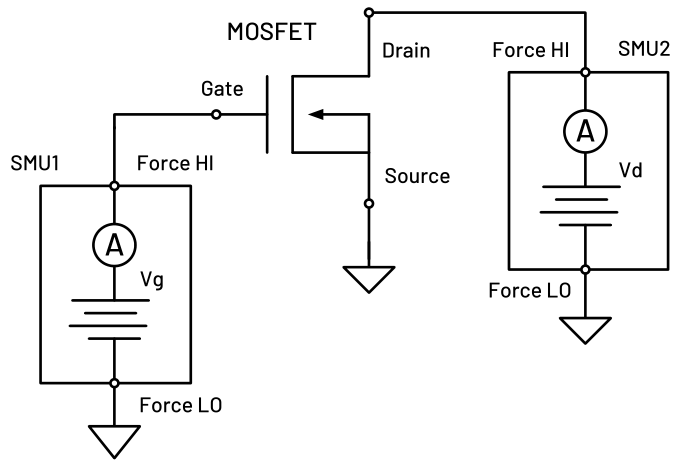

两个SMU和接地单元 (GNDU) 用于执行阈值电压测试,如图2中的基本电路图所示。两个SMU都处于施加电压和测量电流模式。一个SMU (SMU1) 的Force HI端子连接到MOSFET的栅极端子,并施加栅极电压 (Vg),包括调节脉冲和向下电压扫描。第二个SMU (SMU2) 施加固定或扫描漏极电压 (Vd) 并测量漏极电流 (Id) 。Force LO (GNDU) 连接到MOSFET的源端。

电路示意图图中未显示连接到MOSFET的SMU和GNDU Sense HI和LO端子。同时使用施加(Force)和感测(Sense)端子可以与DUT进行四线(或开尔文)连接,以消除引线电阻影响测量精度。

图2. 功率MOSFET的栅极和漏极上SMU的连接示意图

使用 Clarius软件进行SiC MOSFET阈值电压测量

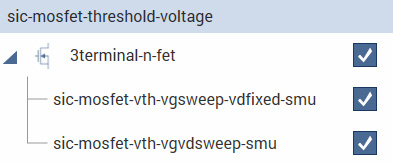

用于进行SiC阈值电压测量的测试在测试库和项目库中都有,可以通过搜索短语“SiC MOSFET”在Clarius界面的“选择”视图中找到。在测试库中找到测试后,可以选择它们,然后将其添加到项目树中。测试库包括两种方法的测试 (sic-mosfet vth-vgsweep-vdfixed-smu和sic-mosfet-vth-vgvdsweep-smu)。如图3的项目树所示,这两个测试也包含在项目库中的项目sic-mosfet-threshold-voltage中。这些测试将在以下段落中进一步描述。

图3. SiC MOSFET阈值电压项目树

扫描栅极电压和固定漏极电压法

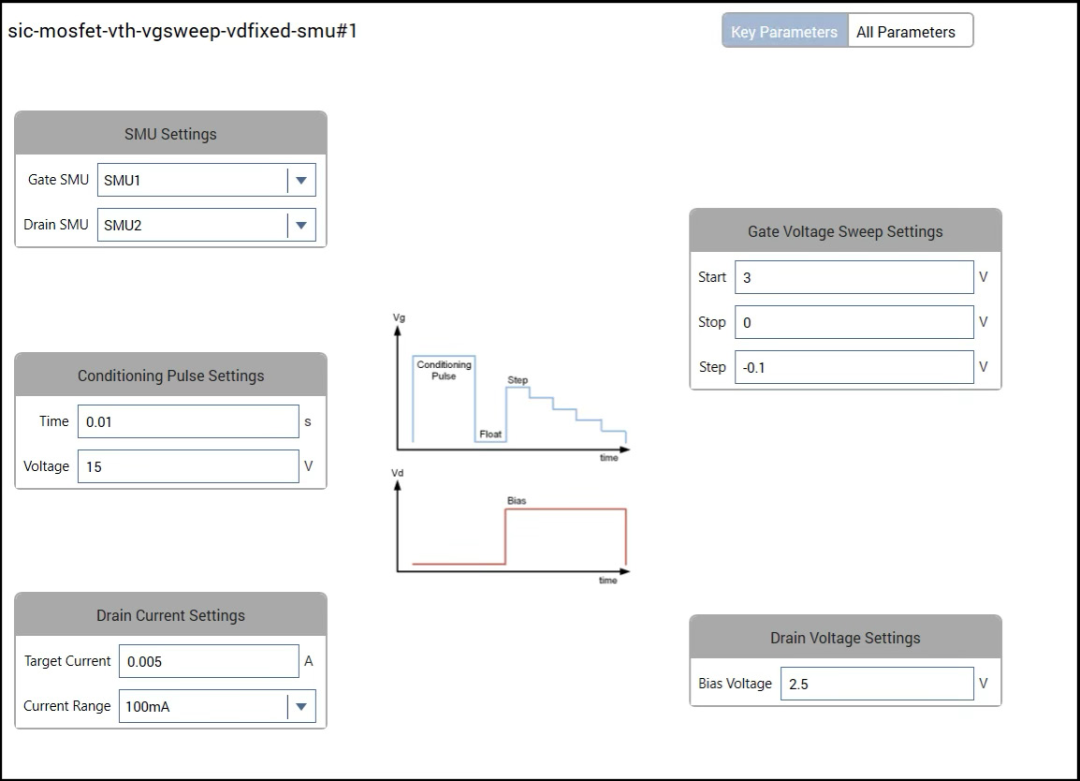

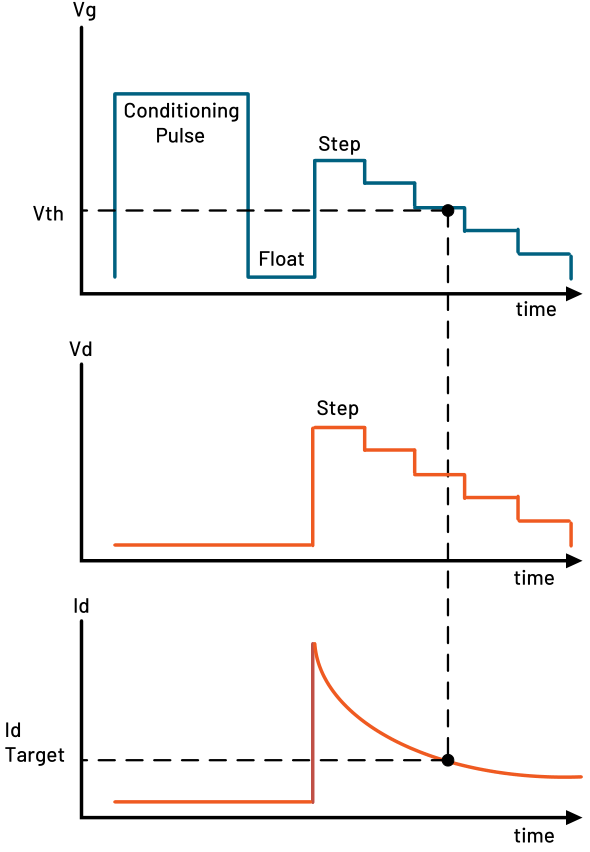

第一个测试是sic-mosfet-vth-vgsweep-vdfixed-smu,它使用扫描栅极电压和偏置漏极电压方法,该方法使用SMU1向栅极 (Vg) 施加调节脉冲,然后向下扫描栅极电压 (SMU1),同时固定漏极A电压 (SMU2)。漏极电流由SMU2测量,并绘制为栅极电压的函数。该测试的栅极电压 (Vg)、漏极电压 (Vd) 和漏极电流 (Id) 时序图如图4所示。

时序图中还显示了Vg图上的阈值电压 (Vth) 和Id图上的目标漏极电流(Id目标)。根据用户定义的目标漏极电流 (Id Target),使用线性插值计算阈值电压 (Vth)。

图4.sic-mosfet-vth-vgsweep-vdfixed-smu测试项的栅极电压,漏极电压和漏极电流的时间曲线

测试的输入参数在Clarius的“配置”视图中设置,如图5所示。该测试具有配置调理脉冲、目标漏极电流、漏极电流测量范围、栅极电压扫描和漏极电压偏置的设置。此测试的所有输入和输出参数都列在附录A的表格中。

图5.sic-mosfet-vth-vgsweep-vdfixed-smu测试项的配置视图

JEDEC JEP183A标准建议将调节脉冲的幅度设置为最大栅极电压。电压扫描的步长应保持较小(0.1 V),以进行准确的阈值电压计算。

该测试方法中的时间参数要求调节脉冲设置在1到100ms之间,并且用户可调。浮动时间是调节脉冲结束和反向扫描开始之间的时间,不可调节。

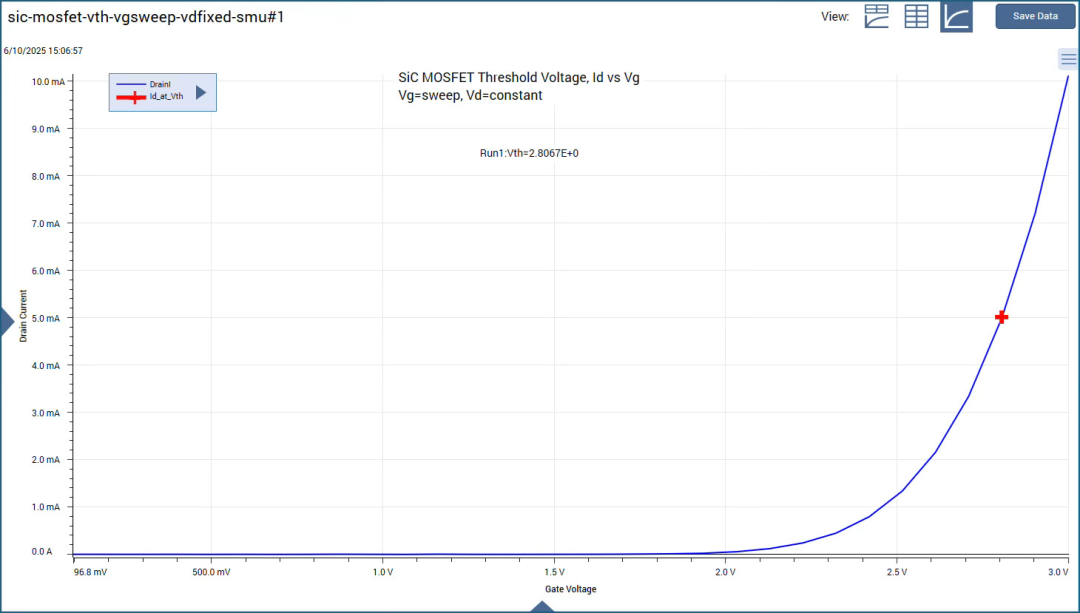

执行测试时,漏极电流在分析视图图中绘制为栅极电压的函数,如图6所示。导出的阈值电压在图表上表示为红叉。

图6.sic-mosfet-vth-vgsweep-vdfixed-smu测试项的Id-Vg曲线中显示Vth

图7显示了泰克MSO5B系列示波器从两个SMU输出的栅极电压(黄色)和漏极电压(蓝色)的屏幕截图。

图7.sic-mosfet-vth-vgsweep-vdfixed-smu测试的示波器捕获图

所有测量值以及导出的阈值电压都显示在分析视图的图表中。工作表的第一个单元格还显示执行后的错误代码。这两项测试的所有错误代码都可以在附录C中找到。

此测试是使用wbg_ulib用户库中的SMU_vgsweepvdfixed用户模块创建的。

扫描漏极和栅极电压法

第二个测试是sic-mosfet-vth-vgvdsweep-smu,使用SMU1向栅极 (Vg) 施加调理脉冲,然后两个SMU向漏极(SMU2) 和栅极 (SMU1) 端输出相同幅度 (Vg=Vd) 的向下电压扫描。该测试的栅极电压 (Vg)、漏极电压 (Vd) 和漏极电流 (Id) 时序图如图8所示。与之前的测试一样,阈值电压 (Vth) 是使用目标漏极电流的线性插值计算的。

图8.sic-mosfet-vth-vgvdsweep-smu测试的栅极电压 (Vg)、漏极电压 (Vd) 和漏极电流 (Id) 时序图

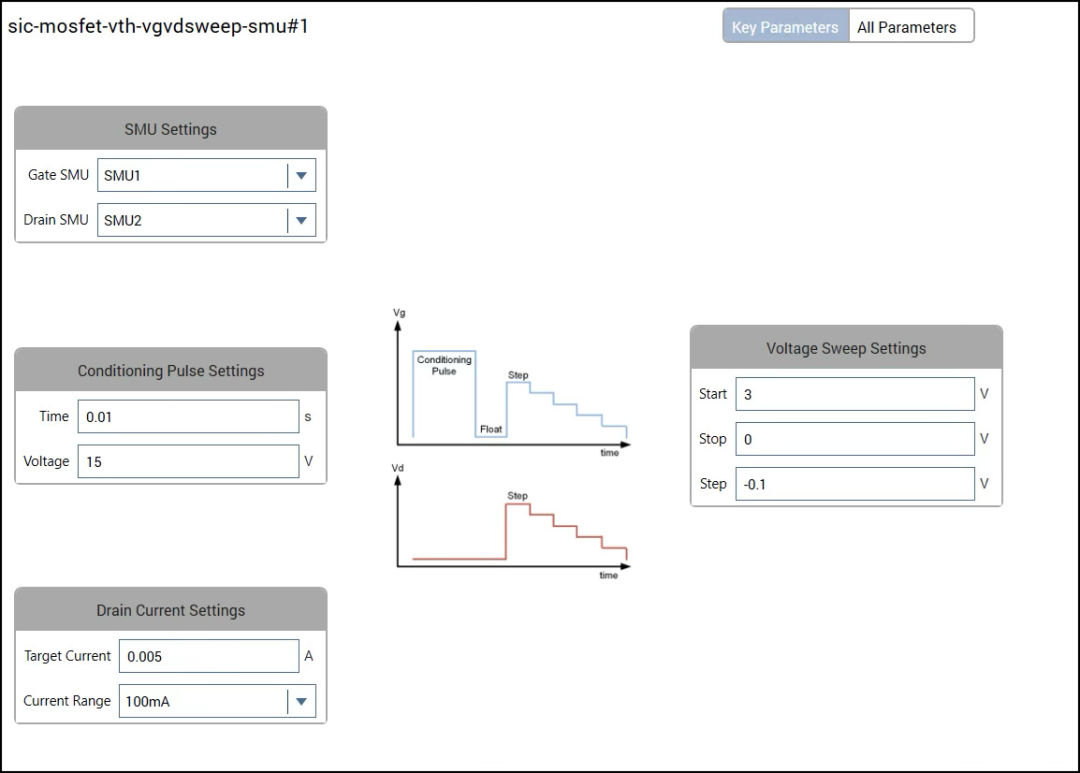

该测试的输入参数在“配置”视图中设置,如图9所示,与第一次测试中的输入参数类似,但没有漏极电压偏置设置。输入和输出参数及其描述列在附录B中。

图9.sic-mosfet-vth-vgvdsweep-smu测试的配置界面

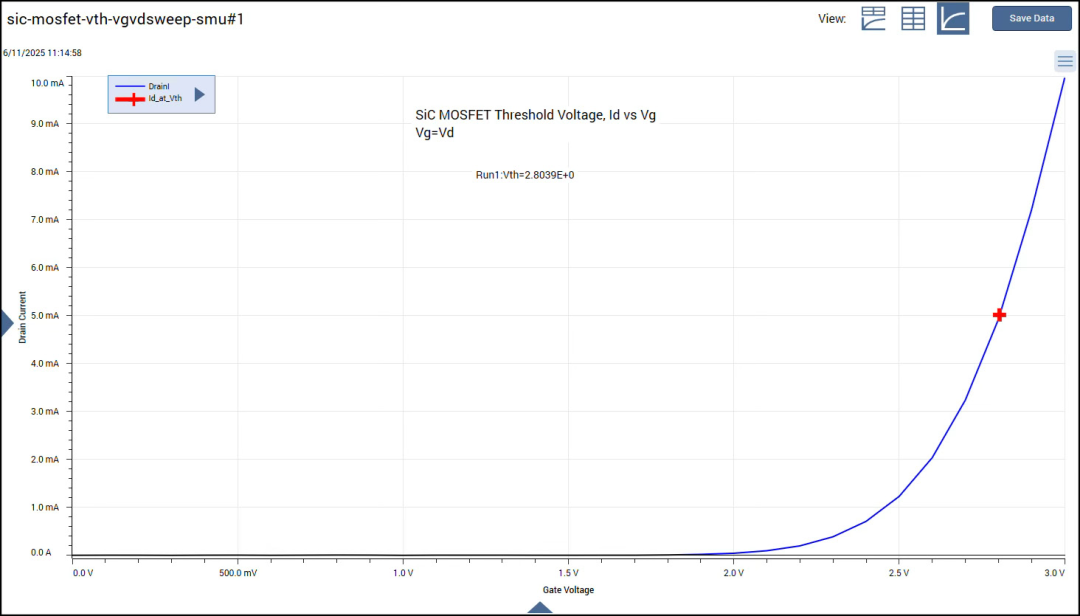

执行此测试的结果如图10所示。与第一个测试一样,外推的阈值电压在传输曲线上显示为红叉。

图10.sic-mosfet-vth-vgvdsweep-smu测试的Id-Vg图中显示Vth

示波器栅极和漏极电压的波形捕获如图11所示。请注意栅极和漏极电压扫描重叠,因为两个扫描同时输出。

图11.sic-mosfet-vth-vgvdsweep-smu测试的示波器捕获图

此测试是使用wbg_ulib用户库中SMU_vgvdsweep用户模块创建的。

结论

4200A-SCS参数分析仪与Clarius+软件套件和两个SMU配合使用,使用基于JEDEC JEP183A标准的测试方法,可以对SiC MOSFET进行精确的阈值电压测量。这些方法通过施加调节脉冲来释放陷阱来减轻滞后效应。凭借其内置的测试和项目库,Clarius软件使4200A-SCS成为SiC器件表征的强大工具。Clarius V1.14版本中添加了另一项SiC MOSFET测试,可在SiC器件上进行准静态C-V测量。

-

MOSFET

+关注

关注

150文章

9411浏览量

229481 -

半导体

+关注

关注

336文章

29978浏览量

257978 -

SiC

+关注

关注

32文章

3502浏览量

68048 -

阈值电压

+关注

关注

0文章

98浏览量

52385

原文标题:基于JEDEC JEP183A标准的SiC MOSFET阈值电压精确测量方法(含直播回放)

文章出处:【微信号:泰克科技,微信公众号:泰克科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

阈值电压的计算

MOS管阈值电压与沟长和沟宽的关系

影响MOSFET阈值电压的因素

什么是MOS管亚阈值电压?MOSFET中的阈值电压是如何产生的?

浅谈影响MOSFET阈值电压的因素

MOSFET阈值电压是什么?影响MOSFET阈值电压的因素有哪些?

基于JEDEC JEP183A标准的SiC MOSFET阈值电压精确测量方法

基于JEDEC JEP183A标准的SiC MOSFET阈值电压精确测量方法

评论