01Latch up概念

在CMOS电路中,存在寄生的PNP和NPN晶体管,它们相互影响在VDD与GND间产生一低阻通路,形成大电流,烧坏芯片,这就是闩锁效应,简称latch-up。

02重要性

随着IC特征尺寸越来越小,集成度越来越高,闩锁效应发生的可能性越来越高,这个现象极为重要,因为它有可能导致整个芯片彻底报废。所以,在质量检测(QUAL测试)中,latch-up是一个必须检查的项目,而且它和静电放电(ESD)防护也是密切相关的

03形成原理

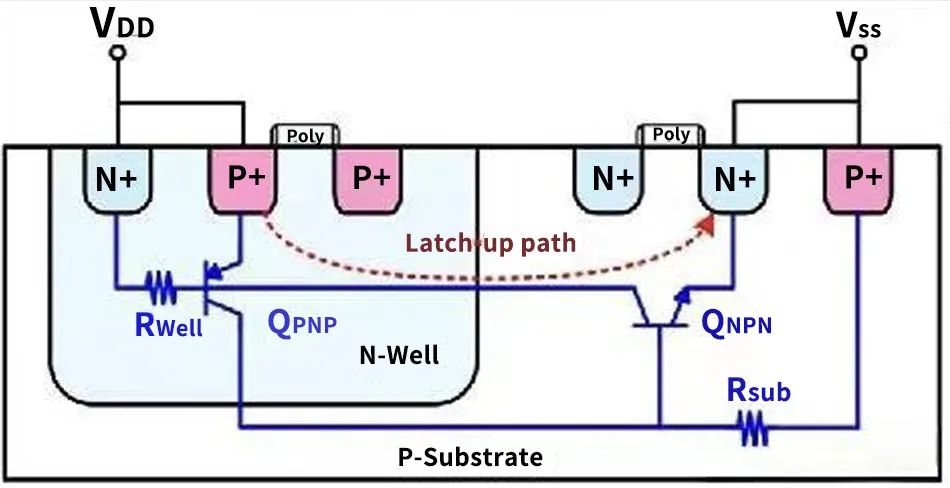

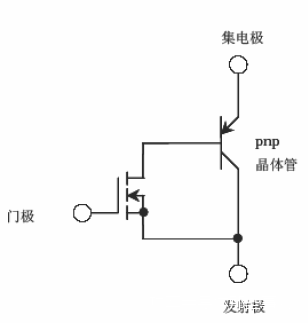

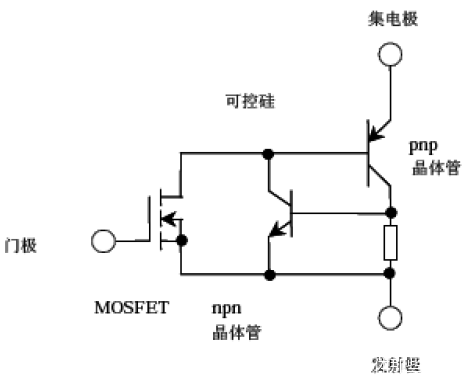

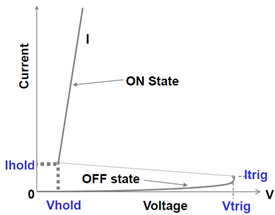

晶体管之间存在PN结。当一个PNP晶体管的集电极连接到NPN晶体管的基极时,如果结反向偏置电压超过一定阈值,就会发生Latch-up现象,如图表1所示。

▲图表1

正常工作情况下,三极管是截止的,不会发生Latch up现象。受到外界来自电源,I/O,ESD静电泄放的干扰时,当一个PNP晶体管被激活时,它通过连接的NPN晶体管的基极转导电流,导致NPN晶体管也被激活,形成一个正反馈回路,电流在这个结构里面不断放大,最终超过芯片承受范围,使得芯片被烧坏。

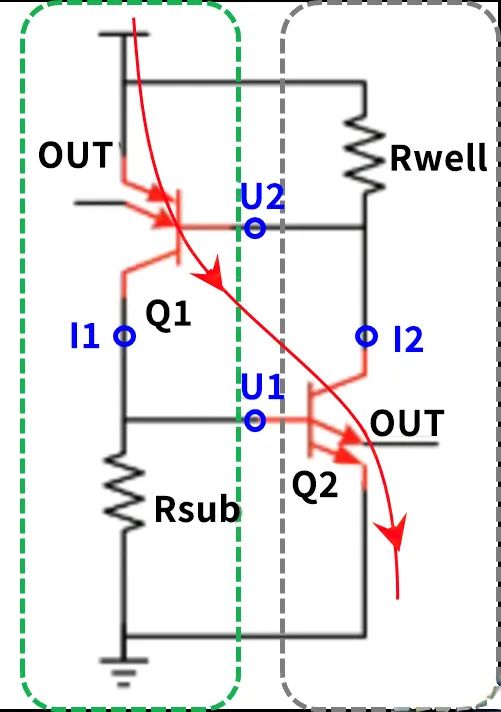

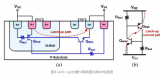

▲图表2

图中电路结构左半部分相当于一个P管放大电路,右半部分相当于一个N管放大电路,且它们的输入输出首尾相连,形成一个正反馈环路。当受到干扰时,PNP管打开,PNP管输出端产生电流I1,I1流经NPN管放大成I2又输入到PNP管的基极,从而导致PNP管的输出端电流I1继续增加,I1增加又导致经NPN管放大后的I2增加,从而形成正反馈环路,电流不断增加。

电路中出现一个低电阻的路径(图表2红色线条所示),导致异常电流流过,这会导致电路失去控制,可能导致器件的损坏或电路功能的失效。

04测试流程

Latch-up测试是集成电路可靠性测试的重要项目之一,主要用于检测芯片在异常电压或电流条件下是否会出现闩锁效应(Latch-up)。

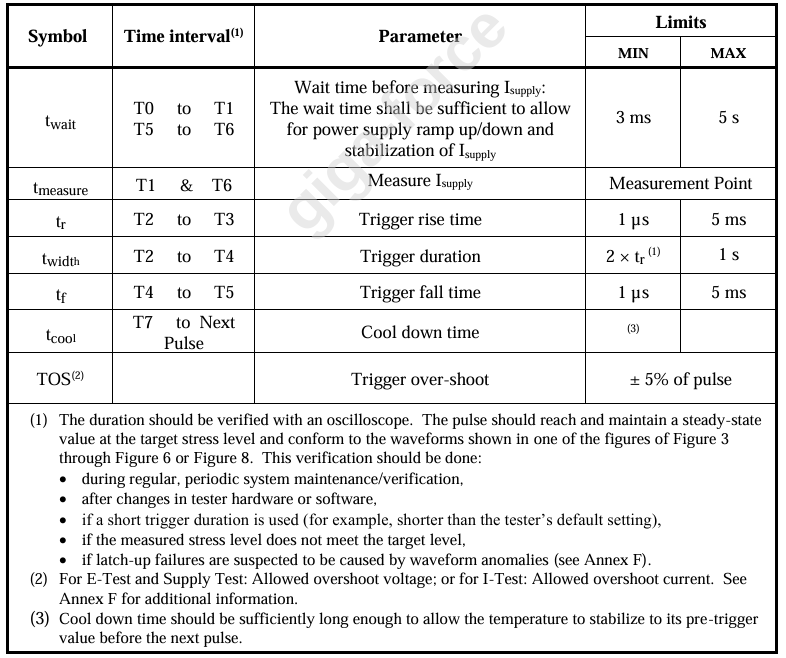

1测试标准

Latch up测试主要依据JESD78F标准进行测试,该标准中将Latch-up测试分为电流测试(I-test) 和电压测试(V-test)。

2测试准备条件

(1)测试温度(室温25℃或特殊温度);

(2)芯片引脚定义(POWER , GND , INPUT, OUTPUT ,I/O) ;

(3)供电引脚(POWER)及IO引脚(INPUT, OUTPUT ,I/O) 的最大工作电压。

3测试内容

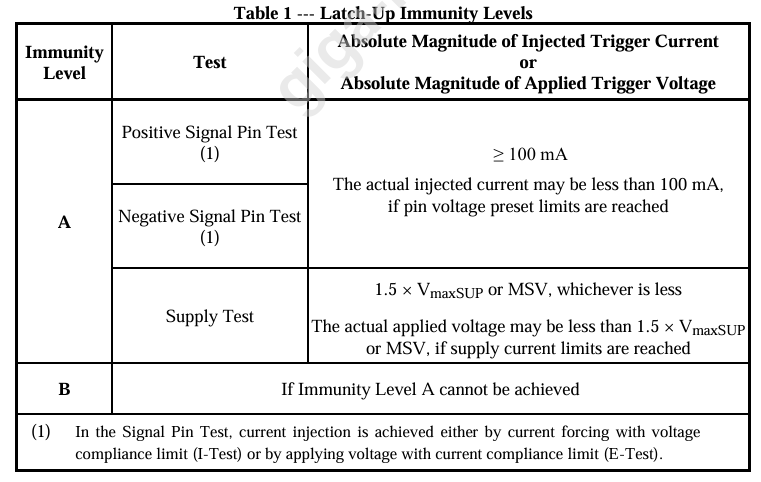

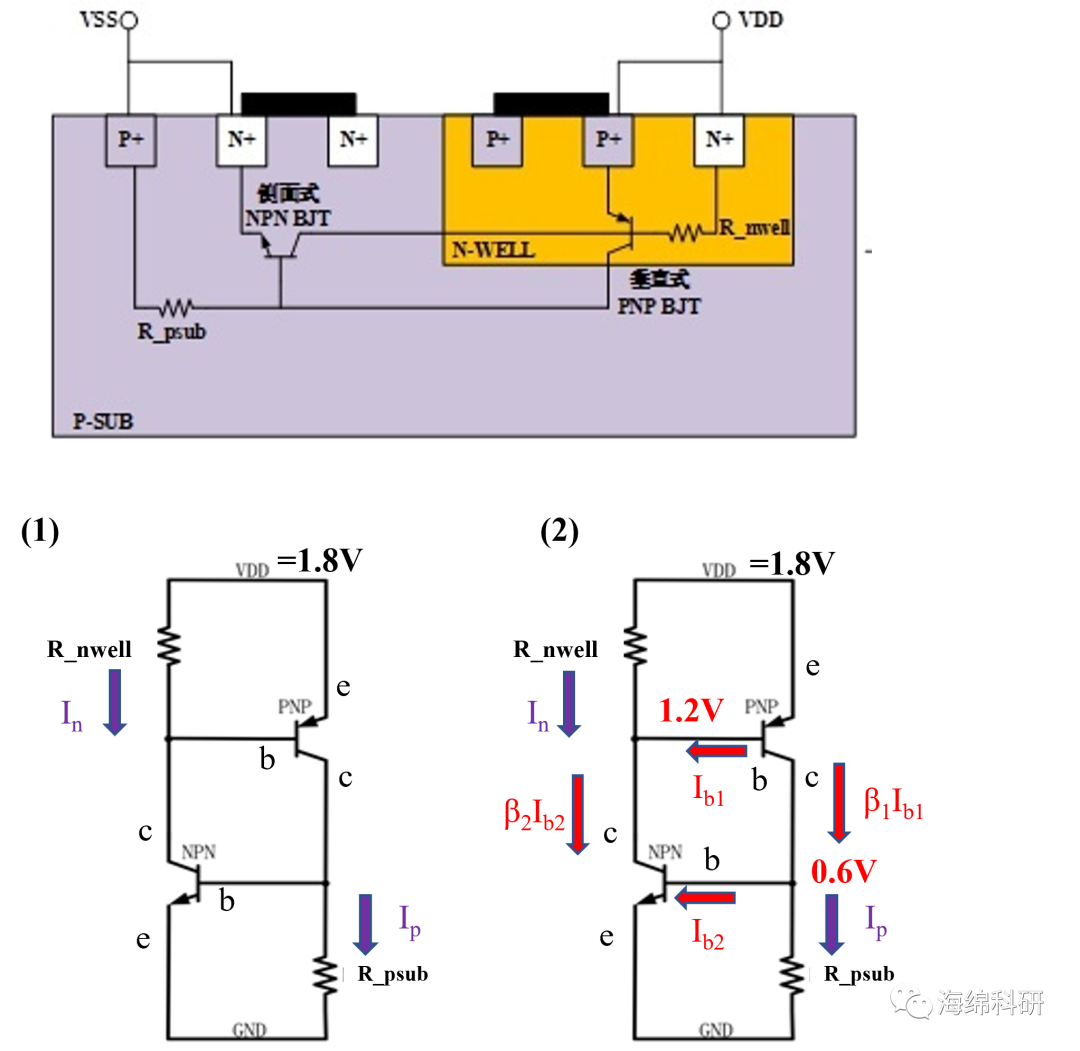

▲图表3

上表为测试闩锁效应的条件及分类:正向电流测试≥100 mA ;负电流测试≥ -100 mA ;电压测试1.5VCCmax或者MSV, 其中MSV表示(Maximum Stress Voltage)最大允许工作电压。

电流测试 I-test,用于测试非电源管脚;电压测试 V-test 用于测试电源管脚。其中I-test又有正向注入/负向抽取两种,正向注入电流会使得端口电压升高,负向抽取电流会使得端口电压降低。

V-test的测试流程

(1)对所有输出和I/O悬空,所有输入管脚置于高电平偏置,所有VDD分别加电为对应的Vmax电压,测量各VDD到GND的漏电流I-pre。

(2)对待测管脚施加V-test源,触发电压取1.5×VCCmax或MSV,触发时间一般取10ms。

(3)去除触发源后将被测管脚复原,测量漏电流I-post,进行失效判断。

(如果I-pre≤25mA, 失效标准为I-post> I-pre+ 10 mA;如果I-pre> 25 mA,失效标准为I-post> 1.4 × I-pre)

(4)如果没有发生Latch-up,对所有输出和I/O悬空,将所有输入管脚都置于低电平偏置,所有VDD分别加电为对应的Vmax电压,测量各VDD到GND的漏电流I-pre,重复实验。

(5)重复以上步骤,直到每个电源Vsupply管脚(或管脚组合)都通过测试。

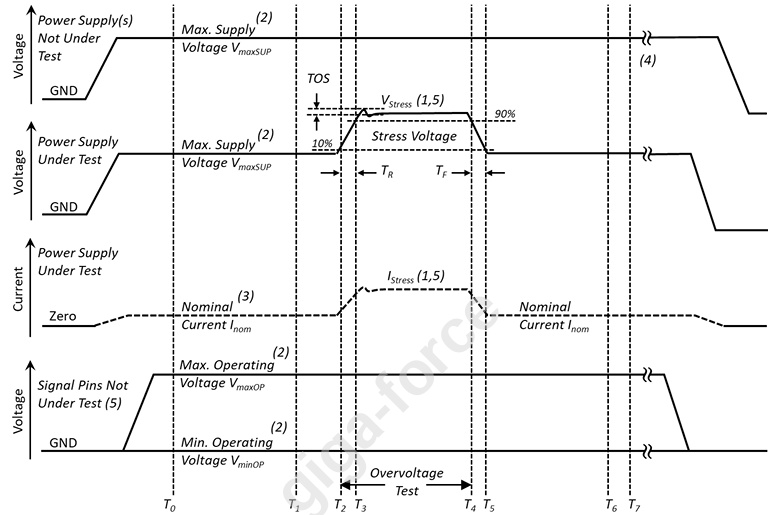

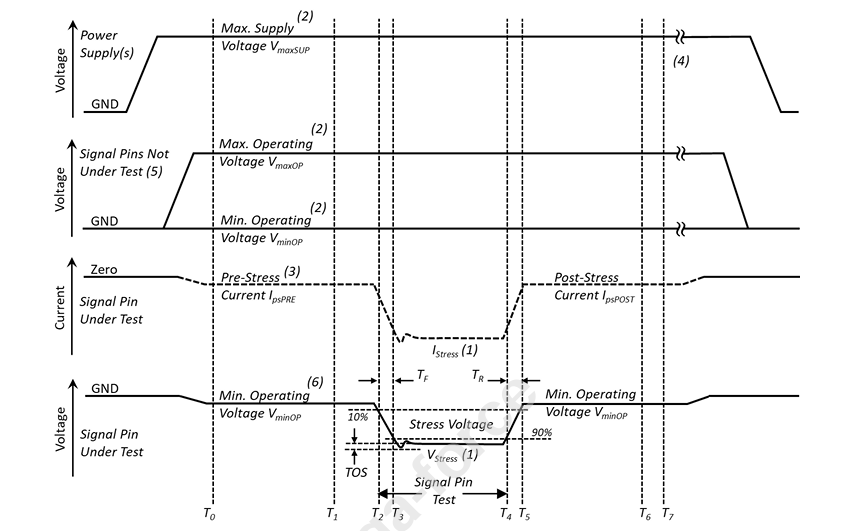

▲图表4

图表4为V-test波形。

I-test的测试流程

(1) 对所有非待测的输出和I/O悬空,所有输入管脚置于高电平偏置,所有VDD分别置于对应的Vmax电压

(2)测量各VDD到GND的漏电流I-pre。

(3)对待测管脚施加I-test源,正电流触发限压取该测试管脚的1.5 × VmaxOP,负电流触发限压取该测试管脚的-0.5×Vmax,触发时间一般取10ms。

(4)去除触发源后将被测管脚复原,测量漏电流I-post,进行失效判断。

(如果I-pre≤25mA, 失效标准为I-post> I-pre+ 10 mA;如果I-pre> 25 mA,失效标准为I-post> 1.4 × I-pre)

(5)如果没有发生Latch-up,对所有未接受测试的输出和I/O悬空,将所有输入管脚都置于低电平偏置,所有VDD分别加电为对应的Vmax电压,测量各VDD到GND的漏电流I-pre,重复实验。

(6)重复以上步骤,直到所有IO管脚都通过测试(除待测试管脚外的其他非输入的IO管脚均悬空)。

▲图表5

图表5为I-test的正电流及负电流测试波形

特殊功能管脚

某些芯片会具有特殊的功能管脚,例如LDO管脚既可作为电源管脚也可作为输出管脚,这些芯片的管脚能为其他芯片或器件提供偏置。而针对这类管脚,使用I-test还是V-test需要根据实际应用情况来确定。

北京季峰检测技术有限公司ESD 实验室始终秉持科学、严谨、专业的态度,致力于为广大客户提供一流的 HBM、MM、Latch-up 检测认证服务。我们深知产品质量和可靠性对于企业的重要性,因此不断提升自身技术水平和服务能力,与您携手共进,共同应对电子产品在静电和闩锁效应方面的挑战。选择北京季峰 ESD 实验室,就是选择放心,选择品质,让我们一起为打造更可靠、更耐用的电子产品而努力。

北京季峰检测技术有限公司是上海季丰的控股子公司,位于北京市海淀区丰豪东路9号院2D楼。

主要服务能力:

(1)ESD测试:HBM、CDM、MM、Latchup;

(2)失效分析:开盖、去层、研磨、2D/3D OM、2D X-Ray、手动探针台、SAT、IV curve测试、WireBonding、Thermal、InGaAs、OBIRCH、SEM/EDS、DB FIB、Nanoprober、TEM等;

同时可承接RA、ATE LB、可靠性板子设计制作、ASSY快速封装、材料分析、ATE回测及测试程序开发、车规可靠性实验等业务,交由上海季丰完成。

北京季峰不仅为您提供一站式的实验服务,还有上门取送件等快速、专业、优质的增值服务,欢迎前来咨询委案。

季丰电子

季丰电子成立于2008年,是一家聚焦半导体领域,深耕集成电路检测相关的软硬件研发及技术服务的赋能型平台科技公司。公司业务分为四大板块,分别为基础实验室、软硬件开发、测试封装和仪器设备,可为芯片设计、晶圆制造、封装测试、材料装备等半导体产业链和新能源领域公司提供一站式的检测分析解决方案。

季丰电子通过国家级专精特新“小巨人”、国家高新技术企业、上海市“科技小巨人”、上海市企业技术中心、研发机构、公共服务平台等企业资质认定,通过了ISO9001、 ISO/IEC17025、CMA、CNAS、IATF16949、ISO/IEC27001、ISO14001、ISO45001、ANSI/ESD S20.20等认证。公司员工超1000人,总部位于上海,在浙江、北京、深圳、成都等地设有子公司。

-

ESD

+关注

关注

50文章

2375浏览量

178812 -

晶体管

+关注

关注

78文章

10245浏览量

146217 -

NPN

+关注

关注

11文章

2686浏览量

51020 -

闩锁效应

+关注

关注

1文章

36浏览量

9659

原文标题:闩锁效应—Latch up

文章出处:【微信号:zzz9970814,微信公众号:上海季丰电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

浅谈IGBT的闩锁效应

闩锁效应的工作原理

什么是闩锁效应?

对 闩锁效应 的一些理解

IGBT中的闩锁效应到底是什么

单片机发生闩锁效应的因素,如何防止发生单片机闩锁效应?

芯片失效机理之闩锁效应

CMOS集成电路中闩锁效应的产生与防护

基于JEDEC标准的闩锁效应测试方法

闩锁效应的形成原理和测试流程

闩锁效应的形成原理和测试流程

评论