三星电子先前发布,到2020年开发3纳米Foundry制程。据分析称3纳米Foundry制程芯片设计费用将高达15亿美金。虽芯片设计费用的增长倍数极高,但据专家分析称其电流效率和性能提升幅度并没有与费用成正比,而且考虑到高额的费用,能设计3纳米工程的企业屈指可数。

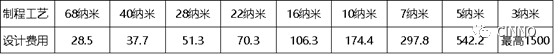

7月17日半导体市调机构International Business Strategy(IBS)分析称3纳米芯片工程的芯片设计费用将高达4亿至15亿美金。IBS说明,在设计复杂度相对较高的GPU等芯片设计费用最高。该公司资料显示28纳米芯片的平均设计费用为5130美金,而采用FinFET技术的7纳米芯片设计费用为2亿9780万美金,是将近6倍的涨幅。半导体芯片的设计费用包含IP、Architecture、检查、物理验证、软件、试产品制作等费用。

这也是半导体行业Fabless工厂一直青睐16纳米FinFET和三星的14纳米FinFET制程的理由。对Foundry厂商来说成本也是颇为伤脑筋的事情,不仅如此3纳米制程难度也颇高。

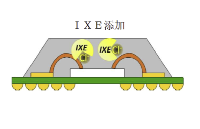

三星电子的3纳米制程将首次使用GAAE(Gate-All-AroundEarly), GAAP(Gate-All-Around Plus)技术,并起名为MBCFET(MultiBridge Channel FET)。技术的核心为确保每个Gate通道的电流存在。若FinFET结构为3面电流,GAA为Gate的所有面都要确保有电流,电流通道变大后随之性能也将提升。

三星电子的MBCFET技术为美国IBM和GF共同开发。若FinFET为鱼鳞状的Gate竖向排列的话,GAA为Gate横向叠加排列方式。为生产此种Gate结构需要Pattern显影、蒸镀、蚀刻等一系列工程的革新,并且为了减少寄生电容还要导入替代铜的钴、钌等新材料。

业界人士称:3纳米工程开发与芯片设计若有庞大财源的支持下是有可行性,但关键在于是否值得如此投资。而且可使用此种工程的公司也就只有高通、苹果、英伟达、苹果等少数公司,这也将是3纳米工程的绊脚石之一。

制造工程所需半导体设计费用(来源:IBS,单位:百万美金)

-

芯片

+关注

关注

463文章

54429浏览量

469381 -

Foundry

+关注

关注

0文章

14浏览量

9640

发布评论请先 登录

芯片测试设备市场持续高速增长--Handler市场2033年将达29.7亿美元 | CAGR 6.8%

3纳米芯片的发展对锡膏行业的挑战?

决战纳米级缺陷!东亚合成IXEPLAS纳米离子捕捉剂如何助力先进封装?

台积电再扩2纳米产能:AI狂潮下的产能豪赌

国产芯片真的 “稳” 了?这家企业的 14nm 制程,已经悄悄渗透到这些行业…

台积电Q3净利润4523亿元新台币 英伟达或取代苹果成台积电最大客户

台积电2纳米制程试产成功,AI、5G、汽车芯片

看点:台积电2纳米N2制程吸引超15家客户 英伟达拟向OpenAI投资1000亿美元

MediaTek采用台积电2纳米制程开发芯片

佳能9月启用新光刻机工厂,主要面向成熟制程及封装应用

今日看点丨某EDA公司认罚并向美支付1.4亿美元罚款;光库科技拟收购安捷讯控制权 2025年全球纯半导体代工收

台积电引领全球半导体制程创新,2纳米制程备受关注

PCIe 6.0 SSD主控芯片曝光!4nm制程,顺序读取高达28 GB/s

台积电Q2净利润3982.7亿新台币 暴增60% 创历史新高

台积电加大投资布局 2纳米制程研发取得积极进展

2020年开发3纳米Foundry制程_芯片设计费将高达15亿

2020年开发3纳米Foundry制程_芯片设计费将高达15亿

评论