思尔芯去年推出的芯神瞳第八代原型验证系统S8-100已实现批量出货,其单核、双核及四核配置均获得国内外众多头部芯片设计厂商的广泛采用。 S8-100搭载高性能AMD VP1902芯片,通过硬件升级显著提升了系统性能——单核等效1亿门容量,并具有丰富的资源和强大的可扩展性。同时,思尔芯全新的RTL编译流程(RTL Compile Flow, RCF)及自动分割技术,实现了关键的软件升级,大幅加速了设计迭代速度。 这一软硬件协同优化的组合,精准应对了当前大规模数字电路设计验证中编译时间过长的核心挑战。

在近期与北京开源芯片研究院(简称“开芯院”)的成功合作中,思尔芯四核S8-100原型验证系统承担了关键角色,高效完成了“香山”第三代昆明湖RISC-V处理器在16核大规模系统(含NOC)上的软硬件协同实测验证。 此次验证不仅充分展现了S8-100在处理复杂系统(性能)上的强大实力,更通过RCF流程显著提升了验证效率,成功实现了“性能+效率”的双重突破,为“香山”处理器后续的快速迭代与创新提供了关键支撑:

●运行性能显著提升:设计被高效部署至2台四核S8-100 (8片VP1902),做静态时序分析的频率为12MHz

● 编译时间大幅缩短:RCF流程使得全流程编译周期缩短至17小时,增量综合功能更是保证了每日的版本迭代与更新

● 互联结构大幅精简:互联结构更简单,拓扑需求更少,接口和线缆配置更简洁,大幅提升了调试效率和工程实施便捷性

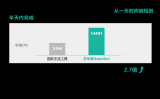

S8-100得益于VP1902的大容量优势,相比上一代VU19P方案,FPGA使用量从16-20片大幅缩减至8片,同时互联线缆数量也从700多条减少到300余条。并结合RCF流程对编译周期的显著优化,客户在收到代码后仅用一周时间就完成了原型验证环境的搭建 (bring up)。

开芯院唐丹博士高度评价S8-100的技术突破:“思尔芯的S8-100不仅提供了大容量,还实现了原型环境搭建周期缩短至1周,支持每日设计迭代更新。除昆明湖16核RISC-V+NOC验证外,我们的4核设计在S8-100上也能以15MHz的速度稳定运行。这些编译流程和分割软件的创新使得软硬件协同效率显著提升。”

思尔芯CEO林俊雄强调:"开芯院是思尔芯的重要战略伙伴,双方合作始于'香山'初代雁栖湖架构,历经南湖架构深化,如今在第三代昆明湖的多核验证中实现突破性协同。 S8-100原型验证系统在昆明湖项目中展现的验证效能,标志着国产高性能处理器与验证工具链的深度融合。我们也将持续通过技术协同创新,与香山一起共同为RISC-V生态系统贡献生产力工具,加速RISC-V生态的产业化进程。"

-

NoC

+关注

关注

0文章

43浏览量

12220 -

RISC-V

+关注

关注

49文章

2958浏览量

53614 -

思尔芯

+关注

关注

0文章

153浏览量

1748

发布评论请先 登录

中科院发布“香山+如意”王炸组合,RISC-V迎来中国时刻

【报名倒计时】Andes晶心与思尔芯强强连手,RISC-V NOW! 北京、上海场亮点抢先看!

思尔芯、MachineWare与Andes晶心科技联合推出RISC-V协同仿真方案,加速芯片开发

思尔芯荣登“国产EDA工具口碑榜”,以“芯神瞳”原型验证解决方案赋能芯片创新

开芯院采用芯华章高性能数字仿真器GalaxSim,RISC-V 验证获近3倍效率提升

西门子EDA与北京开源芯片研究院达成战略合作

芯华章RISC-V敏捷验证方案再升级

超大规模芯片验证:基于AMD VP1902的S8-100原型验证系统实测性能翻倍

思尔芯携手Andes晶心科技,加速先进RISC-V 芯片开发

思尔芯超大容量S8-100,简化并加速开芯院香山昆明湖16核RISC-V+NOC验证

思尔芯超大容量S8-100,简化并加速开芯院香山昆明湖16核RISC-V+NOC验证

评论