GalaxSim Turbo 3.0

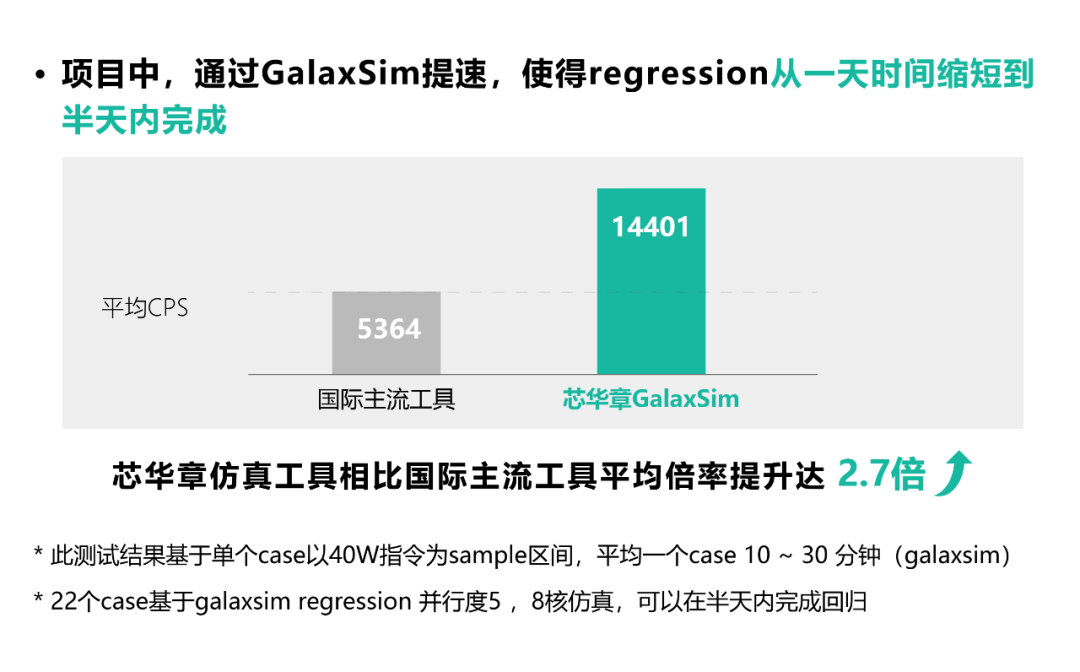

2025年11月,系统级验证EDA解决方案提供商芯华章科技与北京开源芯片研究院(以下简称 “开芯院”),基于GalaxSim Turbo 3.0在事件驱动和周期驱动双引擎在仿真性能上的优势,成功将“香山”第三代昆明湖架构RISC-V处理器的验证效率提升近3倍,为国产开源高性能处理器的研发迭代注入关键动力。

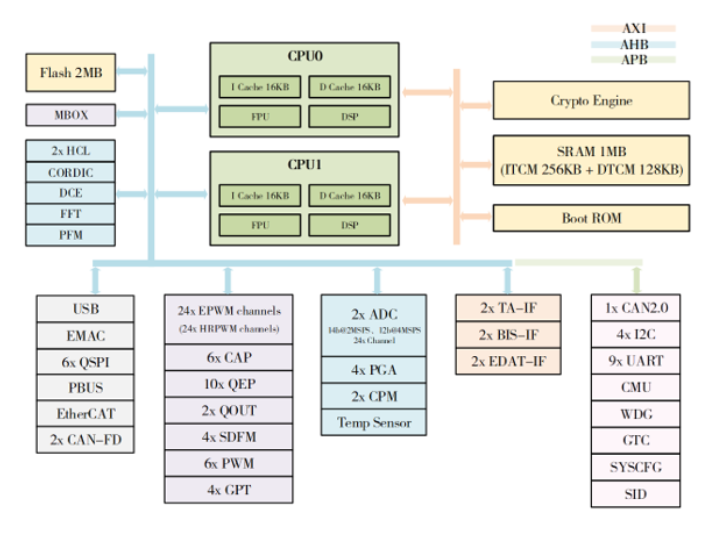

作为国产 RISC-V 生态的核心推动者,开芯院 “香山” 系列处理器一直以突破高性能开源芯片技术壁垒为目标,而复杂架构带来的验证周期长、调试难度大等问题,成为影响研发进度的关键瓶颈。

此次合作中,GalaxSim Turbo 3.0 的高速仿真模式在无需修改验证环境的前提下,大幅提升仿真并行度,其混合仿真模式既兼容 SystemVerilog 语法与 UVM 特性,又通过 XEDB 波形合并、功能覆盖率分析等实用调试工具,确保验证流程的连贯性与精准性,充分匹配 “香山” 处理器的严苛验证需求。

较于传统仿真工具和开源的verilator 工具,GalaxSim Turbo 3.0 展现出多维度优势:

1

使用门槛更低,语法支持范围更全面

支持Verilog/SystemVerilog全语法,额外支持SVA,Functional Coverage等Verilator没有的功能,同时可在原先的仿真用例上可以一键切换

2

易用性更强

不局限C Testbench,验证环境的移植平滑,维护成本大大降低

3

并行效率高

Verilator线程数目需要编译前指定,Turbo的线程数目可以在RunTime的时候根据服务器资源指定,大大提高多线程的管理效率

4

仿真性能卓越

在拆分设计之前对设计描述方式和信号同步机制进行深度优化,同时可以根据客户设计特点进行特殊的定向优化

5

资源管理智能

运行时可以自动寻找合适的CPU资源,并得到计算资源,通讯资源的优化匹配

6

调试能力全面

支持并行下载芯华章波形文件格式XEDB,波形文件大幅减小,下载速度显著提升,得到完整的一体化Debug体验

开芯院院长唐丹表示:

“‘香山’处理器的研发核心诉求是在保证架构创新与性能突破的同时,加速验证闭环与产品落地。‘香山’高性能开源处理器选择使用芯华章 GalaxSim Turbo 3.0 的双引擎技术加速实现验证效率翻倍,特别是在复杂场景下的并行调度能力和全流程调试工具,有效解决了开源架构验证中速度与精度难以兼顾的痛点。

更重要的是,工具与现有流程无缝衔接,大幅降低了研发成本。芯华章将GalaxSim开放给开芯院免费使用,无疑会为RISC-V生态注入强劲动力,让更多团队能够借助量产级国产EDA工具,加速AI、高性能计算等关键领域的芯片创新。

我们也期待与芯华章保持常态化深度合作,共同推动国产开源芯片生态逐步走向成熟。”

芯华章联席CEO谢仲辉表示:

“‘香山’处理器作为高性能RISC-V开源领域的标杆项目,其复杂的验证需求也推动了GalaxSim产品不断迭代升级。

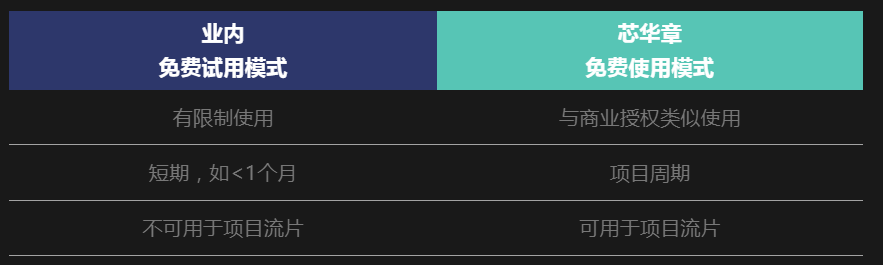

此次验证效率翻倍的成果,也彰显了产业链协同的巨大价值。我们希望通过开放GalaxSim的免费使用,打破传统短期评估模式的局限,让初创团队能直接将经过‘香山’等标杆项目检验的仿真工具用于实际研发。

帮助国内初创团队降低工具门槛,缩短产品开发周期,真正为国产芯片在AI、高性能计算等关键领域的自主发展筑牢根基。推动国产 EDA 与芯片产业双向奔赴、共同成长。

下载开芯院“香山”及仿真框架GalaxSim适配

https://github.com/OpenXiangShan/XiangShan(PR#4893)

申请免费使用芯华章GalaxSim

https://free.x-epic.com/

-

仿真

+关注

关注

55文章

4535浏览量

138655 -

仿真器

+关注

关注

14文章

1052浏览量

88185 -

eda

+关注

关注

72文章

3143浏览量

183711 -

RISC-V

+关注

关注

49文章

2946浏览量

53534 -

芯华章

+关注

关注

0文章

195浏览量

12013

原文标题:开芯院采用芯华章高性能数字仿真器GalaxSim,RISC-V 验证获近3倍效率提升

文章出处:【微信号:X-EPIC,微信公众号:芯华章科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

国芯科技获批建设RISC-V开源芯片先进技术研究院

思尔芯、MachineWare与Andes晶心科技联合推出RISC-V协同仿真方案,加速芯片开发

芯华章仿真器GalaxSim荣登“国产EDA工具口碑榜”

智芯公司荣膺2025“中国芯”RISC-V生态推广示范案例

喜讯|昊芯RISC-V DSP荣获“中国芯”RISC-V生态推广奖

芯华章GalaxEC HEC工具破解RISC-V验证难题

芯华章开放免费使用商用级仿真器GalaxSim,加速中国芯片初创公司发展

2025 RISC-V中国峰会|思尔芯以数字EDA赋能产业生态,加速商业创新

开芯院采用芯华章高性能数字仿真器GalaxSim,RISC-V 验证获近3倍效率提升

开芯院采用芯华章高性能数字仿真器GalaxSim,RISC-V 验证获近3倍效率提升

评论