继X60和X100之后,进迭时空正在基于开源香山昆明湖架构研发第三代高性能处理器核X200。与进迭时空的第二代高性能核X100相比,X200的单位性能提升75%以上,达到了16 SpecInt2006/GHz,单核性能提升125%以上,达到了50 SpecInt2006/Core,主要应用于超级AI计算机、云计算、高阶自动驾驶等高性能计算场景。

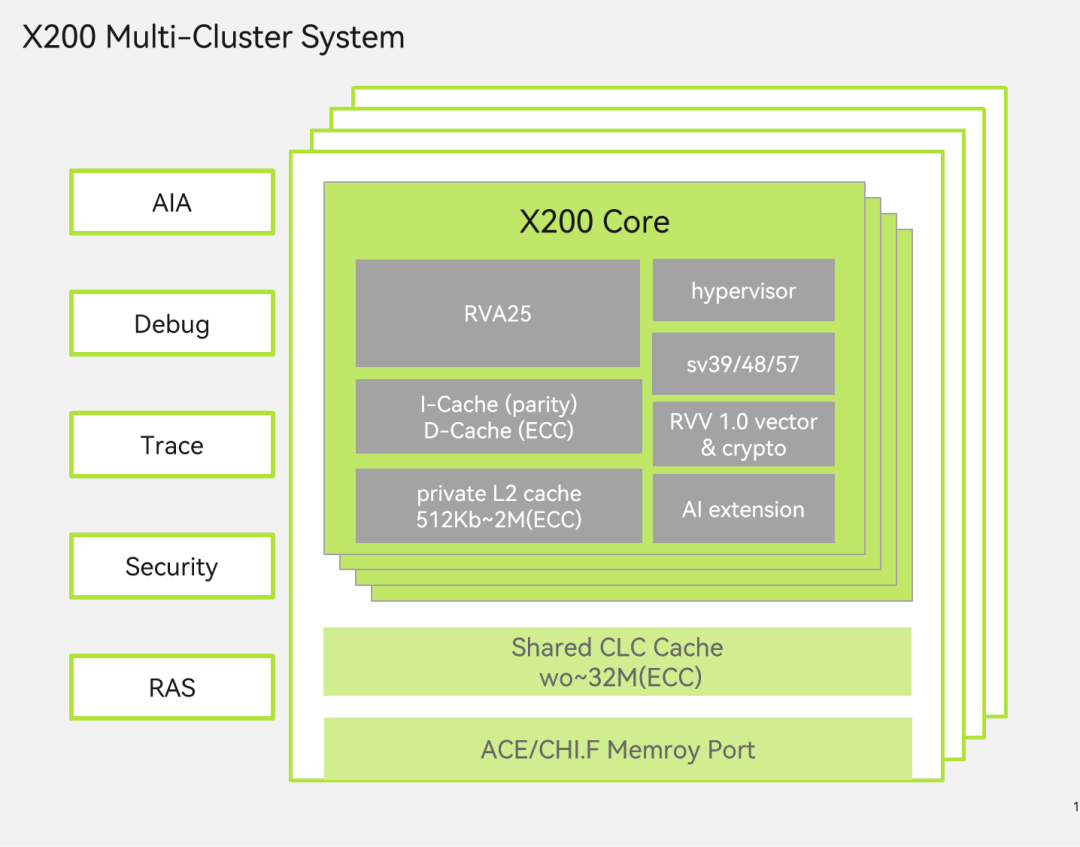

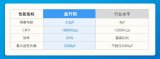

X200是一款6发射、14级流水线的超标量乱序高性能RISC-V核。X200的整体特性如下:

▲

SpecInt2006 > 16分/GHz,单核频率可达3.2GHz @ 7nm

▲

支持RVV1.0,Vector Crypto 扩展以及进迭时空 IME 扩展

▲

支持RVH,AIA技术,并且能够与进迭时空自研IOMMU配合实现完整的虚拟化

▲

支持安全隔离技术,与进迭时空自研 IOPMP配合实现云计算级别的机密计算安全方案

▲

支持服务器级别RAS,Trace特性

▲

支持全芯片高效CHI互联,与进迭时空自研NoC总线配合最大128核心的并行互联

▲

将支持2025年定稿的最新 Profile 规范(RVA25)

X200 架构与微架构创新

基于开源香山,快速迭代

“昆明湖”是开芯院开发的第三代高性能核,整体性能对标 Arm N2,达到 SpecInt2006 性能15分/GHz。开芯院不仅开源了昆明湖全部的设计代码,还提供了昆明湖的验证环境、Golden model、性能分析工具(如完整的Simpoint Flow)以及经过部分对齐的昆明湖Gem5模型。基于开源的昆明湖性能模型和架构设计,可以大大减少了处理器设计过程中架构探索的时间,并在开源性能模型的基础上进一步做微架构创新和性能迭代。

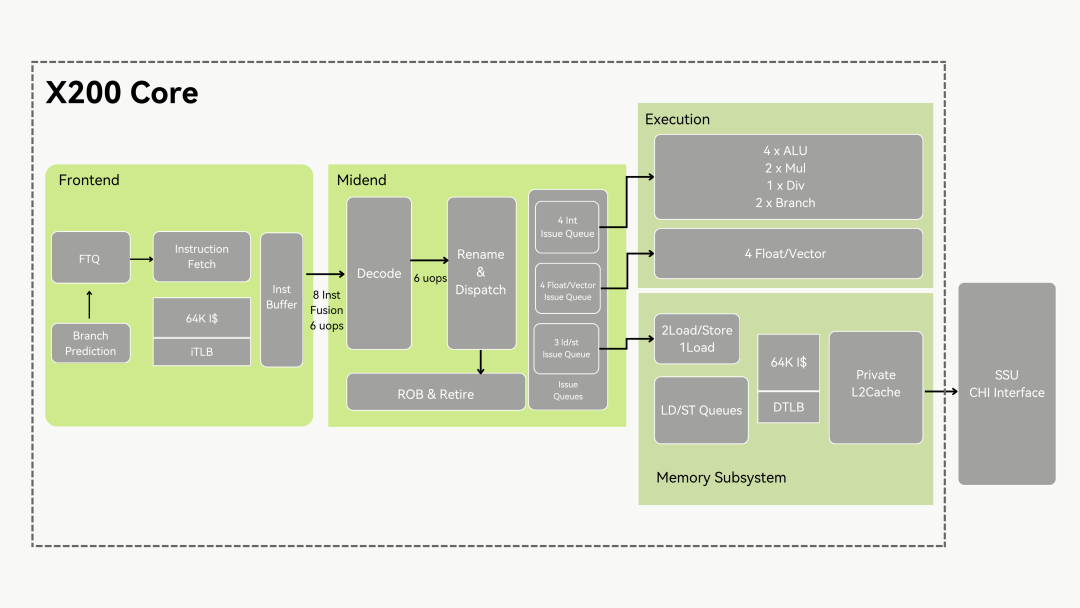

取指前端:昆明湖采用了分支预测和指令缓存访问解耦(下称Decouple)的架构,最大限度减少分支指令对高带宽取指需求的影响。分支主预测器采用两级FTB 加TAGE-SC结构,配合XS-Gem5的前端建模,设计了合理的参数规格;

执行后端:昆明湖实现了基于推测的指令唤醒与发射、Move指令消除、基于Checkpoint检测点的指令恢复等多项机制,有效降低后端指令执行延迟,并提升推测错误时的恢复速度;

访存单元:昆明湖探索了多种预取机制,基于第一级数据缓存实现了Stride, Stream, SMS, SPB的混合预取算法,基于私有的二级缓存L2 Cache实现了BOP与Temporal的算法,在SpecInt2006基准测试上取得了出色的效果。

因为香山核的全套开源以及出色的微架构设计,进迭时空X200选择基于开源昆明湖研发第三代高性能CPU核。在昆明湖的架构上,进迭时空根据面向的计算场景,对部分模块进行了优化,进一步平衡了部分模块的PPA指标。X200 SpecInt2006能够达到16分/GHz,相较前代X100提升75%以上。

取指前端升级

取指前端作为CPU核流水线的起点,其效率直接决定了后级流水线的运行负荷,是影响指令吞吐量的关键瓶颈。近年来,Apple M2, AMD Zen4 等处理器架构均在取指前端进行了大量的优化。

X200的取指前端,基于 Decouple 架构,进一步改进了FTB的结构,提升分支指令的存储利用率;扩展了对2-Taken Branch 场景的支持,可实现每周期至多预测2个跳转分支。

相应的,X200优化了指令Cache的组织结构,支持两个独立的取指块并行取指。通过调整指令Cache Tag和Data的访问流水级,缓解了指令Cache的访问冲突,进一步提升整体的取指带宽。

访存及互联设计优化

访存及互联往往是CPU核中最复杂的部分,访存单元的设计也极大地影响了CPU核的性能。

X200的访存单元优化了整体访存流水线,支持了Load/Store复用流水线,平衡了性能和资源的消耗。针对整个访存通路,通过指令提前唤醒和流水线优化,极致优化访存延迟,L1 Cache的Load To Use Latency控制在4个周期,2M Priave L2 Cache控制在10个周期,Cluster Level Cache控制在~30个周期;针对应用场景,进一步调优预取算法;核级别和簇级别均支持超深的Outstanding能力,面向AI等大数据量搬运场景,允许更多事务在下个层次的内存系统中并行,减少整体内存的访问延迟。

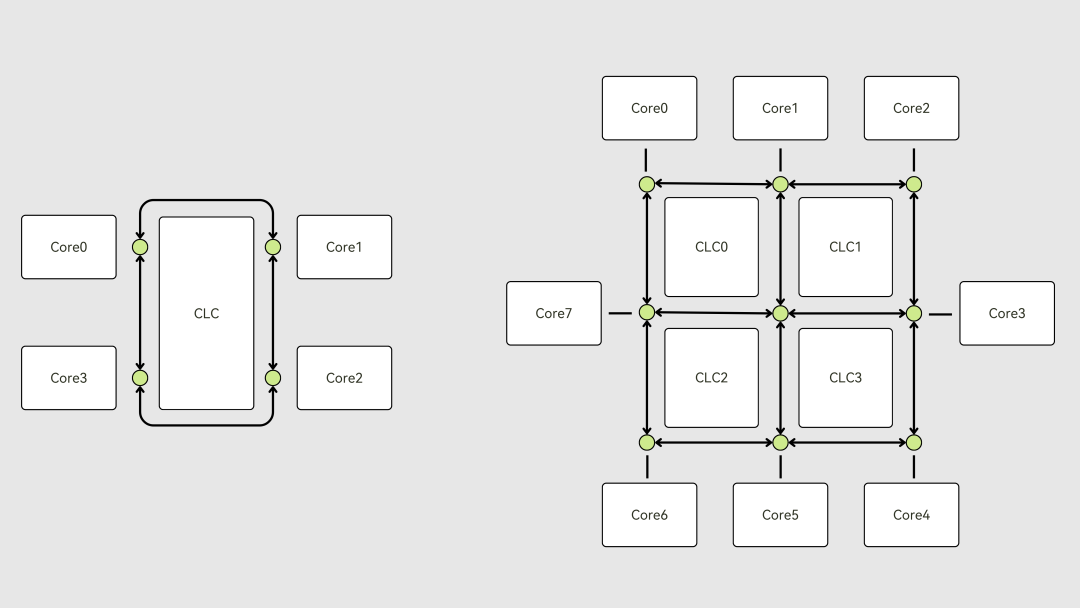

在互联的设计上,从核互联成簇以及多簇之间的互联,均使用了CHI的标准协议,最高可支持到CHI.F协议,核间根据簇中核的规模,使用 Ring/Mesh Bus进行互联,在提升可扩展性的同时,进一步提升簇内总线的频率与带宽。支持Cache Stash的功能,能够通过主动的缓存预存,降低关键数据包的获取延迟。

向量及AI单元优化

X200支持RISC-V Vector1.0及Vector Crypto指令集,VLEN支持256/512/1024可配,数据处理宽度支持4x128/4x256可配。矢量整型指令支持SEW=8/16/32/64;矢量浮点指令支持SEW=FP16/BF16/FP32/FP64。访存处理宽度上支持3x128/3x256的可配,并支持矢量访存指令的非对齐访问。

同时,X200支持符合RV规范的IME扩展的 AI 增强指令

(INT4/INT8/FP8/FP16/BF16/FP32),提供灵活易用的融合 AI 算力。此外,X200可配地通过接口扩展的方式支持AME扩展,以提供更加定制化的AI算力。

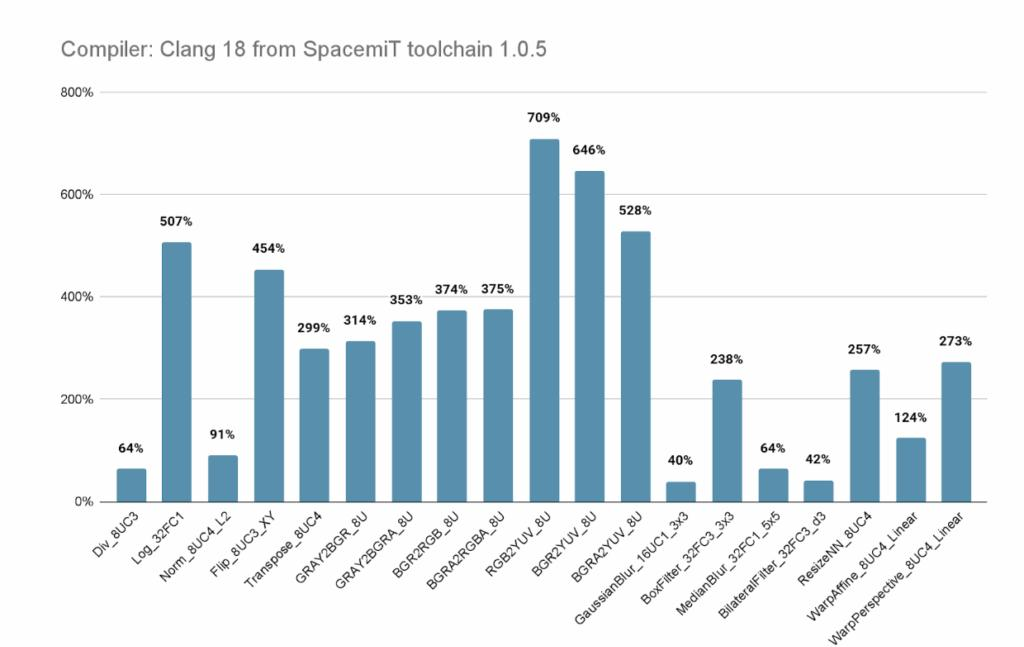

在此基础上,X200针对常见的应用场景,结合算法特点,对向量/AI处理能力和能效进行优化,并重点对向量访存和向量计算资源的均衡和协同、复杂访存pattern以及复杂元素置换操作在乱序核中的的实现等方面进行深度调优。同时,考虑到大带宽向量带来的庞大资源投入,X200基于对大量算法的模拟分析,评估并权衡不同指令对资源/功耗开销以及性能回报,做了不同层次的向量可配性,以满足不同应用场景的性能和PPA需求。

新扩展指令集支持

RISC-V是一个高速发展、充满活力的指令集,2024年,RISC-V共批准(Ratified)了23个规范,RISC-V正快速在各个场景下,拉近与x86、Arm之类成熟指令集的距离。X200面向应用领域的需求,进一步对RISC-V最新的扩展进行了支持:

▲

支持QoS规范(CBQRI, QoSID),进一步提升高优先级数据的延迟表现,增强系统的稳定性和实时性

▲

支持Svadu, Zacas扩展,分别降低多核间页表更新的代价,减少多核抢锁的概率,提升多核系统的效率

▲

支持CFI扩展,使用Shadow Stack和 Landing Pad技术保护内存,降低系统被攻破的概率

X200 也将持续跟进RISC-V的最新扩展以及 Profile,将会支持今年定稿的最新Profile(预计为 RVA25)。

服务器级特性优化

X100已经实现了完整虚拟化、符合云计算场景的安全功能、符合计算机7*24小时稳定工作的RAS特性等。X200在X100的基础上,在完整实现这些功能的同时,也将做进一步增强。重点面向云服务应用场景,通过优化TLB及Walk Cache的组织形式,减少虚拟化多级地址翻译带来的性能损失;扩展Trace以及HPM(高性能计数器)功能,配合自研总线进行系统级优化,提升性能分析、问题定位的跟踪效率;支持更多RAS信息上报,配合全通路CHI总线支持,进一步提升总线的稳定性,配合进迭时空服务器管理固件,能够提升服务器系统可发现错误、可纠正错误、可管理错误能力。

借助于香山昆明湖出色的架构和微架构基础,进迭时空开展了X200的研发工作,并实现了对第二代处理器核X100的大幅性能提升。当前,X200已经完成了代码开发并进入了持续的PPA优化阶段,预计将在2025年Q4季度研发完毕,基于X200的高性能计算芯片将在2026年底面市。

更多X200的设计细节将在后续的公司微信公众号中陆续做介绍,敬请大家期待。

-

处理器

+关注

关注

68文章

20150浏览量

247290 -

进迭时空

+关注

关注

0文章

50浏览量

276

发布评论请先 登录

进迭时空K1 Linux kernel upstream进展 | 取之于开源,贡献于开源

进迭时空参加2025 RISC-V北美峰会,披露第二代RISC-V AI CPU芯片 K3 进展

取之于开源,贡献于开源:进迭时空AI计算生态开源贡献

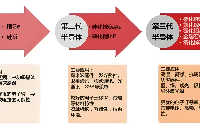

第三代半导体的优势和应用领域

金升阳推出高性能第三代插件式单路驱动电源

第三代半导体器件封装:挑战与机遇并存

进迭时空亮相RISC-V产业发展大会:新AI CPU引领大模型时代

第三代半导体对防震基座需求前景?

进迭时空第三代高性能核X200研发进展

进迭时空第三代高性能核X200研发进展

评论