CMOS的逻辑门如何应用在电路中

前言

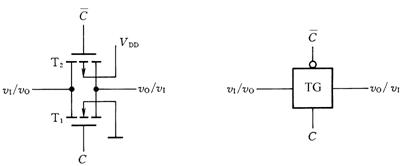

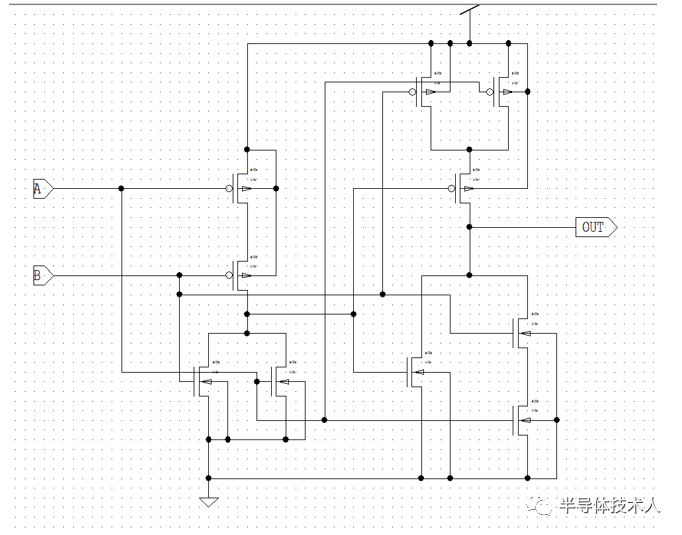

在如今的电子电路中,CMOS逻辑门有着接近零静态功耗和超高集成度的特点,是数字电路不可或缺的存在。其独特之处在于PMOS与NMOS晶体管的互补设计:当输入低电平时,PMOS导通实现电流上拉;输入高电平时,NMOS导通完成信号下拉。两种晶体管交替工作,构成无直流通路的完美配合。合科泰采用的沟槽屏蔽栅工艺优化了晶体管性能,让CMOS互补管在开关切换的电路降低,满足现代互联网和人工智能的能耗要求。

CMOS逻辑门

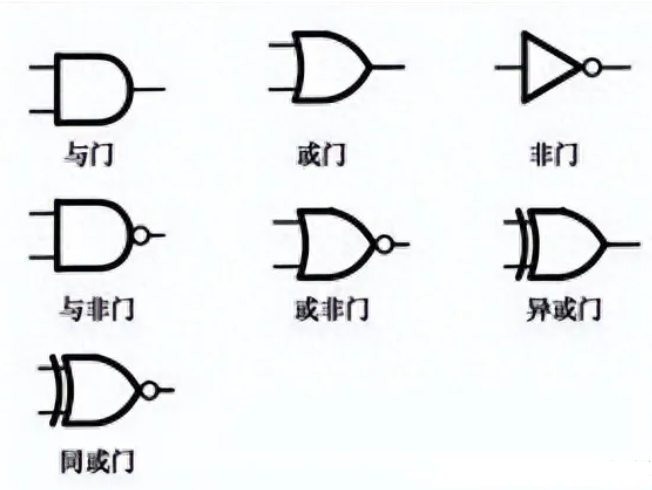

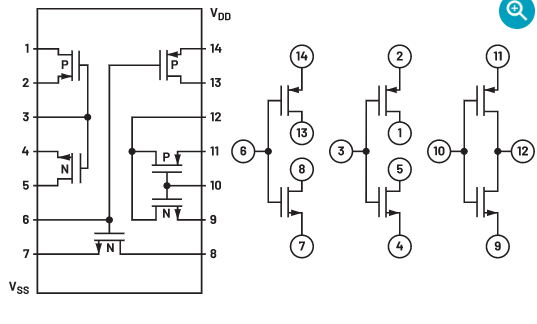

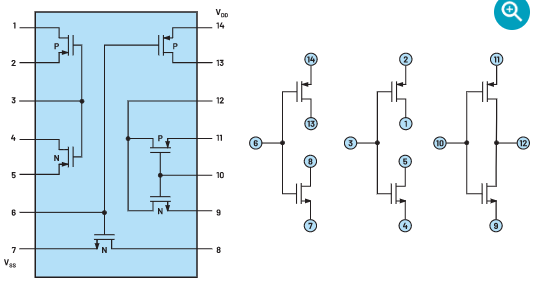

CMOS通过晶体管的不同组合,构建起基础的逻辑功能:

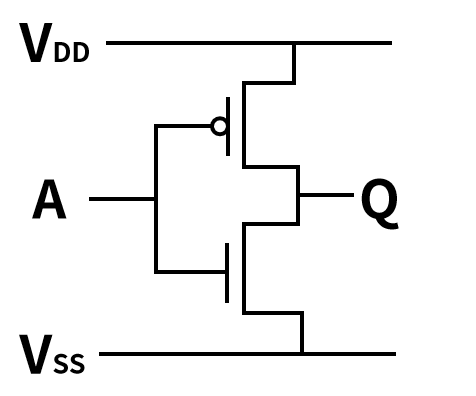

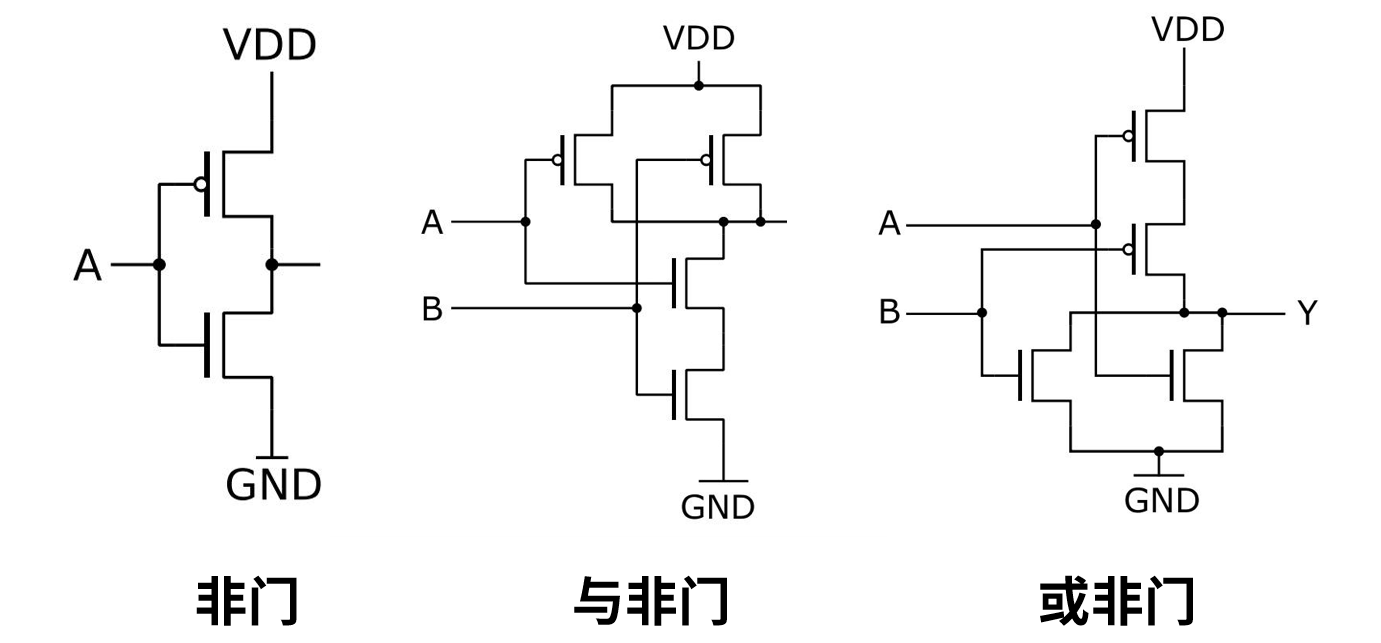

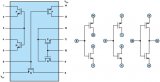

非门(反相器):当输入高电平时,NMOS导通,而PMOS截止,输出低电平;输入低电平的时候则相反,输出接高电平。无论输入高或低,只有一个管导通,且没有直流的通路,静态时几乎为0功耗。

与非门(NAND):当两个输入信号都是高电平时,串联的NMOS将输出牢牢拉向低电平;只要任一输入为低,并联的PMOS立即将输出推回高电平。这种"全高得低,有低得高"的特性,帮助处理器解码指令。

或非门(NOR):任一输入是高电平时,并联的NMOS将输出下拉至低;只有当所有输入归零,串联的PMOS才会输出高电平。这种设计常在内存存取控制看见。

CMOS的电路设计挑战

CMOS电路设计的物理挑战两个,一个是尺寸缩小后短沟道电场渗透、漏电流导致静态功耗高等问题。而在实际应用中,CMOS电路面临着功耗控制、噪声与信号完整等挑战:

功耗控制挑战:高频应用如手机处理器中,其开关损耗会伴随频率变化,而线性增加,进一步会加强芯片发热。而MOS管的低漏电流,可以降低处理器静态时的能耗损失,由此增强续航。

信号传输完整和速度:电路的布线密度高,相邻的电容、电感耦合会产生信号的干扰。如数据中心中的信号传输,要求兆赫兹级别的开关频率。

电源噪声:工厂电机开启和关闭的时候,电源电路的变化导致电压的波动,进而产生噪声。如MOS管HKTQ50N03通过稳定噪声的容限,从而控制信号的准确与可靠性。

这些特性让CMOS可以运用在很多电路上,智能手环通过微型与非门的阵列去处理传感器的信号;电动汽车控制器用或非门的阵列来管理电池状态;甚至在卫星通信的设备当中,数百万个逻辑门就在方寸之间完成数据的编码和解码。

结语

CMOS逻辑门的性能需要每个晶体管的高品质决定。其中的PMOS需要有高正电压响应的能力,NMOS则需要具备快速导通的特性,这两者还需要在毫秒级的开关当中进行协同。这对MOS管提出了更高的要求和稳定性表现。深耕半导体领域数十年的合科泰,正以此为目标精进MOS管技术。

审核编辑 黄宇

-

CMOS

+关注

关注

58文章

6190浏览量

241594 -

逻辑门

+关注

关注

1文章

156浏览量

26096

发布评论请先 登录

CMOS的逻辑门如何应用在电路中

CMOS的逻辑门如何应用在电路中

评论