电子发烧友网报道(文/李弯弯)近日消息,英特尔与软银集团宣布达成战略合作,共同开发具有划时代意义的AI专用内存芯片。这项合作将致力于突破当前AI计算中的能耗瓶颈,有望将芯片功耗降低50%,为全球AI基础设施建设带来革命性变化。

随着AI技术的快速发展,高性能、低功耗的计算硬件需求日益增长。然而,现有的AI内存技术存在高成本、高功耗及发热问题,限制了AI数据中心的进一步扩展和效率提升。据悉,软银与英特尔将研发一种创新的堆叠式DRAM芯片,采用全新的布线架构,完全不同于现有高带宽内存(HBM)技术方案。

这种新型AI内存芯片可能在哪些方面进行创新呢?首先,在架构层面,现有HBM技术主要采用TSV(硅通孔)垂直互连技术实现芯片堆叠,而创新方案采用全新布线架构,可能突破传统TSV的布局限制,通过更优化的布线设计减少信号传输路径的曲折和干扰,从而降低信号延迟和功耗。例如,可能采用新的层间互连方式,使数据在芯片堆叠层之间的传输更加直接高效。

HBM通过宽接口和并行传输实现高带宽,创新方案可能进一步优化通道数量和数据接口设计。比如增加通道数量,或者改进数据接口的信号传输机制,提高数据传输的效率和稳定性,在相同甚至更低的功耗下实现更高的带宽。

在芯片堆叠与封装层面,不同于HBM的堆叠方式,创新方案可能采用全新的芯片堆叠结构,提高堆叠密度和稳定性。例如,采用更紧密的堆叠方式,减少芯片之间的间隙,从而降低整体封装尺寸和信号传输距离。

还可以通过改进封装技术,提高芯片的散热性能和电气连接可靠性。例如,采用更高效的散热材料和封装结构,及时将芯片产生的热量散发出去,避免因过热导致的性能下降和功耗增加;同时,优化芯片与封装基板之间的电气连接,降低连接电阻,减少功耗。

据称,英特尔与软银这种突破性设计不仅大幅提升能效比,更将为AI数据中心的绿色转型提供关键技术支持。业内专家指出,该技术若能成功商业化,将显著降低AI计算的运营成本,对推动可持续发展具有重要意义。

为推进这一重大项目,双方联合成立了专门公司Saimemory,负责芯片的设计和专利管理。制造环节则委托专业代工厂完成,这种分工协作模式有望最大化研发效率。研发团队将采用不同于现有HBM技术的布线方式,通过垂直堆叠多颗DRAM芯片,并改进芯片间的互连技术,实现至少大一倍的存储容量,同时将耗电量减少40%以上。

根据项目规划,研发团队将在两年内完成芯片原型设计,之后启动量产评估程序,目标是在本世纪二十年代末实现商业化应用。项目总投资额预计达100亿日元(约合5亿元人民币),其中软银作为领投方已承诺注资30亿日元(约1.5亿元人民币)。

不过,尽管软银与英特尔在芯片设计和制造方面拥有丰富的经验和技术积累,但新型AI内存芯片的研发仍面临诸多技术挑战,如这种创新的式DRAM芯片的良率控制、量产成本能否真正低于HBM等。

当然,随着AI技术的广泛应用和数据中心规模的不断扩大,高性能、低功耗的内存技术需求将持续增长。如果新型AI内存芯片能够成功商业化并满足市场需求,将具有广阔的市场前景和商业价值。

-

DRAM

+关注

关注

41文章

2402浏览量

189573 -

HBM

+关注

关注

2文章

434浏览量

15884

发布评论请先 登录

低功耗DRAM可靠存储解决方案

不同于HBM垂直堆叠,英特尔新型内存ZAM技术采用交错互连拓扑结构

消息称英伟达HBM4订单两家七三分,独缺这一家

创新的高带宽DRAM解决方案

Kioxia研发核心技术,助力高密度低功耗3D DRAM的实际应用

SK海力士HBS存储技术,基于垂直导线扇出VFO封装工艺

HBM技术在CowoS封装中的应用

新思科技UCIe IP解决方案实现片上网络互连

突破堆叠瓶颈:三星电子拟于16层HBM导入混合键合技术

简单认识高带宽存储器

美光12层堆叠36GB HBM4内存已向主要客户出货

芯片晶圆堆叠过程中的边缘缺陷修整

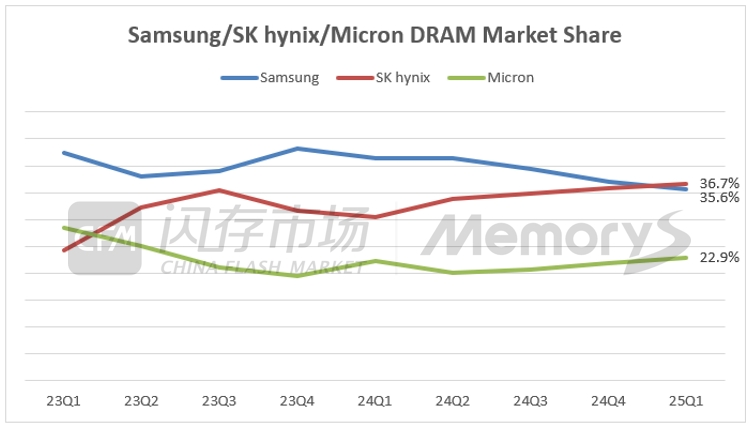

HBM重构DRAM市场格局,2025年首季DRAM市占排名

不同于HBM,这种创新的堆叠式DRAM,功耗有望降低50%

不同于HBM,这种创新的堆叠式DRAM,功耗有望降低50%

评论