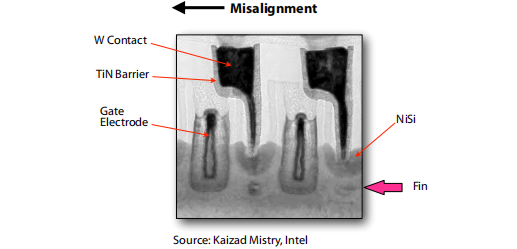

源漏区的单晶硅和栅极上的多晶硅即使在掺杂后仍然具有较高的电阻率,自对准硅化物(salicide)工艺能够同时减小源/漏电极和栅电极的薄膜电阻,降低接触电阻,并缩短与栅相关的RC延迟。另外,它避免了对准误差,从而可以提高器件集成度。由于自对准硅化物直接在源漏区和栅极上形成,CMOS 器件的微缩对自对准硅化物工艺有深远的影响。

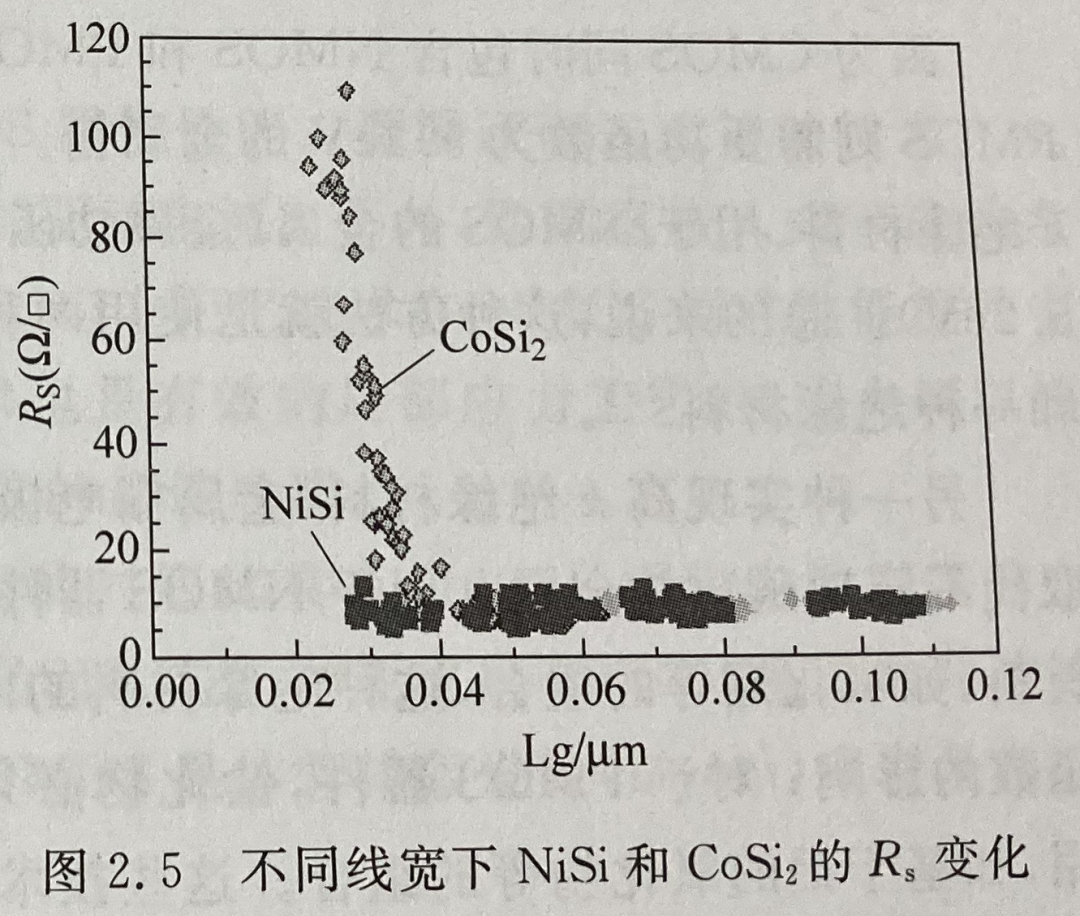

工业界最初采用TiSi2作为标准的硅化物材料,主要应用于0.35μm 和0.25μm 技术节点。在TiSi2工艺中,由高电阻的C49相形成低电阻的C54相的过程与线宽有关。更短的栅使得从C49晶粒相到C54相是一种一维生长模式,这种相变需要更高的温度,因此可能导致结块并会增加窄线的RS。由于窄线条效应限制,在0.18μm 技术代 Salicide 工艺使用CoSi2取代TiSi2。

如图 2.5所示,当线条物理宽度小于40nm 时,CoSi2在多晶硅上的薄层电阻迅速变高,而 NiSi即使到30nm以下,其电阻率仍保持在较低水平。另外,NiSi工艺中退火温度更低,因此具有热预算方面的优点;同时NiSi的硅消耗相比 CoSi2,工艺降低35%左右。这对于超浅结技术来说是一个非常重要的优点。综上所述,在90nm 和 65nm 技术节点,NiSi 工艺取代CoSi2,工艺。

需要注意的是,NiSi 的热稳定性相对较差,在高于600°C时,低阻态的NiSi会转变为高阻态的NiSi2相,这一点,在工艺整合中非常关键。同时,NiSi需要采用新的RTP 工艺技术,如尖峰退火技术(spikeanneal)或者毫秒级退火技术(MSA),在有效地形成硅化物的基础上,避免Ni在界面上的扩散,从而降低漏电流。

-

CMOS

+关注

关注

58文章

6186浏览量

241581 -

工艺

+关注

关注

4文章

708浏览量

30111 -

栅极

+关注

关注

1文章

187浏览量

21627

原文标题:自对准硅化物工艺

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

半导体制造的合金化热处理工艺

集成电路芯片制造中的3种硅化物工艺介绍

自对准硅化物 (Self -Aligned Silicide) 工艺

半导体行业之刻蚀工艺技术

IBC技术新突破:基于物理气相沉积(PVD)的自对准背接触SABC太阳能电池开发

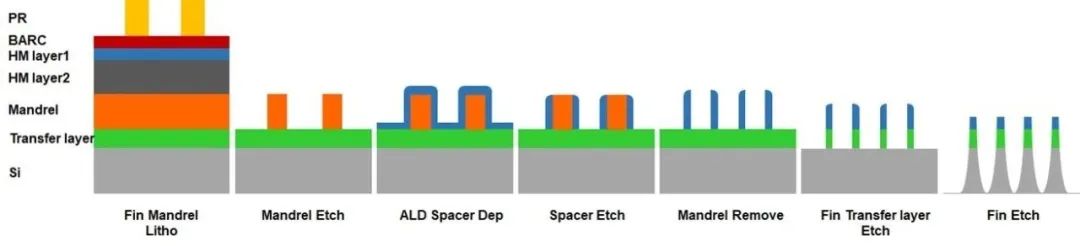

自对准双重图案化技术的优势与步骤

半导体中的合金制备技术详解

自对准硅化物工艺详解

自对准硅化物工艺详解

评论