自对准硅化物 (Self -Aligned Silicide) 工艺

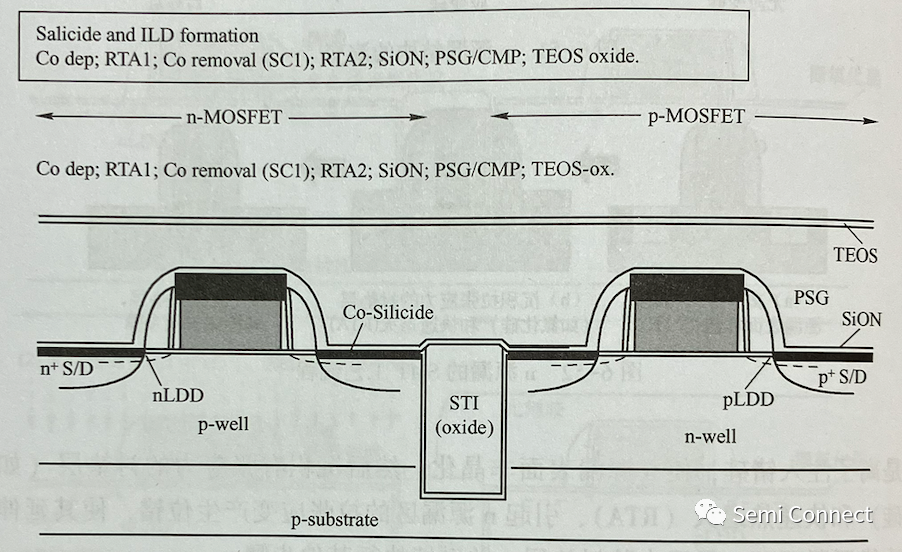

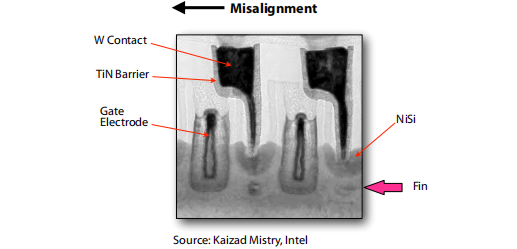

传统的 CMOS 工艺(如32nm或更早的节点上)是基于氧化硅/多晶硅结构形成源漏的(即非 HKMG 和非应变源漏的工艺流程),因此称为先栅 ( Gate-First)工艺。在有源区和多晶硅栅区多采用同时形成硅化物的自对准技术,如图所示。

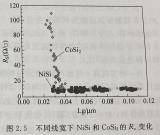

形成多晶硅栅和源漏之后,先用湿法或干法清除在有源区 (AA)和多晶硅栅表面的氧化物,溅射一薄层(厚度范围 10~20nm)金属(钴Co 或镍Ni),紧接着进行第1次 RTA(温度范围为 400-550°C),与硅接触的金属发生反应形成金属硅化物(Metal Silicide)。然后,用 SC1 溶剂去掉氧化硅上剩余的未参与反应的金属,并进行第2 次RTA(温度约为 700°C),在有源区和多晶硅栅区域上留有金属硅化物,这一过程被称为自对准硅化物工艺。之后,沉积氮氧硅和磷硅玻璃(PSG),并用CMP 进行平坦化,再沉积一层 CVD 氧化物(TEOS-ox)来密封 PSG,形成栅-金属层间介质 (Inter-Layer Dielectrie, ILD)。

审核编辑 :李倩

-

CMOS

+关注

关注

58文章

6186浏览量

241576 -

多晶硅

+关注

关注

3文章

249浏览量

30519

原文标题:中段集成工艺(MOL Integration Flow)- 1

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

半导体中的合金制备技术详解

芯片制造中的对准技术详解

lt4363的手册中提到的self enhancement of the N-channel MOSFET到底是什么含义?

微流控芯片的封合工艺有哪些

自对准硅化物工艺详解

自对准双重图案化技术的优势与步骤

IBC技术新突破:基于物理气相沉积(PVD)的自对准背接触SABC太阳能电池开发

TRCX应用:显示面板工艺裕量分析

DLP4500的内参数和畸变系数的相对准确的值是多少?

单晶圆系统:多晶硅与氮化硅的沉积

Techwiz LCD 3D应用:基板未对准分析

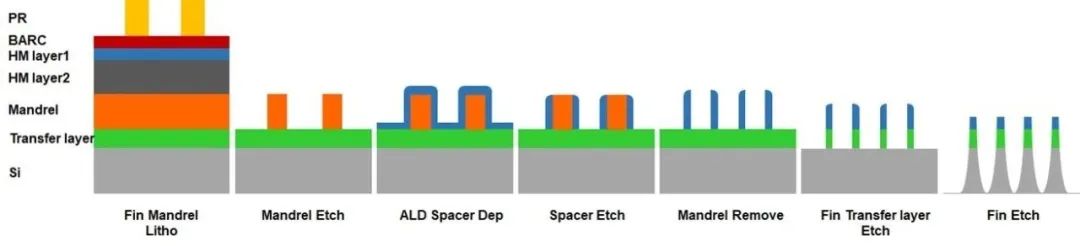

FinFet Process Flow—哑栅极的形成

自对准硅化物 (Self -Aligned Silicide) 工艺

自对准硅化物 (Self -Aligned Silicide) 工艺

评论