文章来源:半导体与物理

原文作者:jjfly686

本文介绍了自对准双重图案化技术的优势与步骤。

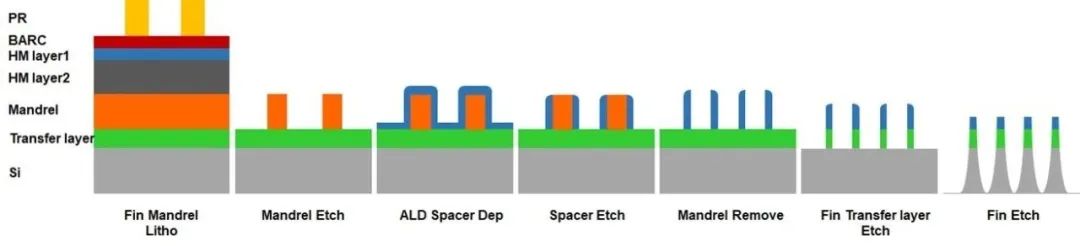

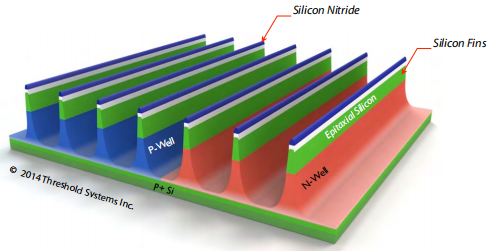

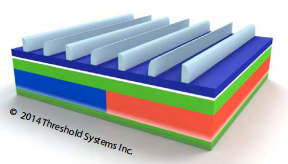

在芯片制造中,光刻技术在硅片上刻出纳米级的电路图案。然而,当制程进入7纳米以下,传统光刻的分辨率已逼近物理极限。这时,自对准双重图案化(SADP)的技术登上舞台,氧化物间隔层切割掩膜,确保数十亿晶体管的精确成型。

光刻的困境

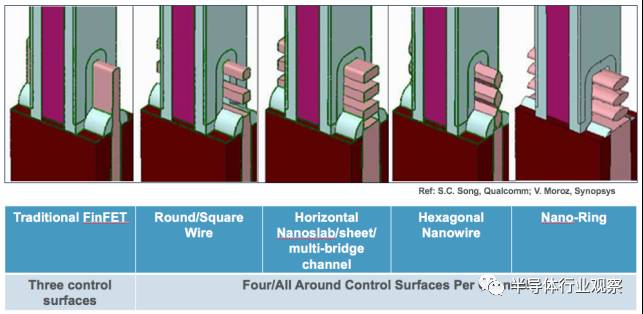

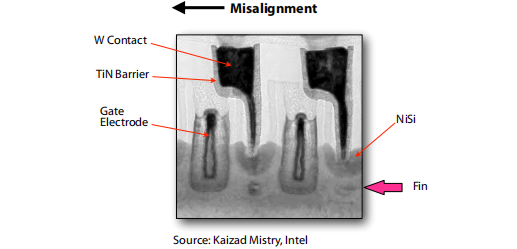

传统光刻机使用193 nm波长的深紫外光(DUV),理论上最小只能刻出约50 nm宽的线条。但现代5纳米芯片的晶体管鳍片(Fin)宽度已缩至10 nm,这相当于要用一把“钝刀”刻出比刀刃更细的纹路。

SADP技术的突破:通过两次图案化,将光刻分辨率提升一倍。其核心在于利用氧化物间隔层(Oxide Spacer)作为“模板的模板”,但若不对间隔层进行精细修剪,最终结构可能扭曲变形。

SADP技术

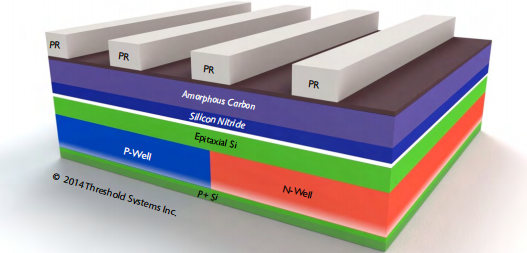

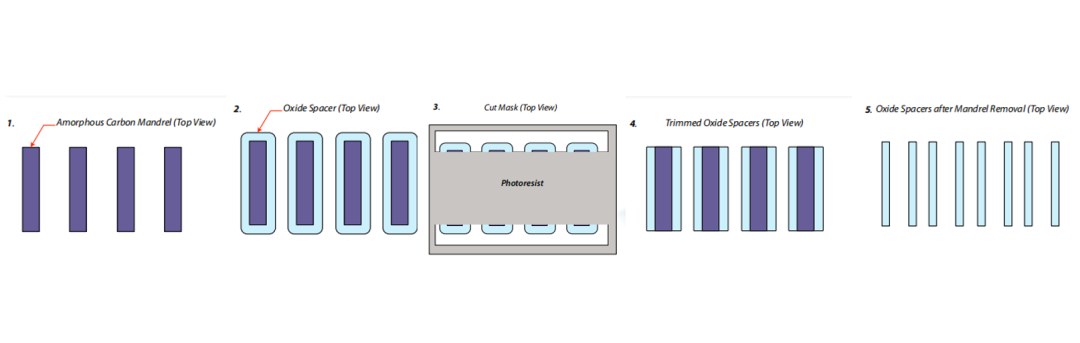

1.第一步:制作核心模板(Mandrel)

材料选择:无定形碳膜因其易刻蚀、耐高温,成为理想模板材料。光刻成型:在硅片上涂覆光刻胶,曝光显影后刻蚀出初始线条。

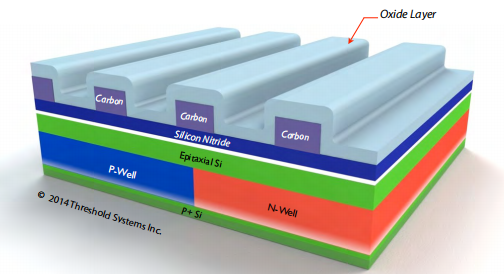

2.第二步:包裹氧化物间隔层

沉积工艺:通过原子层沉积(ALD)在碳模板两侧包裹一层均匀的二氧化硅(SiO₂),厚度精确控制。去除核心:用氧等离子体刻蚀掉中间的碳模板,留下成对的氧化物间隔层,间距缩小至目标尺寸。

3.缺陷

若不对间隔层两端进行修剪,后续刻蚀硅形成鳍片时,边缘会因应力不均变成椭圆形。

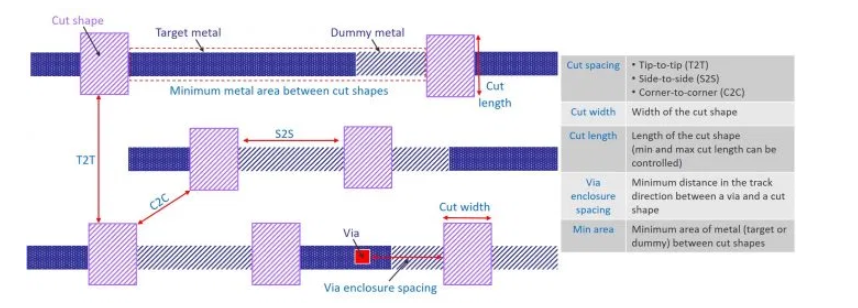

4.切割掩膜

为了将弯曲的间隔层变成笔直的线条,工程师引入切割掩膜(Cut Mask)技术:

1.光刻定位:在间隔层两端涂覆光刻胶,通过光刻机曝光,定义需要修剪的区域。

2.刻蚀:用等离子体刻蚀精确切除间隔层两端多余部分,确保直线结构。

3.定向扩展:修剪后的间隔层作为硬掩膜,刻蚀下方的硅衬底,形成笔直的鳍片阵列。

-

芯片制造

+关注

关注

11文章

711浏览量

30326 -

光刻技术

+关注

关注

1文章

151浏览量

16461

原文标题:双重图案化掩膜层

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

12:1 DC/DC转换器兼具技术上和商业上的双重优势(上)

12:1 DC/DC转换器兼具技术上和商业上的双重优势(下)

基于DCT和混沌的双重图像水印算法

引入 FinFET晶体后的多重图案拆分布局和布线

关于FinFET与集成电路的对比分析介绍

SEMulator3D能提供哪些功能?

双重图形化技术(Double Patterning Technology,DPT)

ASML考虑推出通用EUV光刻平台

IBC技术新突破:基于物理气相沉积(PVD)的自对准背接触SABC太阳能电池开发

基于激光掺杂与氧化层厚度调控的IBC电池背表面场区图案化技术解析

自对准硅化物工艺详解

自对准双重图案化技术的优势与步骤

自对准双重图案化技术的优势与步骤

评论