概述

DS4510是CPU监控电路,具有内部集成的64字节EEPROM存储器和四个可编程的非易失性(NV) I/O引脚。它配备了工业标准I²C接口,使用快速模式(400kbps)或标准模式(100kbps)进行通信。I/O引脚可以用作通用I²C至并行I/O扩展器,具有无限制读写的能力。EEPROM寄存器允许调节I/O引脚的上电值,由此在上电过程跟踪系统的状态。该CPU监控器的定时器可以在125ms至1000ms之间调整以满足大多数应用的需要。

数据表:*附件:DS4510 CPU监控电路,具有非易失存储器和可编程输入 输出技术手册.pdf

应用

特性

- 5V电源精确的5%、10%或15%门限值监视

- 在V

CC返回容限范围后,可编程的复位定时器将维持复位状态 - 具有可选择内部上拉电阻的四个可编程、NV、数字I/O引脚

- 64字节的用户EEPROM

- 减少了对分立元件的需求

- I²C兼容的串行接口

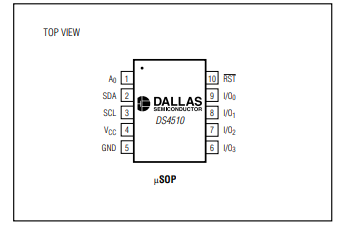

- 10引脚µSOP封装

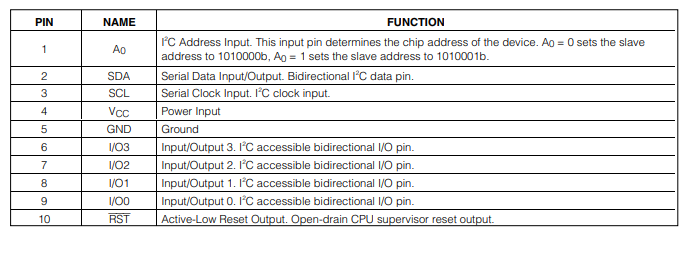

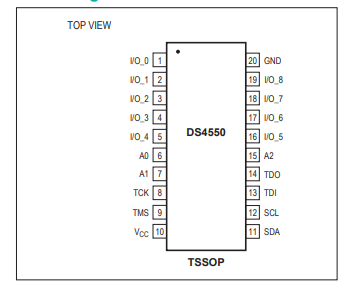

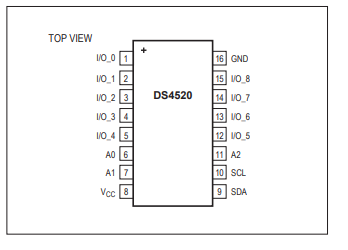

引脚配置描述

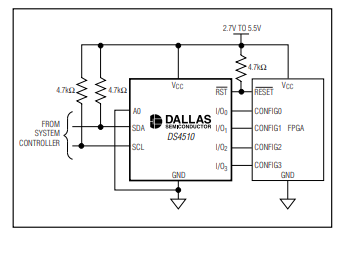

操作电路

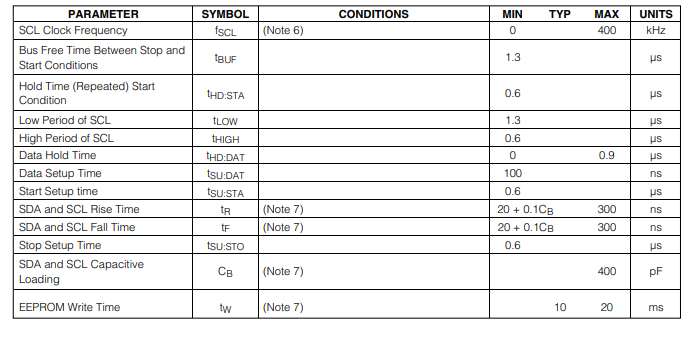

交流电气特性

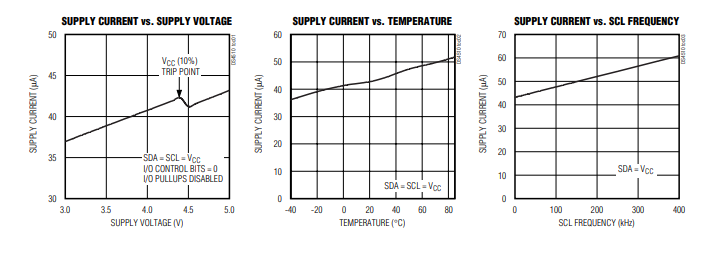

典型操作特性

详细说明

DS4510 包含一个 CPU 监控器、四个可编程 I/O 引脚以及一个 64 字节的 EEPROM 存储器。所有功能均可通过业界标准的 I²C 兼容总线进行配置和控制。DS4510 的非易失性寄存器采用 SRAM 映射的 EEPROM(即影子 EEPROM)实现。该存储器可配置为作为易失性 SRAM 或非易失性 EEPROM 运行,通过调整配置寄存器(SEEPROM)中的 SEE 位来实现。将这些寄存器配置为 SRAM 可消除 EEPROM 写入时间,并允许对这些寄存器进行无限次循环写入。将寄存器配置为 EEPROM 可让应用程序更改上电时调用的电源电平值。

可编程 CPU 监控器

通过向复位延迟寄存器(EEPROM)写入来调整超时周期。AC 电气特性中给出了每个设置的延迟时间。如果设置了 SEE 位,更改将写入 SRAM。在上电时,最后一个值也会写入 EEPROM 中。I²C 总线用于通过设置配置寄存器中的 SWRT 位来激活 RST 引脚。超时周期结束后,该位会自动复位为零。配置寄存器还包含就绪位、阈值点和复位状态位。就绪位用于判断 DS4510 的上电复位电平是否被 VCC 超过。阈值点用于判断 VCC 是否高于 VCTP。如果 RST 处于有效状态,则设置复位状态位。

注意:RST 引脚为集电极开路输出,因此需要一个外部上拉电阻,以实现高逻辑电平。

可编程非易失性数字 I/O 引脚

每个可编程 I/O 引脚都包含一个输入、一个集电极开路输出以及一个可选择的内部上拉电阻。DS4510 将 I/O 引脚的更改存储在 EEPROM 存储器中。将 SEEPROM 用作 SRAM 对应用程序有益,因为 I/O 扩展通常需要快速访问时间和对 I/O 引脚进行频繁修改。配置 SEE 位以在 EEPROM 模式下运行,可允许更改 I/O 引脚的上电状态。上电时,I/O 引脚为高阻抗状态,直到 VCC 超过 2.0V(典型值),此时从 EEPROM 中调用最后一个值。掉电时,I/O 状态由 VCC 降至 1.9V(典型值)来维持。

I/O 引脚的内部上拉电阻由上拉使能寄存器(F0h)控制。同样,各个 I/O 控制寄存器(F4h 至 F7h)用于调整下拉电阻。

-

存储器

+关注

关注

39文章

7753浏览量

172156 -

EEPROM

+关注

关注

9文章

1146浏览量

86322 -

DS4510

+关注

关注

0文章

3浏览量

5613

发布评论请先 登录

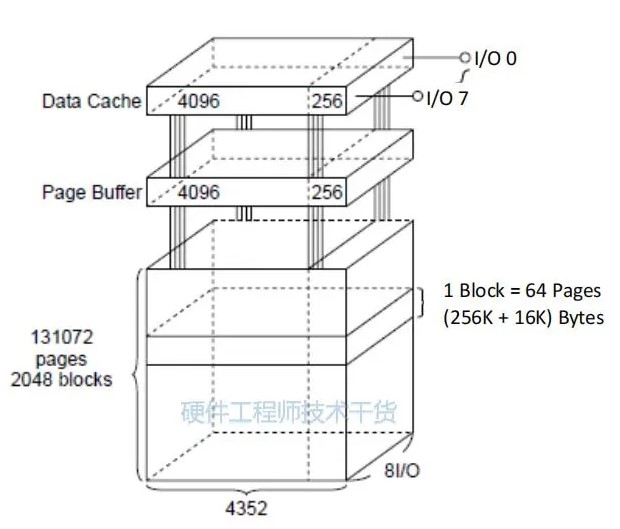

NAND Flash非易失存储器简介

具有多种可编程性的易失性存储器数字电位器

FPGA零基础学习:半导体存储器和可编程逻辑器件简介

可编程非易失(NV)存储器的质询-响应安全认证IC DS28

高度集成、10位可编程gamma和VCOM基准系统,带有非易

Mbit非易失性静态随机访问存储器nvSRAM系列

LTC2936:带电可编程只读存储器和比较器输出的可编程祸不单行电压监控器数据表

DS4510 CPU监控电路,具有非易失存储器和可编程输入/输出技术手册

DS4510 CPU监控电路,具有非易失存储器和可编程输入/输出技术手册

评论