概述

DS4520是9位非易失(NV) I/O扩展器,具有通过I²C兼容的串行接口控制的64字节NV用户存贮器。与用来控制数字逻辑节点的硬件跳线和机械开关相比,DS4520为用户提供了数字可编程的替代方案。并且,每一个引脚的数字状态可以通过串行接口读取。每一个I/O引脚都是独立配置的。输出是开漏极输出,并具有可选的上拉。每一个输出都能吸收12mA的电流。因为设备是NV的,它可以一上电就处于期望的状态,从而能够在上电之后立即控制数字逻辑输入,而不用等待主机CPU来初始化控制。

数据表:*附件:DS4520 9位、I²C、非易失、输入 输出扩展器与存储器技术手册.pdf

应用

特性

- 机械跳线和开关的可编程替代品

- 九个NV输入/输出引脚

- 64字节NV用户存储器(EEPROM)

- 兼容I²C的串行接口

- 最多8个器件可以在同一I²C总线上工作

- 具有可配置上拉的开漏极输出

- 输出能吸收12mA电流

- 低功耗

- 宽工作电压范围(2.7V至5.5V)

- 工作温度范围:-40°C至+85°C

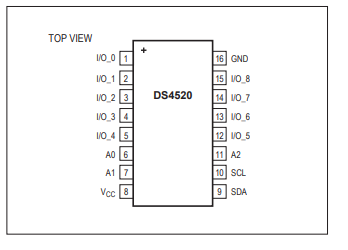

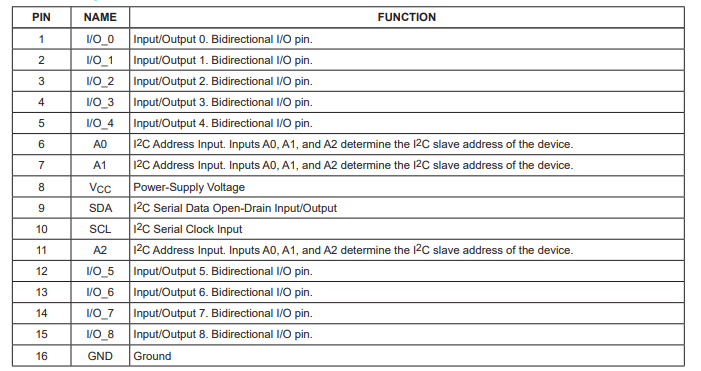

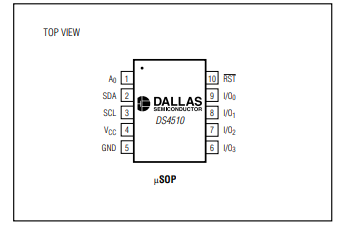

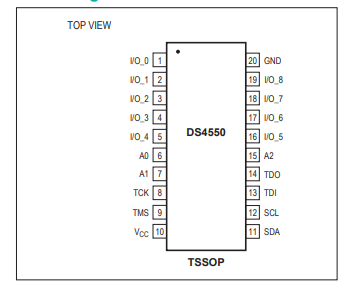

引脚配置描述

交流电气特性

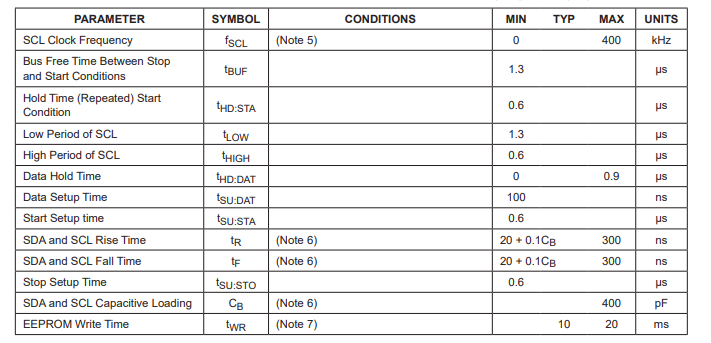

典型操作特性

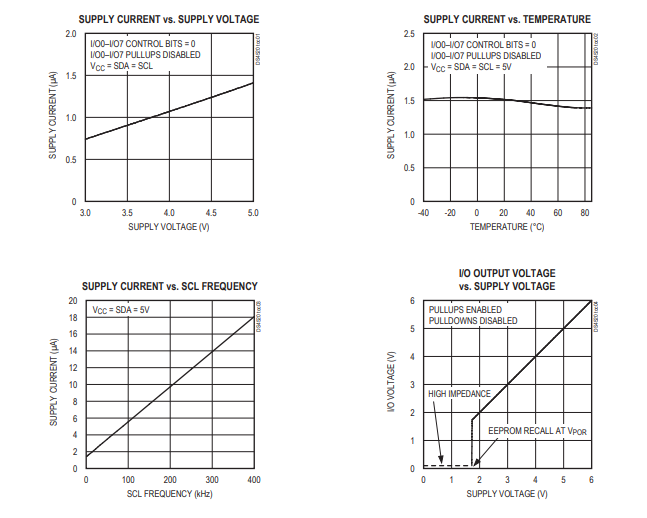

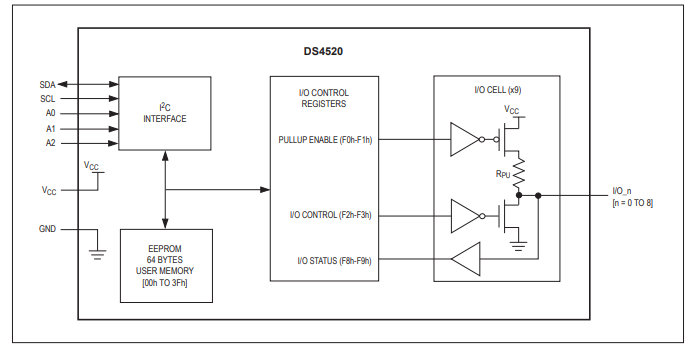

框图

详细说明

DS4520 包含九个双向、非易失性(NV)输入/输出(I/O)引脚,以及一个 64 字节的 EEPROM 用户存储器。I/O 引脚和用户存储器可通过 I²C 兼容串行总线进行访问。

可编程非易失性 I/O 引脚

每个可编程 I/O 引脚由一个输入和一个集电极开路输出组成,带有一个可选择的内部上拉电阻。要为每个 I/O 引脚启用上拉功能,请写入上拉使能寄存器(F0h 和 F1h)。要将输出拉低,或将下拉晶体管置于高阻抗状态,请写入 I/O 控制寄存器(F2h 和 F3h)。要读取 I/O 引脚上的电压电平,请读取 I/O 状态寄存器(F8h 和 F9h)。要确定输出的状态,请读取 I/O 控制寄存器和上拉电阻寄存器。I/O 控制寄存器和上拉使能寄存器均为 SRAM 映射的 EEPROM 寄存器。可以使用配置寄存器中的 SEE 位禁用寄存器的 EEPROM 写入操作。这样做可以减少写入寄存器所需的时间,并且增加在 EEPROM 磨损之前可对 I/O 引脚进行调整的次数。

内存映射与内存类型

DS4520 的内存映射见表 1。DS4520 中有三种不同类型的内存:EEPROM、SRAM 映射 EEPROM 和 SRAM。指定为 EEPROM 的内存位置是非易失性的。向这些位置写入内容会在 EEPROM 写入周期中产生两次写入操作,其时间特性如“AC 电气特性”表中所示。指定为 SRAM 映射 EEPROM 的位置可通过配置寄存器(最低有效位为 F4h)中的 SEE 位配置为在两种模式下运行。当 SEE 位为 0(默认值)时,该内存位置的行为类似于 EEPROM。然而,当 SEE 位为 1 时,会写入影子 SRAM 而非 EEPROM。这消除了 EEPROM 写入时间(tWR)的问题,同时也消除了 EEPROM 磨损的问题。这对于需要频繁更新 I/O 引脚的应用来说是理想的选择。上电默认状态下,I/O 引脚配置写入 EEPROM(SEE = 0),上电后,可将 SEE 位写为 1,这样 I/O 引脚就能定期更新到影子 SRAM。DS4520 中存在的最后一种内存类型是标准 SRAM。

从机地址和地址引脚

DS4520 的从机地址由图 1 中所示的 A0、A1 和 A2 地址引脚的状态决定。连接到 VCC 的地址引脚会在从机地址的相应位位置产生“1”。反之,连接到 GND 的地址引脚会在从机地址的相应位位置产生“0”。I²C 通信中的从机地址将在后面的 I²C 串行接口描述部分进行说明。

I²C 串行接口描述

I²C 定义

以下术语常用于描述 I²C 主设备:

- 主设备:主设备控制总线上的从设备。主设备生成 SCL 时钟脉冲,启动和停止通信。

- 从设备:从设备在主设备的请求下发送和接收数据。

- 总线空闲或非忙状态:停止条件和开始条件之间的时间,此时 SDA 和 SCL 均为高电平逻辑状态。当总线空闲时,它通常会为从设备启动低功耗模式。

- 开始条件:开始条件由主设备生成,用于启动与从设备的数据传输。主设备在保持 SCL 高电平的同时将 SDA 从高电平转换为低电平,以生成开始条件。有关适用的定时,请参见定时图。

- 停止条件:停止条件由主设备生成,用于结束与从设备的数据传输。主设备在保持 SCL 高电平的同时将 SDA 从低电平转换为高电平,以生成停止条件。有关适用的定时,请参见定时图。

- 重复开始条件:主设备可在一次数据传输结束时使用重复开始条件,以表明它会立即启动新的数据传输。重复开始条件通常在读取操作期间用于标识特定内存地址,以启动数据传输。正常的重复开始条件在总线空闲时发出。有关适用的定时,请参见定时图。

- 位写入:在 SCL 为低电平状态期间,SDA 上的数据必须保持不变。在 SCL 的上升沿期间,数据进入高电平脉冲加上建立和保持时间要求(见图 2)。在 SCL 的下降沿,设备会在 SCL 为低电平时读取数据。

-

存储器

+关注

关注

39文章

7757浏览量

172209 -

扩展器

+关注

关注

0文章

169浏览量

16274

发布评论请先 登录

探索DS3502:高电压非易失性I²C数字电位器的卓越性能

DS1804非易失性微调电位器:特性、操作与应用解析

探索MAXIM DS1314:3V非易失性控制器的技术奥秘

深入剖析DS1312非易失性控制器:功能特性与设计要点

SGM4593:低电压16位I²C和SMBus低功耗I/O扩展器的深度解析

SGM4594:低电压16位I²C和SMBus低功耗I/O扩展器的全面解析

深入解析PCF8575:16位I²C与SMBus I/O扩展器的卓越之选

TCA6408A:低电压8位I²C和SMBus I/O扩展器的深度解析

TCA9555:低电压16位I²C和SMBus I/O扩展器的全面解析

深入解析 TCA9539:低电压 16 位 I2C 和 SMBus I/O 扩展器

TCA6424A:低电压24位I²C和SMBus I/O扩展器的深度解析

深入解析TCA9554:8位I²C和SMBus低功耗I/O扩展器

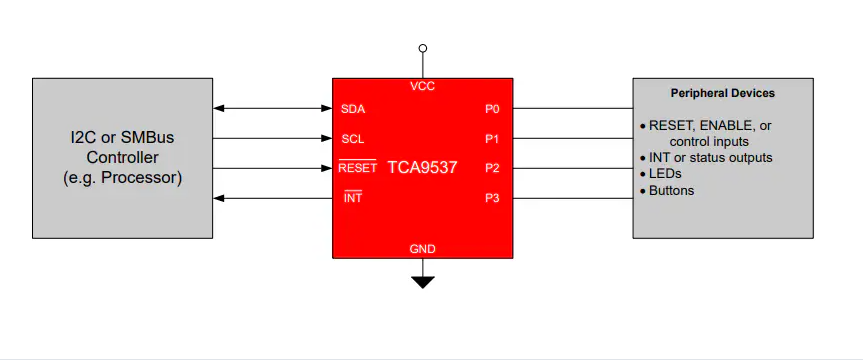

TCA9537远程4位I²C/SMBus I/O扩展器技术解析与应用指南

DS4520 9位、I²C、非易失、输入/输出扩展器与存储器技术手册

DS4520 9位、I²C、非易失、输入/输出扩展器与存储器技术手册

评论