文章来源:老千和他的朋友们

原文作者:孙千

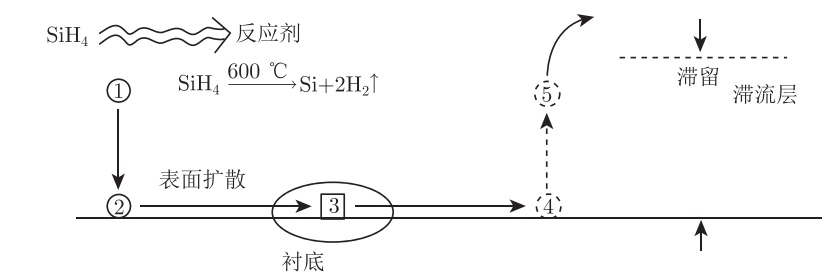

选择性外延生长(SEG)是当今关键的前端工艺(FEOL)技术之一,已在CMOS器件制造中使用了20年。英特尔在2003年的90纳米节点平面CMOS中首次引入了SEG技术,用于pMOS源/漏(S/D)应力器。它结合了抬升源/漏技术、凹槽刻蚀源/漏结形成技术以及硅锗(SiGe)局部沟道应变技术。然而,有关SEG的首次报道可追溯至61年前,即1962年德州仪器的Joyce和Baldrey在《自然》杂志上发表的文章。

引言

20世纪80年代,有超过120篇关于SEG(也称为选择性硅生长(SSG))在双极性、CMOS、BiCMOS和电荷耦合器件(CCD)新型器件结构中各种研发应用的出版物。应用材料公司的Borland在1987年IEEE国际电子器件会议(IEDM)和1987年10月电化学学会(ECS)化学气相沉积(CVD)-X研讨会上报道了SEG器件应用的综述。

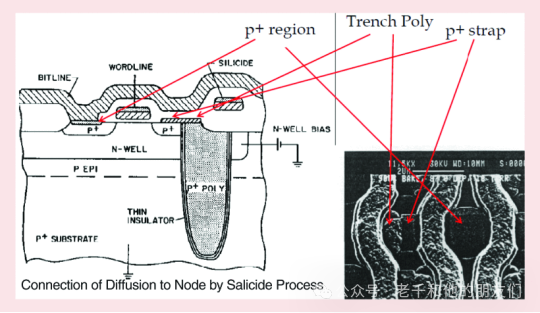

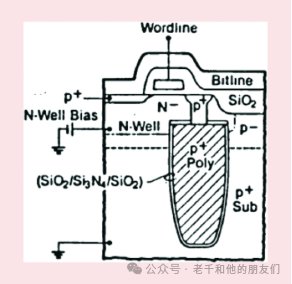

SEG首次大规模制造应用是由IBM/Burlington在1987年用于0.7微米技术节点的4兆动态随机存取存储器(DRAM)。如图1所示,SEG工艺是一种选择性硅表面带,连接DRAM多晶硅沟槽电容器与晶体管。

图1.1987年IBM 4兆位DRAM的选择性硅带

那年夏天,作者在佛蒙特州度过了一周美好时光,致力于SEG工艺研究。0.7微米技术节点的寿命很短,因为0.5微米节点的16兆DRAM在1988年就问世了,采用垂直侧壁多晶硅连接沟槽电容器。

直到16年后,SEG的第二次大规模制造应用才出现,那就是英特尔2003年的90纳米节点,它引入了局部应变硅技术,并使用凹槽刻蚀选择性SiGe抬升源/漏技术用于pMOS,如Ghani等人所报道的。eSiGe源/漏应力器技术在2011年22纳米节点的3D鳍式场效应晶体管(FinFET)中得以延续。

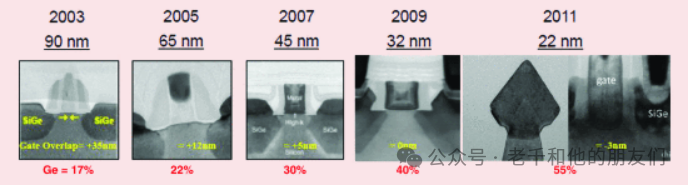

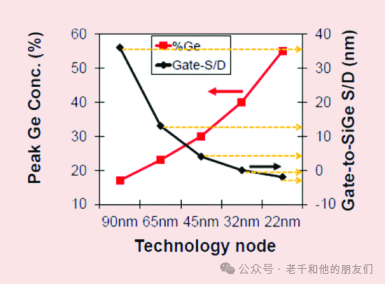

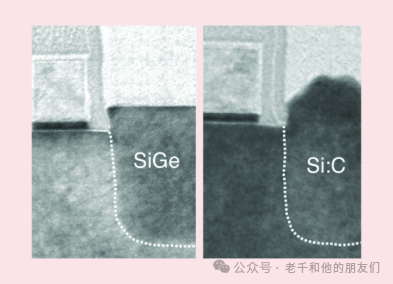

Borland在2016年11月日本学术振兴会第七届硅材料先进科学技术国际研讨会上的特邀报告"智能手机市场推动7纳米和5纳米节点3D器件和堆叠器件"展示了凹槽刻蚀选择性SiGe pMOS源/漏结构的透射电子显微镜(X-TEM)截面演变,从平面90纳米节点(17% SiGe,栅极重叠控制+35纳米)到鳍式22纳米节点(55% SiGe,栅极重叠控制-3纳米),如图2所示。

图2.从90纳米至22纳米节点的凹槽刻蚀选择性硅锗源/漏结构的X-TEM分析

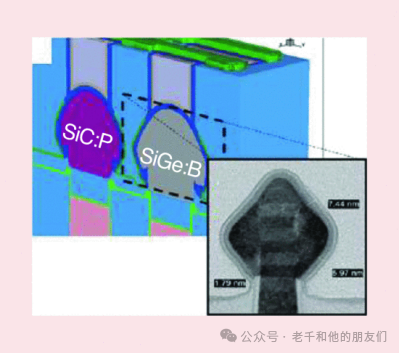

二十年后,选择性源/漏结构继续成为主流前端工艺,并演变为3纳米以下节点3D CMOS环绕栅极(GAA)纳米片器件的环绕接触(WAC),如IBM联盟的Loubert等人所报道,如图3所示。

图3.三维纳米薄片的选择性WAC

选择性WAC预计将使SEG技术在2030年代再延续十年,应用于3D堆叠CMOS器件,同时进行新材料改性研究以降低接触电阻。下面按照各个十年回顾SEG技术的一些关键开创性文章。

按十年代划分的SEG发展

1960年代

德州仪器的Joyce和Baldrey在1962年《自然》杂志上发表的题为"硅的选择性外延沉积"的文章中首次报道了使用SiCl₄在1200°C大气压下通过氧化物掩膜进行SEG。三年后,1965年,Jackson报道了向SiCl₄同时注入HCl,抑制在氧化物表面上的硅沉积。

1970年代

20世纪70年代有12篇SEG出版物,报道了其他用于选择性硅的源气体,包括SiH₄和硅-碘。Dumin在其文章"使用硅烷和锗烷的选择性外延"中报道了使用GeH₄源气体在800°C进行选择性锗生长;他报道在700°C时是非选择性的。西屋电气研发中心的研究人员Rai-Choudhury和Schroder报道了选择性砷化镓(GaAs)沉积。

1980年代

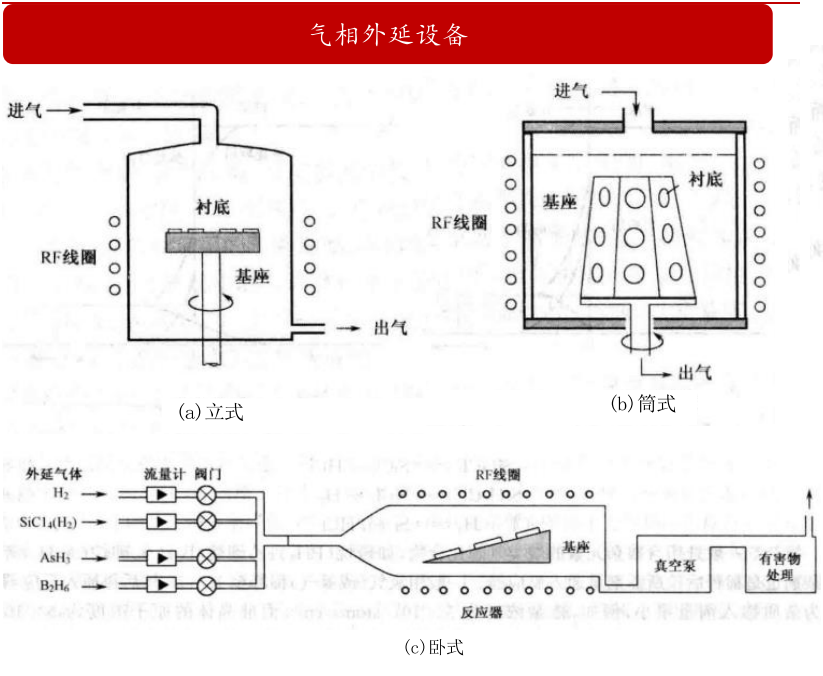

20世纪80年代的SEG出版物增加了10倍,达到120多篇,其中使用降低压力的CVD外延系统在较低温度下进行SEG的材料质量取得了突破。1982年,日本电气公司(NEC)的Tanno等人报道了在低于1000°C和80托压力下使用SiH₂Cl₂+HCl添加剂进行SEG以改善选择性。

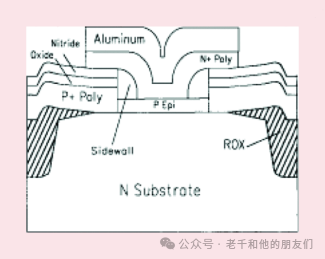

当时,工业界也正从双极性向CMOS和BiCMOS技术过渡。然而,IBM大型机仍然基于高速双极性技术。来自IBM约克镇高地的Burghartz等人在1988年5月《电子器件快报》(EDL)上报道了SEG首次用于双多晶硅自对准结构中的基极形成,题为"选择性外延基极晶体管(SEBT)",如图4所示。

图4.IBM用于高速双极型的选择性外延基极晶体管

IBM选择了Meyerson的超高真空/CVD外延方法。麻省理工学院的O等人在1987年5月ECS会议上报道了使用另外两个掩膜步骤与SEG的其他BiCMOS设计,将垂直NPN和PNP双极性晶体管插入p阱CMOS工艺流程。

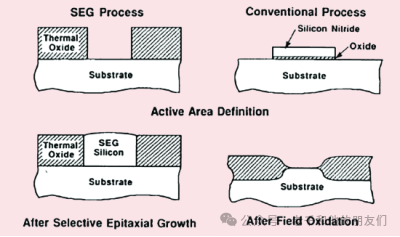

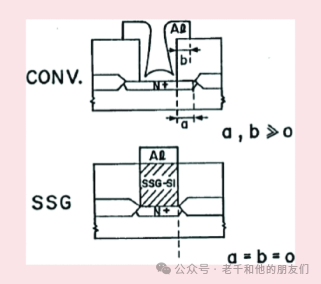

CMOS的引入面临的关键挑战之一是pMOS和nMOS器件隔离和闩锁效应预防。Borland在IEDM-1987的特邀演讲中回顾了SEG新型器件结构:1)横向器件隔离,2)用于n型和p型硅结构的选择性掺杂,3)抬升源/漏,4)接触填充,以及5)绝缘体上硅(SOI)的形成。

横向器件隔离:Borland和Drowley在应用材料公司和惠普实验室于1985年8月发表的《固态技术》文章中,回顾了替代局部硅氧化的先进介电隔离技术,包括SEG隔离,如图5所示。

图5.用于先进介质隔离的SEG

SEG侧壁面形成和缺陷出现在(110)侧壁上;然而,在(100)氧化物侧壁上实现了无面和无缺陷的SEG。SEG隔离工艺流程类似于今天我们所称的"鳍后工艺"(而非"鳍先工艺"),通过SEG在硅晶圆表面上方创建抬升的硅台结构。

浅沟槽隔离(STI)工艺在20世纪80年代末0.5微米技术节点引入,是相反的"鳍先"类工艺,通过台面刻蚀硅晶圆创建抬升的硅结构。它避免了在刻蚀损伤的硅表面上生长高质量SEG的困难、界面杂质和侧壁面形成/缺陷。

为了将SEG面形成/缺陷限制在n阱区域并将CMOS的横向隔离极限推至<0.25微米,来自NEC的Kasai等人在IEDM-1985上报告了一种4微米深、0.25微米宽的高纵横比SEG窄隔离结构,用于n阱CMOS,如图6所示。

图6.采用SEG的CMOS窄隔离间距

垂直侧壁上的氧化物厚度成为窄隔离宽度。单阱CMOS,无论是n阱(使用p型晶圆最常见)还是p阱(使用n型晶圆),主导了CMOS技术;只有少数公司使用双阱CMOS,如AT&T,提供了使用p型或n型晶圆的灵活性。将n型晶圆用于CMOS,特别是n/n+ epi晶圆,由于内在吸杂能力差而存在问题。

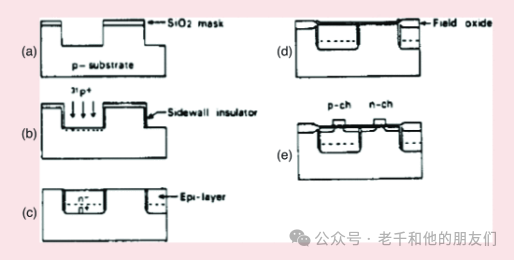

选择性掺杂:Manoliu和Borland在IEDM-1987上发表了一篇联合仙童研究和应用材料公司的论文,报告了用于n阱和p阱的有源区选择性掺杂,用于亚微米双阱CMOS,展示了优异的闩锁特性,无需深沟槽,如图7所示。双掩埋层形成了双阱逆向掺杂阱,并使用钛(Ti)进行硅化物接触。

图7.双埋层双阱CMOS

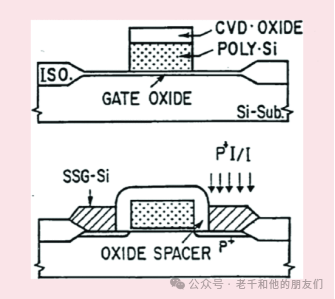

抬升源/漏:对于硅外延质量不重要的非有源器件区域,使用选择性硅或多晶硅沉积形成抬升源/漏结构。来自东芝的Hashimoto在1988年12月应用材料公司第三届年度先进器件结构外延技术创新研讨会上,展示了无掺杂SSG随后进行B注入的抬升源/漏,如图8所示。源/漏结是通过从注入的抬升源/漏结构中p+硼扩散形成的。

图8.东芝抬升源/漏结构

接触填充:Shibata等人来自东芝在1987年VLSI技术研讨会上报告了原位n+磷掺杂SEG用于接触填充。由于这是非有源器件区域,硅外延质量不重要,他们制造了1-Mb静态随机存取存储器(SRAM),具有平坦的金属接触,没有不共形金属键孔结构,用于改进自对准接触(SAC),如图9所示。

图9.用于平面SAC的原位掺杂n+ SSG

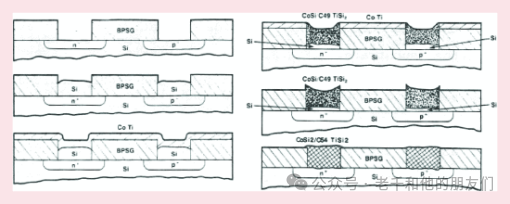

Wei等人在1989年ECS超大规模集成科学和技术研讨会和VMIC-89上发表了一篇英特尔和应用材料公司的联合论文,报告了另一种方法,使用接触硅化。他们报告使用无掺杂选择性硅插塞用于n+和p+接触填充,随后沉积钴(Co)或钛(Ti)并进行硅化,如图10所示。

图10.选择性硅接触填充,随后形成Co或Ti硅化物

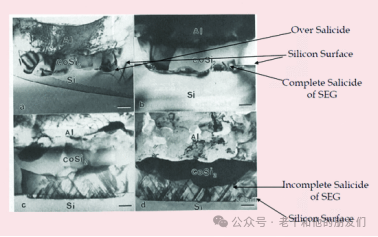

图11显示了过度硅化[图11(a)]、完美硅化[图11(b)]和不足硅化[图11(c)和(d)]的X-TEM结果。这种厚硅化物技术将成为21世纪开发的用于高k金属栅极(HK/MG)的FUSI栅极的前身。

图11.(a)–(d) SSG-SAC随后形成钴硅化物的X-TEM结果

SOI形成:Jastrzebski在1984年12月的《晶体生长杂志》中报告了横向生长SEG覆盖氧化物,称为外延横向超生长(ELO),形成局部SOI结构,并在图12中说明了用于双阱CMOS的应用。使用化学机械抛光(CMP),完全抛光回和SOI层变薄的ELO结构,不含任何表面面形成凹坑,如图13所示。

图12通过ELO形成SOI

图13CMP被用于抛光和减薄由ELO形成的SOI层

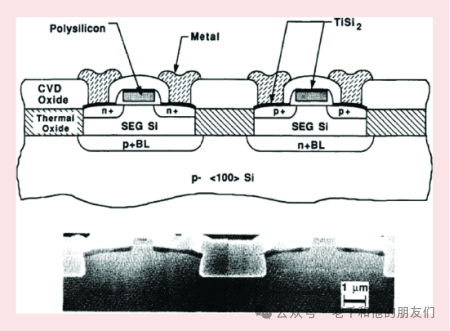

SEG DRAM沟槽电容器设计:从1-Mb DRAM 1.0微米技术节点开始,IBM自1985年以来一直使用多晶硅沟槽存储电容器单元设计。在1987年的4-Mb DRAM 0.7微米技术节点,他们使用选择性硅表面带随后进行硅化作为连接到沟槽存储电容器的局部互连,如图1所示。

SSG晶体结构在p+硅晶体管源/漏区域上是单晶的,在p+多晶沟槽电容器单元上方是多晶硅。IBM研究人员在1988年展示了各种设计选项,将SEG纳入潜在的0.35微米节点64-Mb DRAM及更高,包括使用沟槽上外延(EOT)设计的埋入式沟槽电容器,该设计结合了ELO和CMP平面化,如图14所示,由Lu和Bronner在1988年12月应用材料公司第三届年度先进器件结构外延技术创新研讨会上报告。

图14.选择性EOT DRAM

20世纪90年代

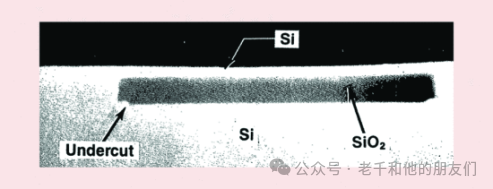

低温预SEG硅表面清洁和去除等离子体刻蚀损伤和残留物继续限制SEG在有源器件区域的应用。许多组织研究了减少厚氧化物刻蚀后残留刻蚀损伤和表面杂质的方法。牺牲氧化物最好能消耗残留刻蚀效应,而外延氢气烘烤步骤导致硅表面迁移/平滑,轻微的氧化物下切,以及氢表面钝化被证明对本征氧化物生长非常有抵抗力。从H2烘烤/退火步骤中学到的好处将用于其他工艺应用。

东芝陶瓷公司使用高温H2退火进行氢去核,并作为高质量Hi晶圆销售给半导体制造商,如1993年5/6月的《日经微器件》所报道。Gardner等人在1994年VLSI技术研讨会上发表了AMD和Genus的联合文章,题为"氢去核用于增强薄氧化物质量、器件性能和潜在外延消除"。

在2010年代,研究发现氢退火还能减少线边缘粗糙度,在硅侧壁刻蚀鳍和硅波导结构后导致硅表面平滑。HF蒸气刻蚀也被研究用于选择性氧化物刻蚀,作为独立和集成集群工具,但留下氟钝化表面,如Borland在1992年双极/BiCMOS电路和技术会议上报道和de Larios等人在1993年SSDM上报道。

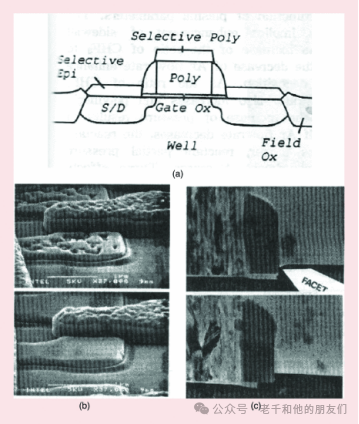

英特尔的Weldon等人在1994年5月ECS会议上报告了"使用选择性硅沉积的抬升源-漏用于亚半微米CMOS器件"。他们展示了表面预清洁处理对SEG抬升源/漏结构表面粗糙度和面形成的影响,如图15所示,轻微的源/漏下切消除了侧壁面。图15(a)说明了SEG抬升源/漏结构,显示源/漏区域上的选择性外延和栅极上的选择性多晶硅。图15(b)显示了n+源/漏区域的扫描电子显微镜表面形貌,对于900°C 1分钟H2烘烤显示点状SEG成核和生长,对于950°C 1分钟H2烘烤显示均匀SEG生长。图15(c)显示氧化物下切情况下没有侧壁面形成。

图15(a)–(c)预清洗处理后提高的源/漏(S/D)表面质量。

同时,对超浅结(USJ)形成也存在担忧。北卡罗来纳州立大学(NCSU)的一组研究人员,由Ozturk教授领导,在半导体研究公司-SEMATECH的资金支持下,研究了这些问题,并从1999年开始发表研究成果,展示了SEG用于源/漏工程如何将国家技术路线图半导体(NTRS)路线图扩展到亚30纳米节点。

他们的第一篇论文由Ban和Ozturk在1999年5月ECS研讨会上关于快速热处理进展的报告,题为"使用选择性生长的原位硼掺杂硅薄膜的50-70nm CMOS超浅P+-N结",实现了SEG源/漏B水平高达3E21/cm3,比硼在硅中的固体溶解度极限高一个数量级。

一年后的2000年,NCSU研究小组将报告通过添加Ge形成SiGe合金然后添加硅凹槽刻蚀的改进效果。

2000年代

NCSU在2000年的第一篇论文发表于ECS 2000年5月快速热处理和其他短时间工艺技术研讨会上,由Gannavaram和Ozturk撰写,题为"用于35-70 nm CMOS的选择性沉积高浓度硼掺杂硅锗薄膜制备的超浅P+-N结"。他们报告了S/D区域30 nm的凹槽刻蚀,随后进行原位硼掺杂SiGe(45-75%)。他们报告S/D区域的高SiGe压缩应变被1-5E21/cm3浓度的小型硼掺杂原子所补偿;20% SiGe需要2.5% B,而80% SiGe需要10% B来实现应变补偿。

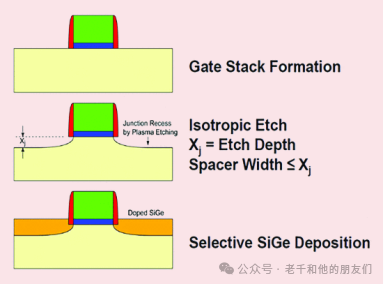

七个月后,在IEDM-2000,Gannavaram等人的论文18.3介绍了一种新的CMOS S/D工艺技术,这一技术最终将摩尔定律延伸了另外二到三十年,直至2025年及以后。他们的论文标题是"用于亚70纳米CMOS的低温(<800°C)凹槽结选择性硅锗源/漏技术"。

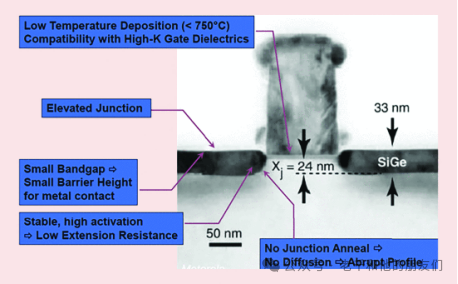

作者认为这是他们关于S/D选择性外延生长的第一篇开创性论文,因为该论文指出这项新技术满足NTRS路线图的要求:1)30纳米结的Rs/Xj <100 Ω/sq,2)超低电阻率接触(1.5×10-8 Ω-cm2),3)优异的反向漏电特性,4)完美的盒形横向陡峭度,以及5)使用传统栅极后CMOS工艺流程与HK栅介质的热集成兼容性。

谁能预见到七年后的2007年,英特尔将推出其45纳米节点混合HK先/MG后技术,随后在32纳米节点采用HK/MG后工艺。NCSU提倡单一S/D CMOS晶体管设计,而不是传统的浅源漏延伸区(SDE)或轻掺杂漏极(LDD)与深S/D结构。凹槽硅刻蚀(等离子体刻蚀)深度将决定浅结深度,达到<30 nm。

为了将原位硼掺杂浓度从硅中2E20/cm3的固溶限提高到7E20/cm3,他们使用了选择性SiGe合金沉积(45-66%),并提到SiGe引起的压缩应变被替位硼原子所补偿/缓解,导致更高的掺杂剂掺入,正如他们在2000年5月ECS论文中早先报告的那样。图16说明了通过等离子体刻蚀的凹槽刻蚀步骤,然后进行选择性掺杂SiGe S/D。图17所示的X-TEM分析显示了用于USJ的24纳米凹槽刻蚀。

图16.源/漏凹槽刻蚀,随后进行选择性硅锗源/漏

图17凹槽结选择性硅锗源/漏的横截面透射电子显微镜图

两年后,在2002年10月ECS半导体硅研讨会上,Ozturk等人的受邀论文"基于选择性CVD SiGe合金的30纳米以下CMOS技术节点新结技术",我认为这是他们的第二篇开创性论文,因为它描述了在2003年英特尔90纳米节点中可以找到的关键SiGe SEG工艺步骤。

S/D形成涉及将S/D区域凹槽刻蚀到所需的结深度,随后进行选择性SiGe沉积,同时形成抬高的S/D结构以改善接触形成。他们使用镍(Ni)形成锗硅化物以获得低接触电阻。该论文还提到,在高温结形成后需要HK/MG后工艺,这与英特尔在2007年推出的45纳米节点混合HK先/MG后工艺非常相似。

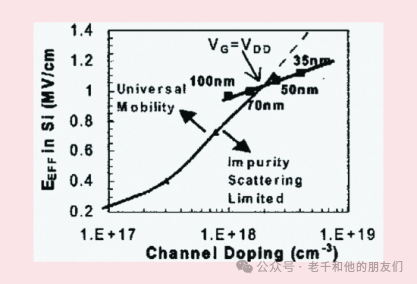

英特尔90纳米节点引入了pMOS的eSiGe S/D应力器和nMOS的CVD应力衬垫。正如英特尔的Ghani等人在2000年VLSI技术研讨会上报告的,随着沟道掺杂浓度增加到>2E18/cm3,杂质散射占主导地位,需要沟道迁移率增强,如图18所示。

图18.沟道掺杂浓度对杂质散射的影响

因此,图19显示了从90纳米节点的平面结构到22纳米节点的3D FinFET的五代pMOS选择性SiGe S/D应力器,锗含量从17%增加到55%,以及最佳栅极重叠/非重叠距离(+35 nm至-3 nm),这需要对英特尔Kuhn等人在IEDM-2012上报告的硅横向凹槽刻蚀进行关键控制。

图19.SiGe浓度与栅极重叠的关系

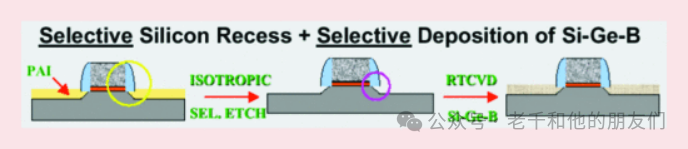

垂直和横向硅凹槽刻蚀步骤对于优化栅极到S/D在沟道应变上的重叠至关重要。德州仪器的研究人员报告了他们用于SDE应变硅的SEG eSiGe活动。为了控制凹槽刻蚀工艺,Mansoori在2002年Varian年度vTech技术研讨会上报告了使用预非晶化注入(PAI)进行各向同性选择性刻蚀控制,随后进行选择性Si-Ge-B沉积,如图20所示。

图20.使用PAI注入实现各向同性选择性刻蚀控制

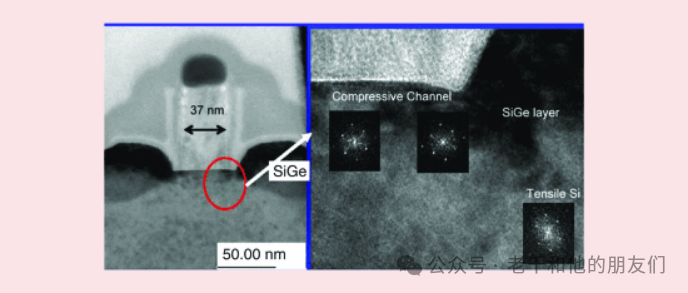

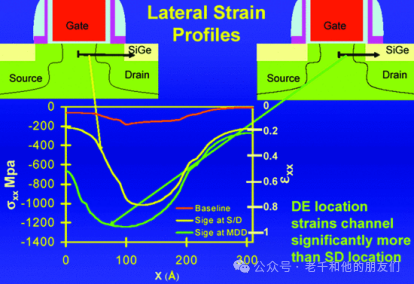

Chidambaran在vTech 2004上展示了高分辨率(晶格成像)X-TEM应变硅分析结果,图21显示压缩沟道区域和拉伸S/D区域。图22显示了德州仪器独特的漏极延伸(DE) eSiGe工艺的横向应变模拟结果,该工艺比记录中的S/D eSiGe工艺提供更高的沟道应变。

图21漏极延伸区SiGe应力层的X-TEM分析

图22.SiGe DE的横向应变模拟剖面图

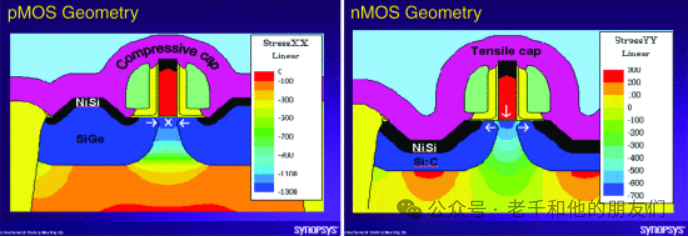

在2005年5月ECS会议上,Synopsys的Moroz报告了用于凹槽刻蚀选择性外延的应变硅器件模拟,pMOS使用SiGe,nMOS使用SiC,结合CVD应力帽,如图23所示:pMOS沟道横向应变高达-1,300 MPa,nMOS沟道横向应变为+400 MPa。

图23.应变硅的SiGe源/漏区P型MOS和SiC源/漏区N型MOS的模拟结果

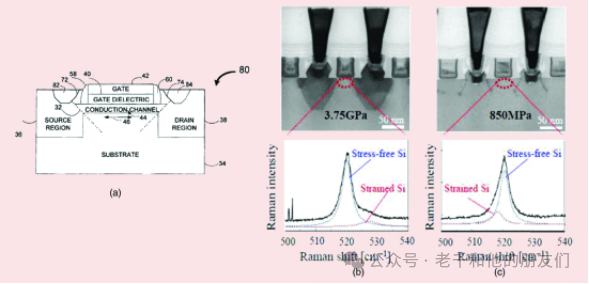

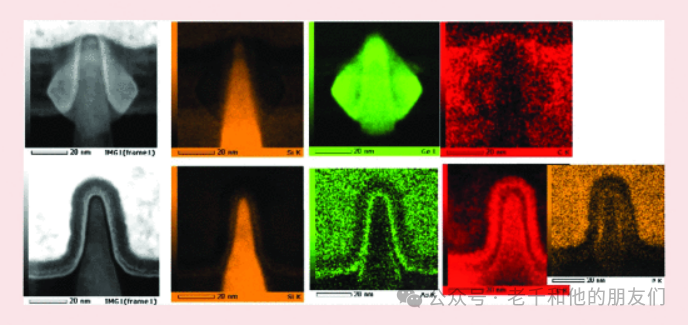

英特尔在32纳米节点继续避免使用选择性SiC S/D应力器,而是使用作者称之为堆垛层错应力器的技术,如图24(a)所示,由Weber等人在其美国专利申请"增强错位应力晶体管"中报告。明治大学的Ogura小组告诉我,他们如何从东京秋叶原地区的电子商店购买英特尔32纳米芯片,并进行了详细的X-TEM分析、拉曼应变分析和能量色散X射线(EDAX)化学分析,如图24(b)、(c)和25所示,分别针对pMOS和nMOS。

图24.(a)–(c)明治大学对英特尔32纳米节点eSiGe型pMOS和堆垛层错应力源nMOS的应变分析

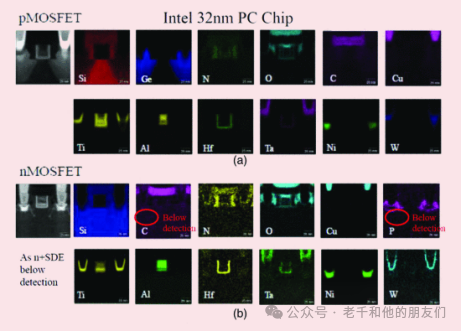

拉曼分析显示,具有40% eSiGe S/D和0 nm栅极重叠的pMOS沟道应变为3.75 GPa,而他们测量到具有堆垛层错应力器的nMOS沟道应变为850 MPa,尽管英特尔专利提到了碳化硅材料。EDAX技术要求化学水平>2%至3%才能检测到,Ge为蓝色,Si为红色,C为紫色,Ti为黄色(图25)。32纳米节点清晰显示了HK/MG后多化学层组成。直到IBM在IEDM-2012上报告的22纳米节点PD-SOI,选择性SiC-S/D才用于平面CMOS,如图26所示,它们采用了HK/MG先工艺。

图25.(a)和(b)英特尔32纳米节点的详细X-TEM和EDAX化学分析

图26IBM采用双重硅锗和碳化硅源/漏应力技术的22纳米节点PD-SOI

2010年代

英特尔在2011年以22纳米节点引入了3D FinFET器件架构,采用类似STI的鳍先方法,使用刻蚀的硅台结构和SEG eSiGe S/D应力器,如图2所示。如前面图25所示,EDAX用于晶体管的化学分析是一种强大的工具。

2013年,明治大学的Ogura小组检查了英特尔22纳米FinFET,如图27所示。nMOS鳍区域显示有As(图27中的绿色)、P(图27中的橙色)和C(图27中的红色)注入的证据,而pMOS鳍区域显示绿色的Ge-S/D(图27)。S/D区域没有选择性SiC外延的证据。

图27. Intel 22纳米鳍式场效应晶体管(FinFET)的EDAX化学分析,显示了用于nMOS的P、As和C元素注入的证据

在FinFET 14纳米节点,凹槽刻蚀选择性外延SiCP S/D用于nMOS终于成为块状CMOS技术的主流。图28中的X-TEM分析显示了双SEG S/D应力器,这是由Chipworks的James在2015年Semicon/West AVS-西海岸结技术用户组会议上报告的。这显示了三星Galaxy S6中使用的三星Exynos 7420应用处理器;注意选择性S/D结构是合并的,限制了用于金属接触形成的顶部表面。

2020年代

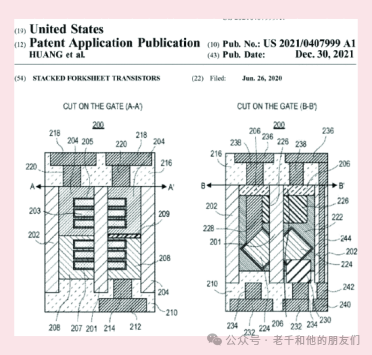

行业计划在亚3纳米节点迁移到3D GAA纳米片器件,三星在3纳米节点率先采用。对于环绕接触(WAC),使用SEG eSiGe-B用于pMOS和eSiC-P用于nMOS S/D变得至关重要,如图3所示。这将持续到下一个十年,正如英特尔的Huang等人在他们的堆叠CMOS叉形片美国专利中报告的那样,如图29所示,该专利使用SEG实现了环绕n+和p+接触。

图29.英特尔CMOS堆叠叉形片专利,展示SEG-S/D环绕接触点

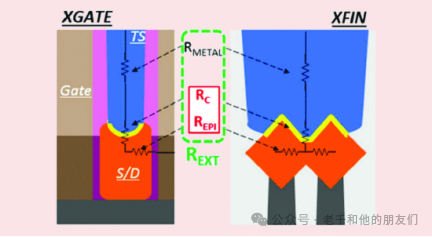

图29中的"栅极上切割"图像清晰地显示了堆叠CMOS纳米片器件的菱形SEG-WAC结构。如Gluschenkov等人在2023年国际结技术研讨会上报告并在图30中说明的那样,接触电阻变得至关重要,因为在环绕接触中金属只接触SEG-WAC结构的顶部表面。

图30.改善SEG-S/D的接触电阻

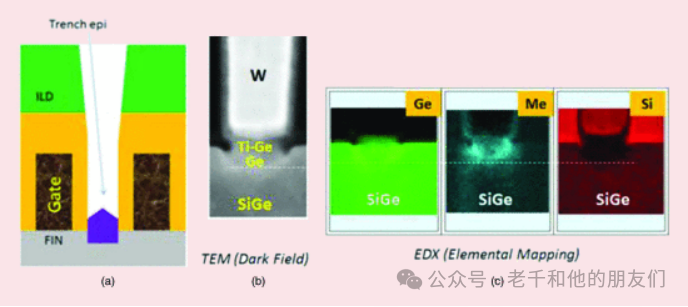

他们报告,金属到S/D界面的低接触电阻在堆叠CMOS中将变得更加关键和具有挑战性,需要新的先进退火和表面材料修饰/工程技术。一个例子是他们的选择性"沟槽"外延工艺,如图31所示,旨在改善接触电阻,由Xie等人和Gluschenkov等人在IEDM-2016上报告。

图31.IBM选择性沟槽外延优化接触电阻:(a)锗选择性外延生长(Ge-SEG),(b)横截面透射电子显微镜(X-TEM),(c)能量色散X射线光谱(EDX)

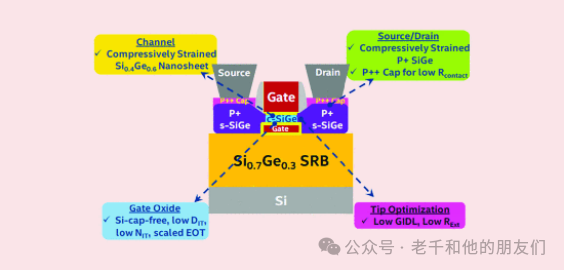

图31(a)说明了在接触开口底部的选择性Ge"沟槽"外延;图31(b)显示了X-TEM暗场图像,图31(c)显示了EDX元素映射,展示了Ge:III族金属合金。英特尔的Agrawal等人在他们2020年IEDM论文中为纳米片pMOS显示的图32中,在选择性SiGe S/D WAC顶部有一个p++帽层,用于低接触电阻。注意他们展示了尖端(SDE)优化以获得低延伸电阻。

图32.英特尔使用p++帽层以获得低接触电阻

结论

自1962年在《自然》杂志上首次发表以来,硅SEG技术现已有61年历史。用于CMOS S/D应力器的应用已有20年,于2003年随英特尔90纳米节点技术引入。随着向3D堆叠CMOS器件的迁移,SEG技术用于环绕接触的预期寿命应该会延长到2030年代的另一个十年。

-

半导体

+关注

关注

339文章

31238浏览量

266577 -

工艺

+关注

关注

4文章

720浏览量

30393 -

晶体管

+关注

关注

78文章

10439浏览量

148610

原文标题:半导体专题| 选择性外延生长的历史回顾:从1962年至今

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

半导体发展的四个时代

PCB选择性焊接技术介绍

PCB选择性焊接技术详细

PCB选择性焊接技术详细

嵌入式源漏选择性外延(Embedded Source and Drain Selective Epitaxy)

6.1.1 选择性掺杂技术∈《碳化硅技术基本原理——生长、表征、器件和应用》

应力消除外延生长装置及外延生长方法

半导体选择性外延生长技术的发展历史

半导体选择性外延生长技术的发展历史

评论