概述

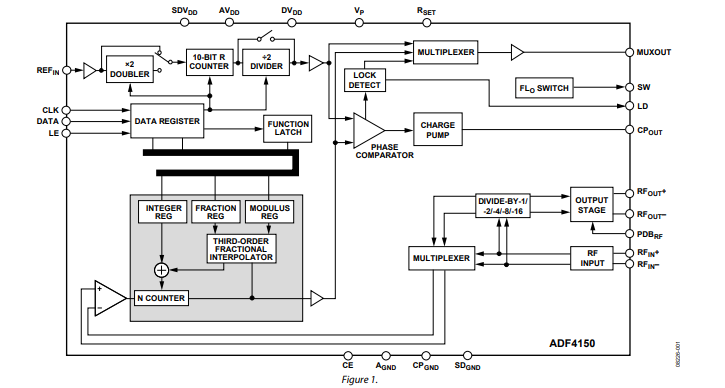

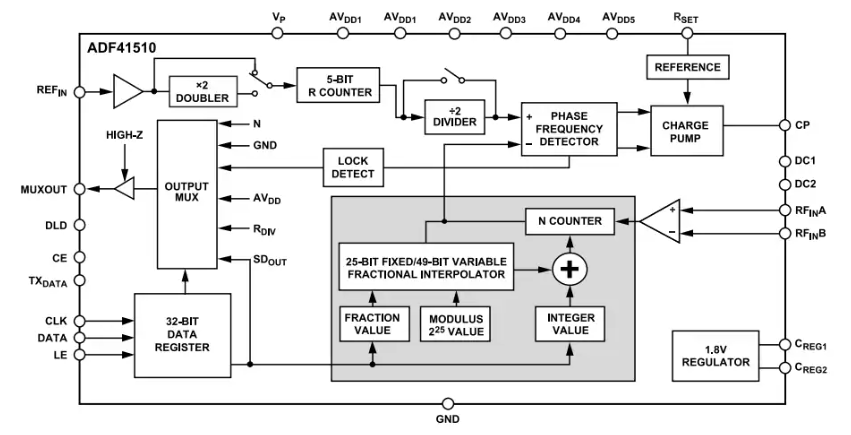

ADF41513 是一款超低噪声频率合成器,可用于在无线接收器和变送器的升频转换和降频转换部分实施高达 26.5 GHz 的本地振荡器 (LO)。

ADF41513 的设计基于高性能硅锗 (SiGe) 双极互补金属氧化物半导体 (BiCMOS) 工艺,可实现 −234 dBc/Hz 的归一化相位本底噪声。相位频率检波器 (PFD) 的工作频率高达 250 MHz(整数 N 模式)/125 MHz(小数 N 模式),可实现更高的相位噪声和杂散性能。使用 49 位分值时,可变模数 Δ-Σ 调制器可以实现极精细的分辨率。ADF41513 可用作整数 N 锁相环 (PLL) 或小数 N PLL,可使用固定模数以实现亚赫兹频率分辨率或使用可变模数以实现亚赫兹精确频率分辨率。

频率合成器与外部环路滤波器和压控振荡器 (VCO) 配合使用可实现完整的 PLL。26.5 GHz 带宽意味着不再需要倍频器或分频器级,从而简化了系统架构并降低了成本。ADF41513 采用紧凑式 24 引脚 4 mm × 4 mm LFCSP 封装。

数据表:*附件:ADF41513 26.5GHz整数N 小数N PLL频率合成器技术手册.pdf

应用

特性

- 1 GHz 至 26.5 GHz 带宽

- 超低噪声 PLL

- 整数 N:−234 dBc/Hz,小数N:−231 dBc/Hz

- 最大高 PFD 频率

- 整数 N:250 MHz,小数N:125 MHz

- 25 位固定/49 位可变小数模数

- 单端参考输入

- 3.3 V 电源,3.3 V 电荷泵

- 集成 1.8 V 逻辑能力

- 相位再同步

- 可编程电荷泵电流:16× 范围

- 数字锁定检测

- 3 线串行接口,具有寄存器回读选项

- 硬件和软件关断模式

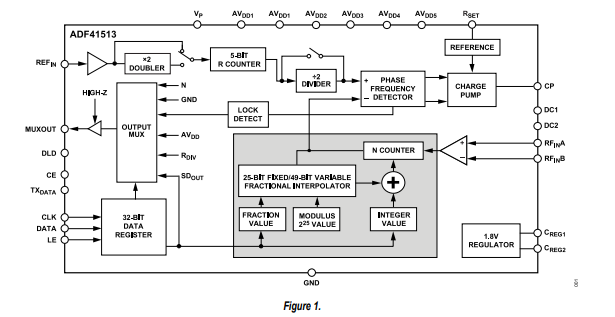

框图

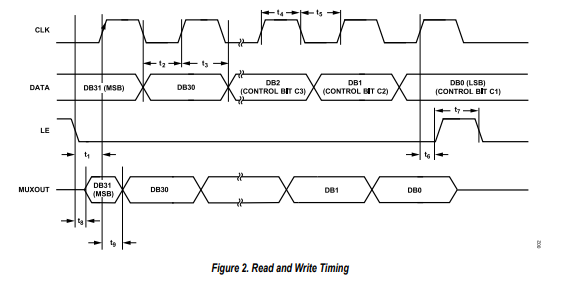

时序图

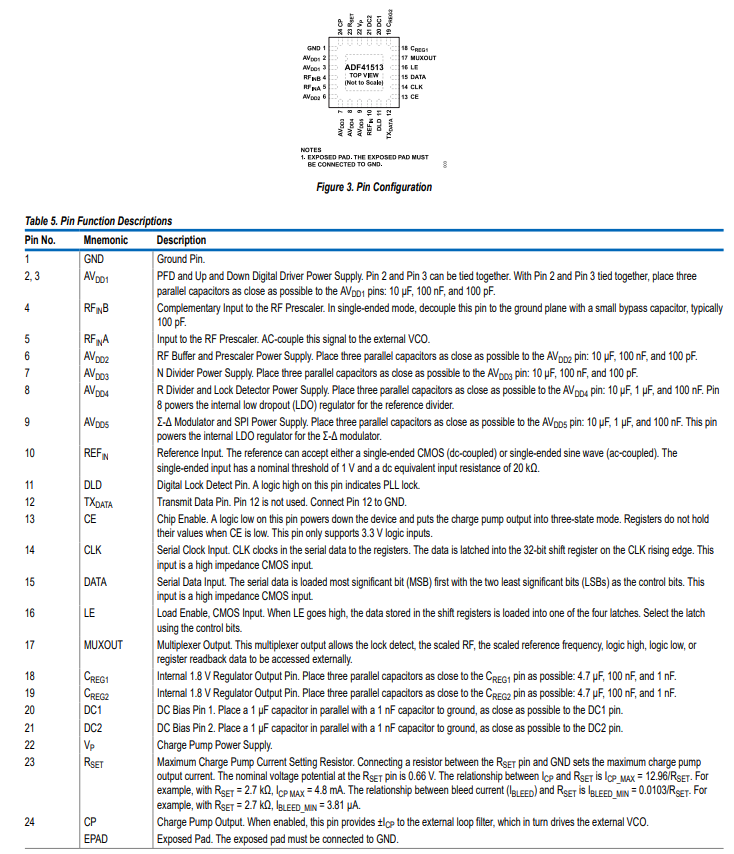

引脚配置描述

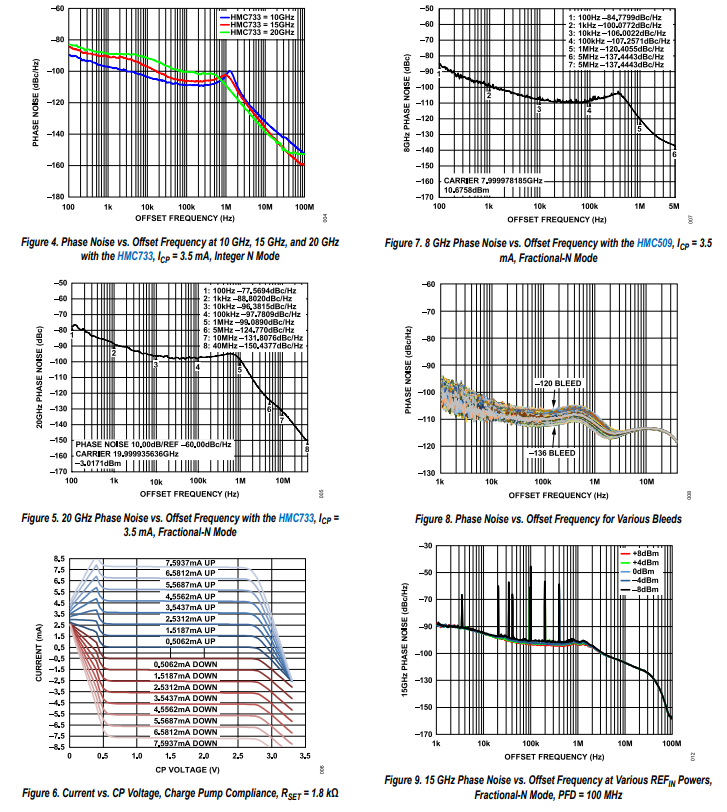

典型性能特征

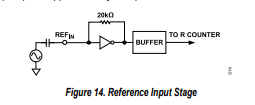

参考输入

参考输入级如图14所示。该参考输入接受交流耦合的单端信号。在掉电期间,此电路保持工作状态,并从**AV_{DD}**汲取相同电流;在无参考连接时,**AV_{DD}**下降约600 μA。

图14. 参考输入级

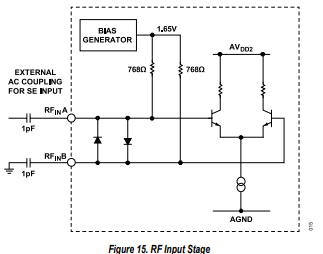

射频输入级

射频输入级如图15所示。两级限幅放大器(CML)为预分频器提供所需的时钟电平。射频**V_{IN+}和射频V_{IN-}**输入包含隔直电容,以隔离来自输入信号的1.65V偏置电平。

图15. 射频输入级

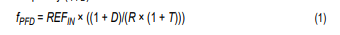

N分频器和R计数器

N分频器用于将射频输入信号分频至鉴频鉴相器(PFD)频率(f_{PFD})。

其中:

- **REF_{IN}**是参考输入频率。

- D是**REF_{IN}**倍频位(0或1)。

- R是5位二进制可编程参考计数器的预设分频比(1至32)。

- T是**REF_{IN}**二分频位(0或1)。

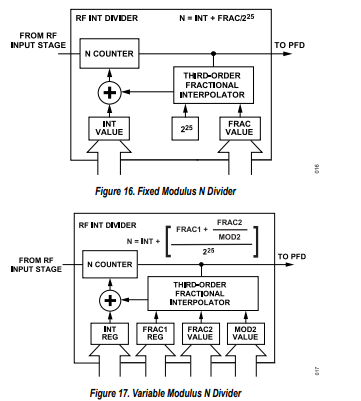

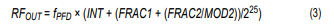

N分频器值由Σ-Δ调制器生成。N分频器包含两个可选调制器。一个调制器的模数固定为$2^{25}$(见图16),另一个的模数可变,最高可达49位(见图17)。寄存器0的第28位用于选择调制器。

图16. 固定模数N分频器

图17. 可变模数N分频器

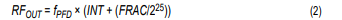

25位固定模数(寄存器0,位28 = 0)

对于25位固定模数,射频压控振荡器(VCO)频率(RF_{OUT})公式为:

其中:

- **RF_{OUT}**是射频VCO频率。

- INT是寄存器0中16位整数值(在整数N模式下,对于4/5预分频器,INT为20至511;对于8/9预分频器,INT为64至1023;在分数N模式下,对于4/5预分频器,INT为23至511;对于8/9预分频器,INT为75至1023)。

- FRAC是25位小数位(由寄存器1中的FRAC1设置)。

最小射频输出分辨率为$2^{25}×f_{PFD}。例如,若f_{PFD}$ = 100 MHz,最小分辨率为2.98 Hz。

默认情况下,由于架构Σ-Δ调制器的存在,会有一个固定的(f_{PFD}/$2^{25}$)偏移量从编程输出频率中减去(有关此偏移量的更多信息,请参见辅助SPI寄存器,寄存器1,位24)。

可变模数(R0,DB28 = 1)

对于可变模数,射频VCO频率(RF_{OUT})公式为:

-

振荡器

+关注

关注

28文章

4191浏览量

143163 -

频率合成器

+关注

关注

5文章

368浏览量

33878 -

SiGe

+关注

关注

0文章

99浏览量

24662 -

pll

+关注

关注

6文章

989浏览量

138360

发布评论请先 登录

ADF41513BCPZ频率合成器产品介绍

ADF41513:26.5 GHz,整体而言N/facional-N,PLL合成器数据Sheet

ADF41513 26.5GHz整数N/小数N PLL频率合成器技术手册

ADF41513 26.5GHz整数N/小数N PLL频率合成器技术手册

评论