在PCB(印制电路板)设计中,整板铺铜是一个需要仔细考虑的问题。铺铜,即在PCB的空白区域覆盖铜膜,这一做法既有其显著的优势,也可能带来一些潜在的问题。是否整板铺铜,需根据具体的设计需求和电路特性来决定。

1、铺铜的优点

降低地线阻抗:大面积的铜膜可以作为地线,显著降低地线阻抗,这对于提高电路的稳定性和抗干扰能力非常重要。

减少电磁干扰(EMI):铺铜可以形成一个连续的屏蔽层,有效减少电磁干扰,保护敏感电路免受外部电磁场的影响。

增强散热性能:铜具有良好的导热性能,大面积的铜膜可以帮助散发元器件工作时产生的热量,提高设备的稳定性和寿命。

减少形变:铺铜可以增加PCB的刚度,减少因温度变化或机械应力导致的形变,提高PCB的可靠性。

2、铺铜的缺点

焊接和返修困难:大面积的铜膜可能增加焊接和返修的难度,特别是在需要局部修改或维修时。

高频信号干扰:在高频电路中,铺铜可能作为天线引入额外的干扰信号,影响电路的性能。

增加成本:铺铜需要消耗更多的铜材料,可能增加PCB的制造成本。

3、不同层数PCB的设计建议

两层板:

对于两层板,通常建议底层铺地平面,作为主要的地线层。

顶层则用于放置主要器件,走电源线和信号线。这样的设计可以充分利用铺铜的优势,同时避免对顶层器件和走线造成干扰。

多层板:

在有完整电源、地平面的多层板高速数字电路中,外层铺铜并不会带来很大的益处。

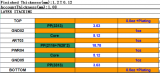

反而可能因铜膜与信号线之间的耦合而改变微带传输线的阻抗,影响信号完整性。因此,在多层板设计中,需要谨慎考虑外层铺铜的必要性。

4、特殊电路和区域的处理方式

高阻抗回路和模拟电路:

对于高阻抗回路和模拟电路,铺铜可以有效降低地线阻抗,提高电路的抗干扰能力和稳定性。

因此,在这些区域铺铜通常是有益的。

天线部分周围区域:

在天线部分周围区域,一般不建议铺铜。因为铜膜可能作为天线引入额外的干扰信号,或者改变天线的辐射特性,从而影响无线通信的性能。

通过以上内容可知,在PCB设计中,是否整板铺铜需要综合考虑多个因素。包括电路的类型、信号完整性要求、散热需求以及制造成本等。对于两层板,通常建议底层铺地平面;对于多层板高速数字电路,外层铺铜需要谨慎考虑;对于高阻抗回路和模拟电路,铺铜通常是有益的;而在天线部分周围区域,则不建议铺铜。通过合理的设计和优化,可以充分发挥铺铜的优势,同时避免其潜在的问题。

审核编辑 黄宇

-

PCB设计

+关注

关注

396文章

4939浏览量

95780

发布评论请先 登录

射频前端设计的阻抗匹配和铺铜距离参数解析

07. 如何在Allegro中设置可以走线但不能铺的铜区域?| 芯巧Allegro PCB 设计小诀窍

射频PCB的“隐形杀手”:90%的工程师都忽视的铺铜细节!

高速PCB工程师必看:用仿真三步法,让铺铜从“隐患”变“保障”

从设计阶段排查预防PCB短路

高速PCB设计EMI避坑指南:5个实战技巧

深度解读PCB设计布局准则

上海图元软件国产高端PCB设计解决方案

Allegro Skill布线功能之切线、切铜、连接布线介绍

PCB设计整板铺铜说明

PCB设计整板铺铜说明

评论