本文由半导体产业纵横(ID:ICVIEWS)综合

易于扩展、更快创新和成本效益都是芯片组的优势,同时还增强了功能和性能效率。

根据 IDTechEx 最近发布的一份报告,利用小芯片技术可以实现更小、更紧凑且结构简化的设计,该报告与竞争性半导体设计及其最适合的应用相比,阐述了开发小芯片技术的优势和挑战。

芯片组使 GPU、CPU 和 IO 组件小型化,以适应越来越小巧紧凑的设备和硬件,并可以将各种功能集成到更简化、统一的设计中。易于扩展、更快创新和成本效益都是芯片组的优势,同时还增强了功能和性能效率。

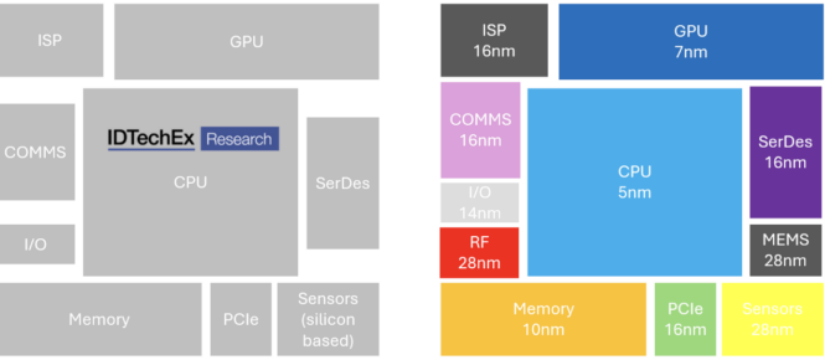

来源:IDTechEx

与单片 SoC 和多芯片 SiP 相比,小芯片的开发速度更快,而且可以大量重复使用。它们还有望实现单片设计无法实现的新功能,尤其是在人工智能、物联网和先进计算系统等领域。

然而,尽管小芯片可广泛应用于智能手机、汽车系统、高性能计算 (HPC)、数据中心和云计算,但它们并非旨在取代性能效率更高的单片 SoC。

半导体制造工艺

未来半导体节点将逐渐变小,通过增加组件密度和功能密度,可能有助于改善芯片和单片设计。单片集成目前因其性能质量和能效而广泛应用于 HPC,而芯片可以使用不太先进的节点来制造专用组件,从而降低成本并缩短上市时间。

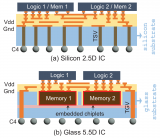

IDTechEx 预测的另一个未来趋势是先进的 3D 堆叠,通过这种技术可以改善芯片和单片设计的互连性和热管理,从 2D 结构转向 3D 结构,从而实现更紧凑、更高性能的系统。

Chiplet技术解决的问题

Chiplet技术通过将一个大的芯片分解成多个小的模块(即Chiplet),然后通过高速互连技术将它们组合起来,以实现整个芯片的功能。

与传统单片系统相比,具有以下优点:

可重新使用的知识产权:同一个chiplet可以在许多不同的设备中使用。

更快的上市时间:由于小芯片可以独立设计和制造,因此可以采用更加模块化的 IC 设计方法。这可以加速开发过程,从而加快新产品的上市时间。

设计灵活性和可扩展性:Chiplet设计允许通过组合不同的模块来快速实现不同的功能,极大地提高了设计的灵活性和产品的可扩展性。

提高制造良率:与单片芯片相比,小芯片尺寸更小,可以带来更高的制造良率。如果小芯片在制造过程中出现故障,可以在不丢弃整个芯片的情况下进行更换,从而减少浪费和成本。

多芯片(chiplet)设计导致额外面积增加主要是因为需要额外的互连区域、每个芯片的封装边界、可能的冗余设计元素以及布局和功率分配的考虑。尽管这会带来一定的面积和成本增加,但通过显著提高良率、降低单芯片复杂性和增加设计灵活性,多芯片设计在总体上能有效降低生产成本并提升生产效率,为满足快速变化的市场需求提供了一种有效的策略。

Chiplet技术趋势

实现通用互连标准可实现不同制造商的芯片之间的互操作性,并提高其使用灵活性。随着美国、中国、德国和日本等国家对芯片的兴趣日益浓厚,这一点将尤为有用。芯片设计交易所 (CDX) 正在努力实现芯片设计的开放格式,以克服标准化方面的挑战,这对于促进芯片在各个领域的更广泛采用是必不可少的。

芯片之间的通信对于实现互连和可靠性也至关重要。IDTechEx 报告称,目前正在开发多种技术来实现这些目标,包括通用芯片互连快递 (UCIe) 和线束 (BoW)。

新的测试方法正在涌现,以应对与芯片技术相关的挑战。IDTechEx 强调使用可测试设计 (DFT) 和内置自测试 (BIST) 策略作为测试芯片的经济可行解决方案。这些方法有助于克服测试互连芯片的复杂性,通过直接在芯片设计中实现故障检测、诊断和优化,减少对外部测试设备的依赖。此外,正在开发分层测试和芯片间通信测试等先进技术,以确保跨芯片接口的全面测试覆盖。

虽然测试策略侧重于确保功能性和可靠性,但铜混合键合等键合方法的进步正在彻底改变芯片集成。铜混合键合消除了传统的焊料凸块,实现了超细间距连接,并提高了电气和热性能。这种键合技术支持更高的互连密度并降低寄生电阻,使其成为紧凑型高性能芯片系统的关键推动因素。

-

芯片

+关注

关注

463文章

54463浏览量

469720 -

SiP

+关注

关注

6文章

543浏览量

108032 -

chiplet

+关注

关注

6文章

499浏览量

13659

发布评论请先 登录

算力爆发时代IP设计面临哪些新挑战

深入解析48V供电网络设计的技术挑战

拥抱Chiplet,大芯片的必经之路

多Chiplet异构集成的先进互连技术

如何突破AI存储墙?深度解析ONFI 6.0高速接口与Chiplet解耦架构

西门子EDA如何推动Chiplet技术商业化落地

跃昉科技受邀出席第四届HiPi Chiplet论坛

得一微电子受邀出席第四届HiPi Chiplet论坛

Chiplet核心挑战破解之道:瑞沃微先进封装技术新思路

Chiplet封装设计中的信号与电源完整性挑战

解构Chiplet,区分炒作与现实

玻璃中介板技术的结构和性能优势

CMOS 2.0与Chiplet两种创新技术的区别

Chiplet与3D封装技术:后摩尔时代的芯片革命与屹立芯创的良率保障

Chiplet技术的优势和挑战

Chiplet技术的优势和挑战

评论