文章来源:老虎说芯

原文作者:老虎说芯

本文介绍了在集成电路制造工艺中的High-K材料的特点、重要性、优势,以及工艺流程和面临的挑战。

DRAM(动态随机存取存储器)是一种常见的内存芯片,就像我们家里的储藏室,用来短暂存放数据(“0”或“1”)。DRAM最基本的结构就是由一个晶体管(相当于开关)和一个电容(相当于储藏室)组成的“1T1C”单元。

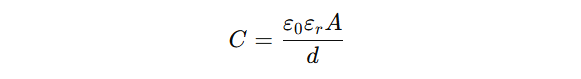

随着芯片尺寸不断缩小(从28纳米缩小到10纳米以下),电容这个“小储藏室”的面积(A)急剧减小,但存储能力(电容值C)却不能降低。按照公式:

面积变小了,要维持容量,就只能减薄介质层厚度(d)。但传统硅氧化物(SiO₂,介电常数ε_r≈3.9)一旦变得极薄(例如1纳米左右),漏电流就会指数级增加,导致电荷快速流失,数据无法稳定保存。

核心原理篇:High-K材料如何破解难题?

High-K(高介电常数)材料,就是指介电常数(ε_r)比传统SiO₂高数倍甚至十几倍的新材料,如氧化铪(HfO₂,ε_r≈25)、氧化锆(ZrO₂,ε_r≈30)等。

通俗地讲,如果将电容比作“蓄水池”,则介电常数越高,就好比蓄水池内壁更加厚实,不容易“渗漏”,即便把“蓄水池”面积造得更小,也仍能保持足够水量,不必牺牲内壁厚度。

工艺流程篇:如何将High-K材料引入芯片制造?

引入High-K材料主要有以下关键工艺:

1.选材与沉积工艺(ALD)

通过原子层沉积技术(Atomic Layer Deposition, ALD)精确沉积极薄均匀的高K薄膜。这就像用3D打印机逐层铺设墙砖,每一层都精准一致,从而确保膜厚度均匀可靠。

2.界面优化工程

High-K材料与硅晶圆表面直接接触会产生缺陷(就像新粉刷的墙面不光滑),需用特殊处理工艺(例如氮化处理或加入极薄SiO₂过渡层)修复这些缺陷,确保“墙面”光滑、平整,提高芯片性能与可靠性。

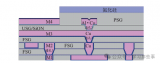

3.结合3D电容结构

此外,芯片设计师还将High-K材料与立体的圆柱或沟槽结构电容结合。类比为在原本平面的停车场上搭建多层停车库,大幅提升有效面积,使电容值进一步增强。

优势篇:High-K材料的三大技术红利

1.性能提升

因为High-K材料厚度更厚,电子“漏出”概率大幅降低,这有效延长了数据保存时间。同时,由于电容充放电效率更高,芯片数据读写速度也提升显著,可适用于更高频的DDR5、LPDDR5甚至未来的DDR6标准。

2.功耗降低

漏电减少,意味着不需要频繁刷新数据,直接降低芯片的动态功耗。同时,厚度增加意味着电场强度减小,也能有效降低静态功耗。

3.工艺兼容性强

现有芯片产线可较平稳地导入ALD沉积High-K材料的步骤,这对于先进制程(如10纳米以下)至关重要。

技术难点篇:实现High-K材料的挑战有哪些?

尽管优势突出,但High-K技术面临三大关键挑战:

1.工艺复杂、成本高昂

ALD设备价格高昂、沉积工艺精细化,直接导致芯片生产成本上升;同时,铪(Hf)、锆(Zr)等稀有元素本身成本也较高。

2.界面缺陷控制难度大

High-K材料与硅表面接触容易形成界面缺陷,严重时将影响芯片稳定性。这对晶圆制造厂商的技术积累和品控能力提出极高要求。

3.长期可靠性与寿命问题

长期工作下High-K材料可能发生“氧空位迁移”,导致芯片性能(如阈值电压)漂移,可靠性降低。针对该问题,需要引入特殊掺杂工艺,如掺入镧(La)或硅(Si),或构建多层复合结构以抑制氧空位迁移。

未来展望篇:下一个十年High-K技术往哪里去?

技术进步永不止步,未来High-K材料仍有巨大创新空间:

1.新材料探索

铁电氧化铪(Fe-HfO₂)材料兼具铁电性和高介电常数,有望进一步增强电容特性,适合更高速、更高容量的下一代内存技术。

2.二维材料异质集成

与二维半导体材料(如二硫化钼MoS₂)结合,有望打破传统硅材料和3D结构的物理极限,创造性能更佳的内存芯片。

3.人工智能辅助新材料开发

通过AI和机器学习快速筛选和优化High-K材料及配方,加速工艺创新进程,显著降低研发周期和成本。

总结篇:芯片制造离不开的关键技术

High-K介质就如同芯片产业的“隐形英雄”,它巧妙地平衡了芯片尺寸缩小和性能保持之间的根本矛盾。

-

芯片

+关注

关注

463文章

54437浏览量

469399 -

集成电路

+关注

关注

5464文章

12686浏览量

375742 -

制造工艺

+关注

关注

2文章

216浏览量

21315 -

芯片制造

+关注

关注

11文章

735浏览量

30532

原文标题:芯片制造为什么需要High-K材料

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

集成电路制造工艺中的High-K材料介绍

集成电路制造工艺中的High-K材料介绍

评论