这是NVMe控制器IP设计系列博客之一,其他的见本博客或csdn搜用户名:tiantianuser。相关视频见B站用户名:专注与守望。

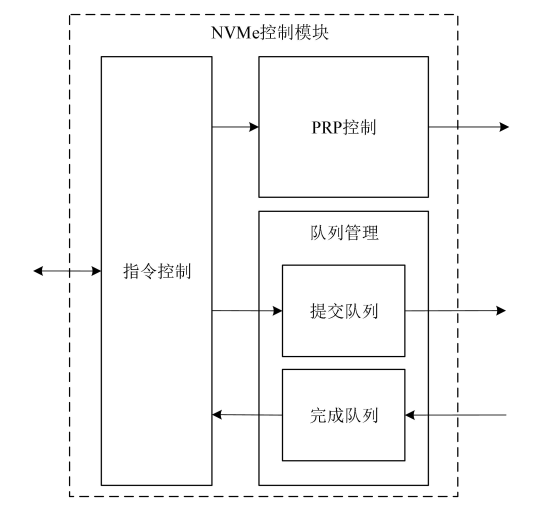

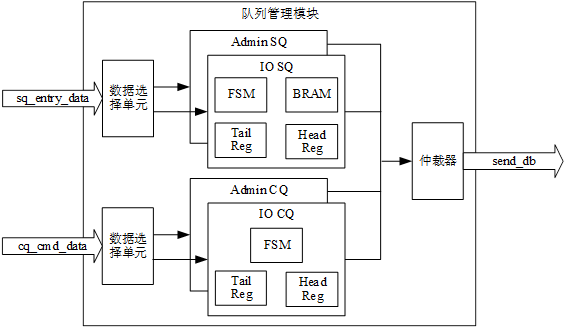

接口转换模块负责完成AXI4接口与控制器内部的自定义接口之间的转换工作。接口转换模块的框图如图1所示。

图1 接口转换示意图

由于AXI4接口协议的实现会占用大量的逻辑资源,为了节约资源,控制器内部的接口信号均采用逻辑简单的自定义接口,对外通过此模块转换为通用的AXI4接口,从而实现与其他模块之间的高效互联。

接口转换模块内部包含AXI4-Lite写转换模块、AXI4读转换模块、AXI4写转换模块。AXI4-Lite写转换模块是用于将内部信号(addr、en、data_db)转换为与AXI PCIe IP模块相连接的AXI4-Lite接口。

该模块的主要功能是在队列管理模块需要更新SSD内部门铃寄存器时,通过访问BAR空间实现更新NVMe SSD内部门铃寄存器。

门铃寄存器更新后,NVMe SSD会通过AXI PCIe IP模块的AXI4接口访问提交队列内存空间,读取NVMe命令。在这个过程中,需要通过读转换模块将读地址通道和读数据通道的信号转换为控制器内部信号(addr、en、data_out)。

命令执行结束后,完成信息通过AXI PCIe IP模块的AXI4接口传输至完成信息解析模块。这个过程需要通过AXI4写转换模块将读地址通道和读数据通道的信号转换为控制器内部信号(addr、en、data_in)。

-

控制器

+关注

关注

114文章

17863浏览量

195034 -

接口

+关注

关注

33文章

9591浏览量

157598 -

nvme

+关注

关注

0文章

300浏览量

23909

发布评论请先 登录

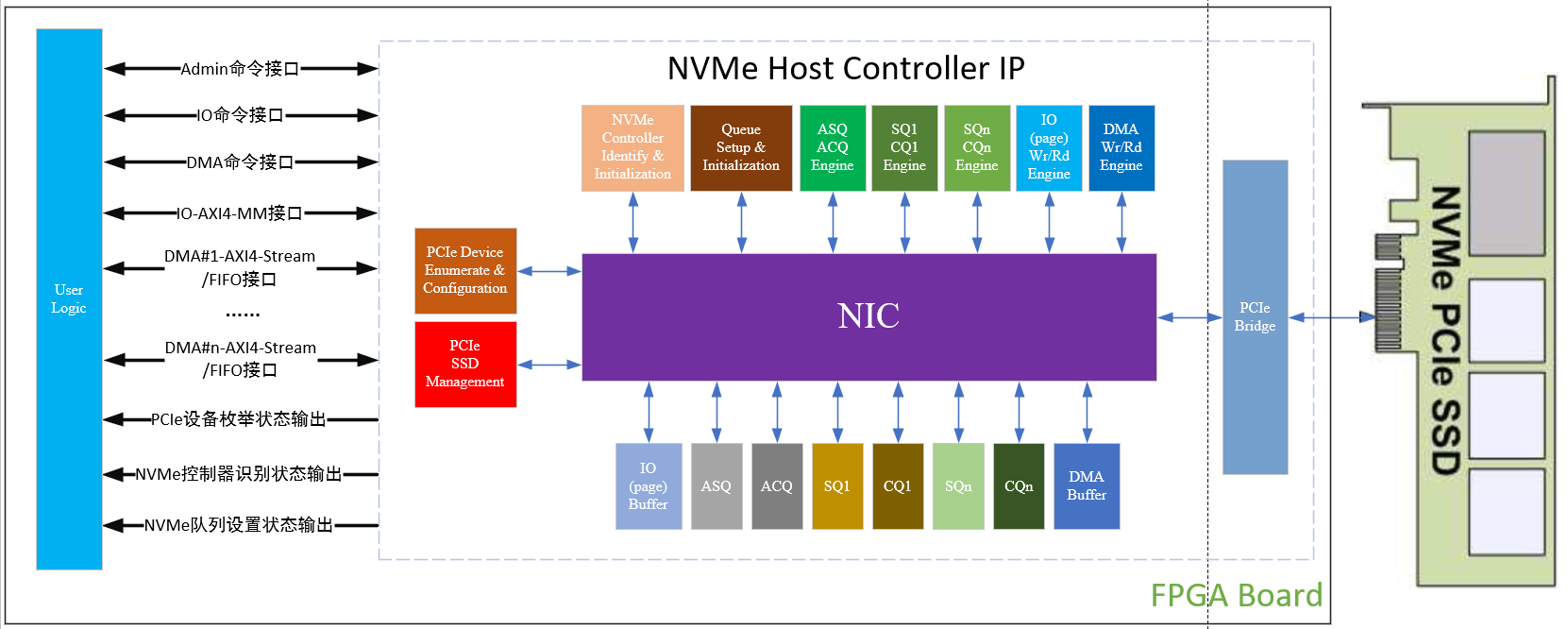

Xilinx FPGA NVMe Host Controller IP,NVMe主机控制器

Xilinx FPGA NVMe主机控制器IP,高性能版本介绍应用

Xilinx FPGA高性能NVMe SSD主机控制器,NVMe Host Controller IP

高性能NVMe主机控制器,Xilinx FPGA NVMe Host Accelerator IP

NVMe控制器IP设计之接口转换

NVMe高速传输之摆脱XDMA设计44:工程设计考量?

Xilinx高性能NVMe Host控制器IP+PCIe 3.0软核控制器IP,纯逻辑实现,AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和4.0

安全控制器CIP Safety对应EtherNet/IP接口模块用户手册(详细篇)

Xilinx FPGA NVMe控制器,NVMe Host Controller IP

NVMe控制器IP设计系列之接口转换模块

NVMe控制器IP设计系列之接口转换模块

评论