在芯片设计的世界里,有一种被称为"火眼金睛"的技术,它就是DFT(Design for Testability,可测性设计)。今天,就让我们一起揭开这项技术的神秘面纱,看看它是如何成为芯片质量的守护神的。

DFT:芯片质量的守护神

DFT,全称Design for Testability,即可测性设计。它是一种在芯片设计阶段就考虑测试问题的技术,目的是为了提高芯片的可测试性,确保芯片在制造过程中能够被有效地检测和诊断。把有缺陷的芯片筛选出来,防止有缺陷的芯片流入到客户手上。同时考虑成本和收益,向量覆盖率越高,越有利于筛选出有缺陷的芯片。

DFT的工作原理

DFT的工作原理主要基于扫描链(Scan Chain)、内置自测试(BIST,Built-In Self-Test)、IO测试与边界扫描(Boundary Scan)三种技术。

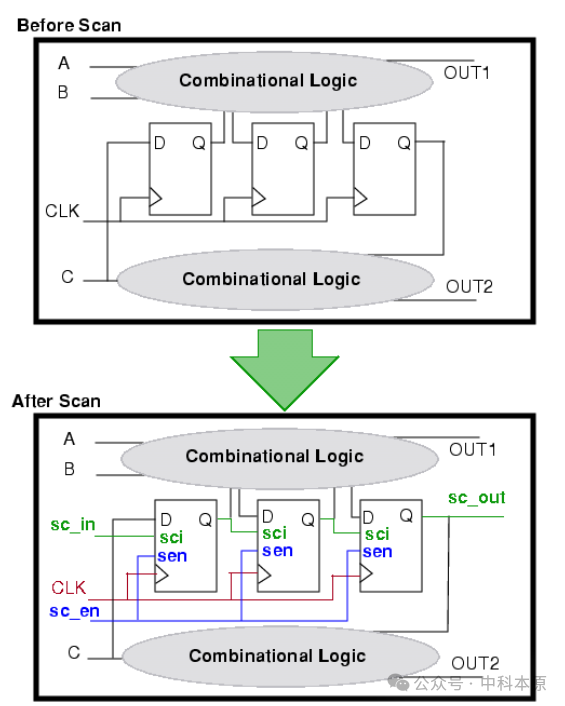

扫描链(Scan Test):通过插入扫描链(Scan Chain),使得内部逻辑状态都可控制,既控制内部逻辑的输入,也控制内部逻辑的输出,生成测试向量检测实际输出与期望输出是否一致,来筛选出有Stuck-at故障、transition故障等的芯片。在测试模式下,我们可以通过这条链将测试数据输入芯片,并读取芯片的输出数据,从而检测芯片的功能是否正确。

图1 Design Before and After Adding Scan

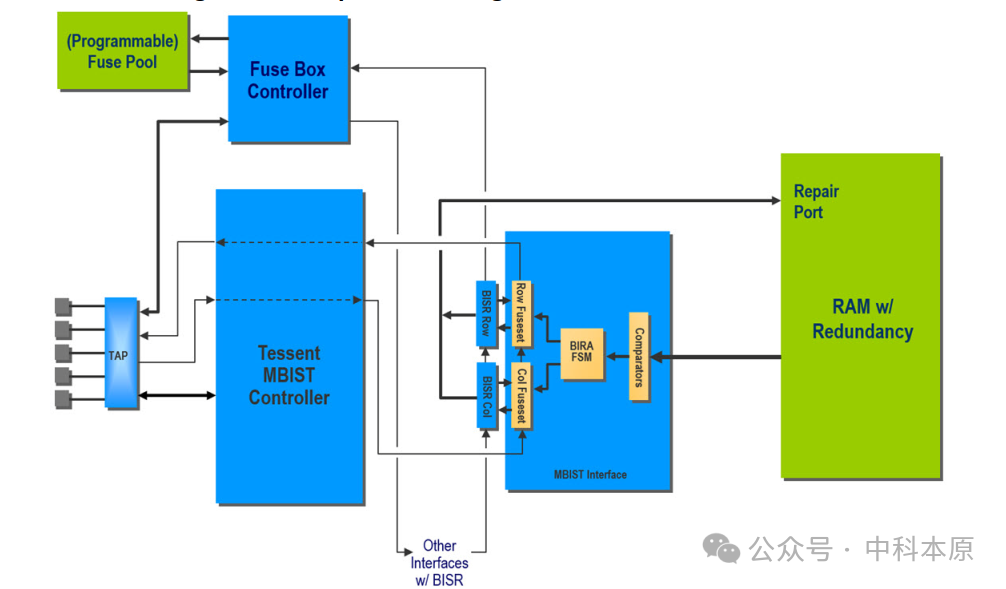

内置自测试(mbist):内置自测试是一种在芯片内部集成测试电路的技术。它可以在芯片工作时自动进行测试,无需外部测试设备的参与。针对SRAM、DRAM等存储器单元,通过旁路逻辑和BIST算法检测物理缺陷(如短路、断路),筛选出有故障的芯片。这种技术特别适用于检测芯片的存储器和逻辑电路。

图2 Configuration with BISR Controller

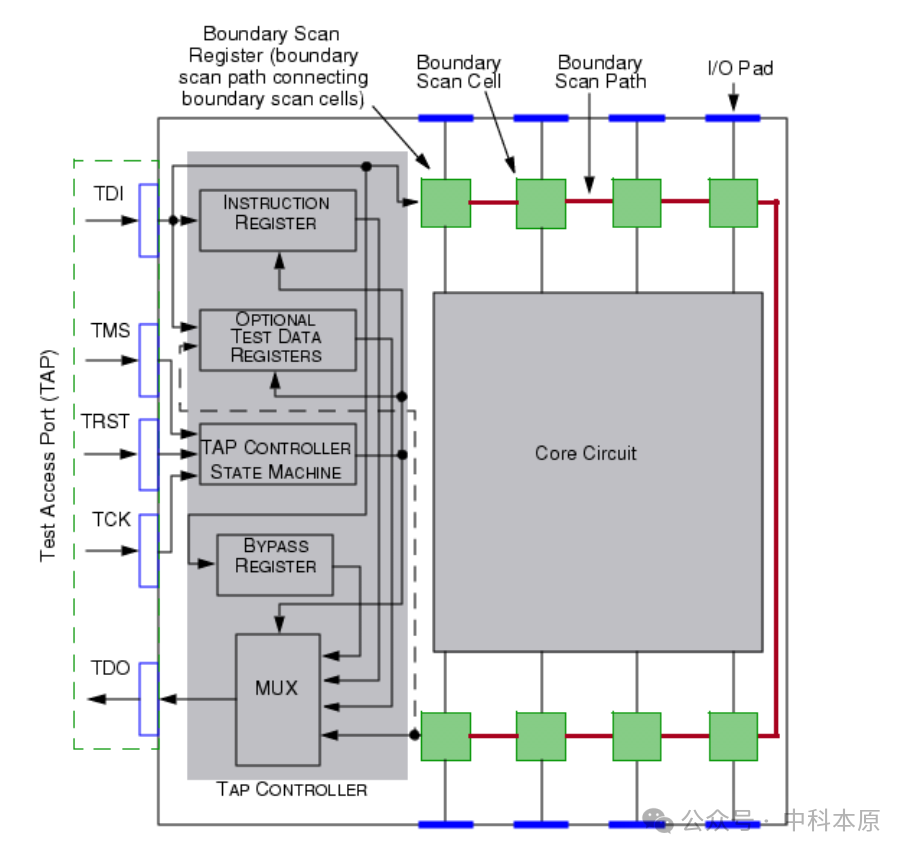

IO测试与边界扫描(Boundary Scan) :验证芯片引脚连接性,筛选出管脚有制造缺陷的芯片。通过以上测试,在晶圆未切割前进行初步测试,筛选出存在制造缺陷的芯片,避免后续封装成本的浪费。这个测试原理就和EDA验证一样,都是通过golden值来判断逻辑的正确性

图3 Boundary Scan Architecture

DFT的应用

DFT技术在芯片设计中的应用非常广泛。无论是处理器、存储器,还是各种专用芯片,都离不开DFT的支持。

中科本原实时控制系列DSP芯片凭借其完善的DFT架构,确保了芯片在复杂应用场景下的高可靠性和稳定性。具体来说,DFT设计通过在芯片内部集成多种测试机制,如扫描链、内建自测试(BIST)和边界扫描(Boundary Scan),能够在芯片制造和运行过程中实时监测和诊断潜在故障。这种设计不仅提高了芯片的可测试性,还显著降低了生产测试成本和时间,同时增强了芯片在高温、高湿、强电磁干扰等恶劣环境下的抗干扰能力。此外,DFT设计还支持芯片的全生命周期管理,从设计、制造到现场应用,均可通过高效的测试手段确保芯片性能的一致性,从而满足工业控制、汽车电子、航空航天等对可靠性要求极高的领域需求。

DFT的未来

随着芯片技术的不断发展,DFT技术也在不断进步。未来的DFT技术将更加智能化,能够自动识别和诊断芯片的问题。同时,DFT技术也将更加高效,能够在更短的时间内完成芯片的测试。

将来,中科本原也会在DSP系列芯片的DFT设计中不断地进行突破和创新,设计出低功耗、高效率的DFT方案,满足不同场景对芯片的实时性和能效的高要求。

结语

DFT技术,这个芯片设计中的"火眼金睛",以其独特的方式守护着芯片的质量。它让我们能够在芯片设计阶段就预见并解决问题,确保芯片的稳定性和可靠性。随着科技的进步,DFT技术也将不断进化,为芯片设计带来更多的可能性。让我们期待中科本原在DFT设计领域的无限可能,不仅为自身产品赋予更高的竞争力,也为推动国产芯片的崛起贡献力量。

-

芯片设计

+关注

关注

15文章

1128浏览量

56452 -

DFT

+关注

关注

2文章

236浏览量

23890

原文标题:

文章出处:【微信号:中科本原,微信公众号:中科本原】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

浅谈DFT可测性设计的工作原理

浅谈DFT可测性设计的工作原理

评论