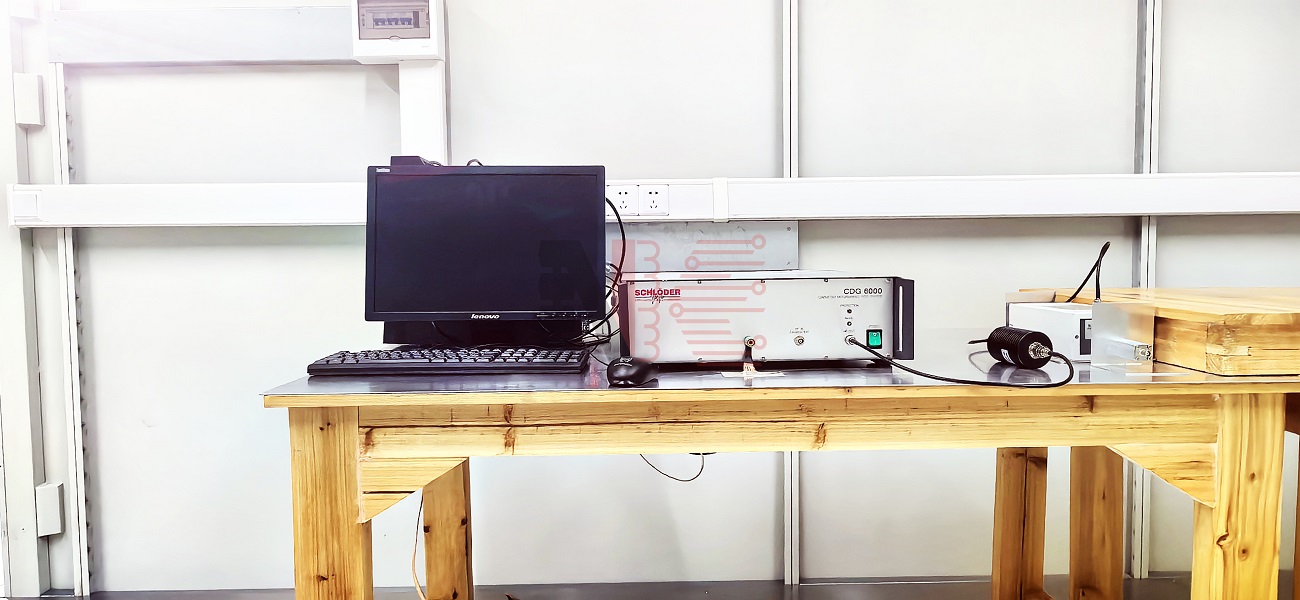

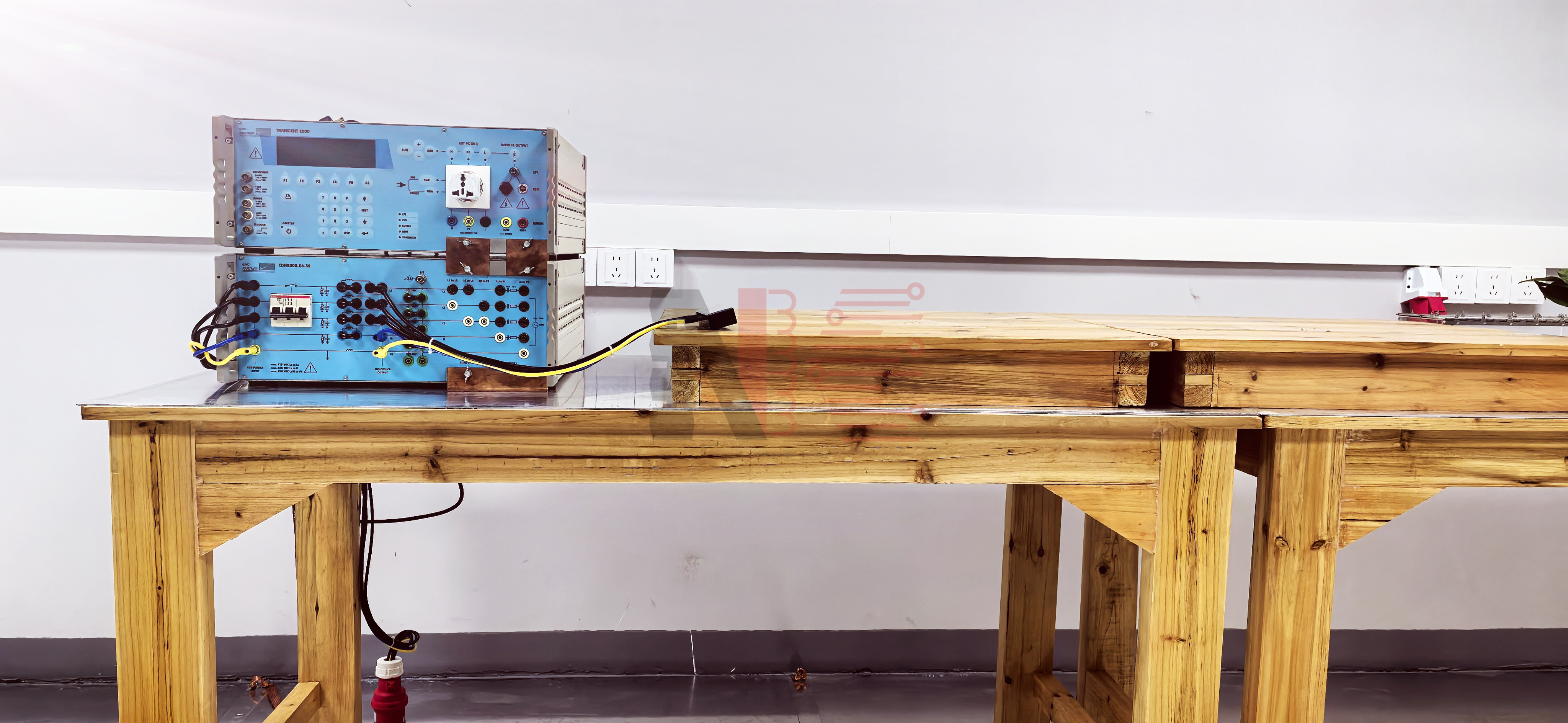

通过此视频可快速浏览 PADS DFT 审核的一些主要功能、优点和易用性。在设计流程的早期使用 PADS DFT 审核可大幅降低 PCB 的批量投产时间,确保 100% 的测试点覆盖和制造前所有网络的可测试性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pcb

+关注

关注

4391文章

23742浏览量

420756 -

网络

+关注

关注

14文章

8130浏览量

93089 -

PADS

+关注

关注

81文章

821浏览量

110578

发布评论请先 登录

相关推荐

热点推荐

【产品介绍】PADS软件

概述PADS是业界应用最普遍的电子设计解决方案,其中涵盖了原理图设计、模拟仿真、PCB布局布线设计、信号和电源完整性分析(SI/PI)、热分析、可制造性分析等全套的功能需求。

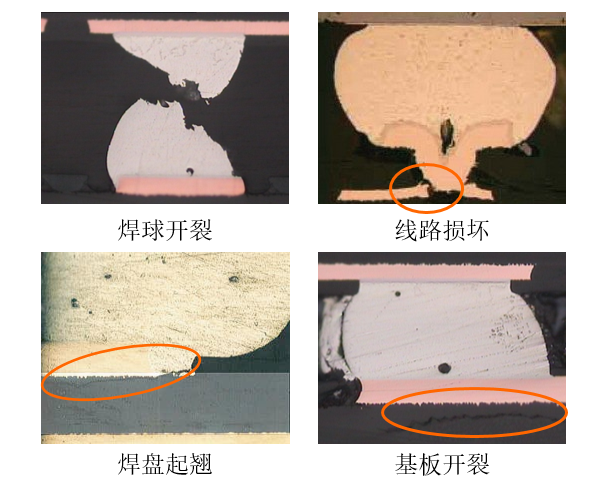

借助DFT技术实现竞争力最大化

通过改进和优化设计与制造的各个方面,半导体行业已经能够实现 IC 能力的巨大进步。可测试性设计 (DFT)——涵盖从在 RTL 中插入测试逻

浅谈DFT可测性设计的工作原理

在芯片设计的世界里,有一种被称为"火眼金睛"的技术,它就是DFT(Design for Testability,可测性设计)。今天,就让我们一起揭开这项技术的神秘面纱,看看它是如何成为芯片质量的守护神的。

DFT的常见误区与解决方案

不足,可能会导致高频信号与低频信号发生混叠,使得频谱分析不准确。 解决方案:在进行DFT分析之前,应确保采样频率满足奈奎斯特采样定理,即采样频率至少是信号中最高频率的两倍。若采样频率不足,可以通过增加采样频率或进行预滤波来

DFT的优缺点比较 DFT在机器学习中的应用

DFT(离散傅里叶变换)的优缺点比较 优点 频域分析 :DFT能够将信号从时域转换到频域,这对于分析信号的频率成分非常有用。 线性和时不变性 :DFT是线性和时不变的,这意味着它满足叠加原理,对于

DFT在信号处理中的应用 DFT与FFT的区别

是DFT在信号处理中的一些主要应用: 频谱分析 :DFT可以用来分析信号的频率成分,这对于理解信号的特性和识别信号中的周期性成分非常有用。 滤波 :在频域中,滤波器的设计和应用更为直观。DFT

PADS DFT审核确保设计的可测试性

PADS DFT审核确保设计的可测试性

评论