受人工智能和超连接性普及的推动,预计半导体行业规模将在未来十年内翻一番。然而,尽管微芯片(从智能手机到救命医疗设备等一切产品的基础)的需求量空前高涨,但它们也面临着迫在眉睫的技术困境。

高数值孔径 EUV 光刻中的微型化挑战

晶体管不断小型化,缩小至 3 纳米及以下,这需要完美的执行和制造。在整个 21 世纪,这种令人难以置信的缩小趋势(从 90 纳米到 7 纳米及更小)开创了技术进步的新时代。

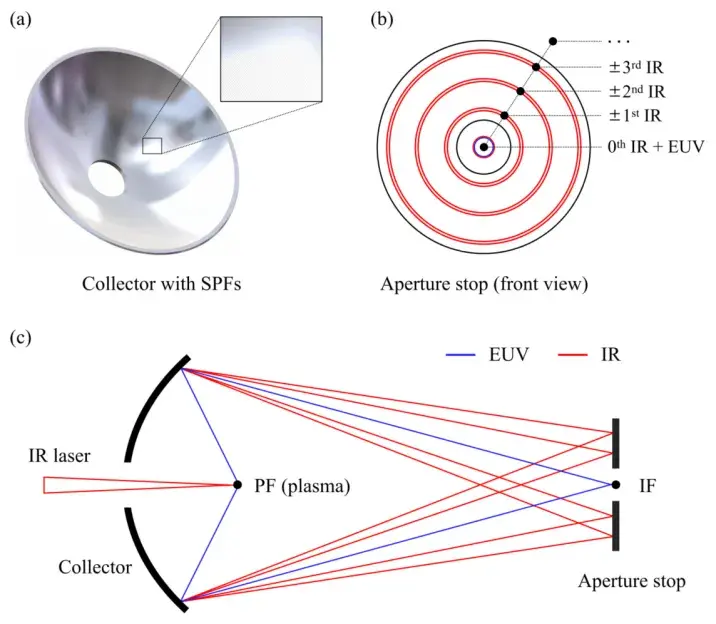

在过去十年中,我们见证了将500 亿个晶体管安装到单个芯片上的惊人壮举。这一成就得益于极紫外 (EUV) 光刻技术,这是一种使用 EUV 光的尖端工艺。EUV 光刻技术可以打印比以前更精细的集成电路 (IC) 图案,因为它的波长 (13.5 nm) 比传统深紫外 (DUV) 光刻技术 (193 nm) 中使用的波长短得多。

半导体制造业的领导者们正争相将这些系统部署到大批量生产中,第一批高数值孔径 (High-NA) EUV 工具已经安装完毕。这些复杂的机器有望进一步缩小特征尺寸,同时提高生产效率。然而,尽管取得了进展,但在 EUV 光刻过程中实现零缺陷的关键挑战仍然存在。

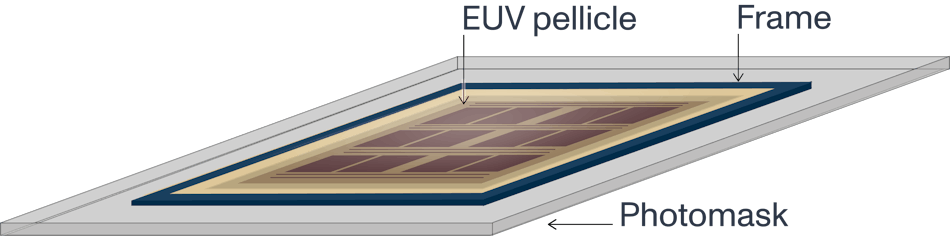

图中显示的是用于 EUV 光刻的 Canatu 碳纳米管 EUV 薄膜和光掩模的示例。

EUV 芯片制造中的缺陷困境

缺陷继续对当今生产的芯片的性能和可靠性产生负面影响。在芯片制造过程的每个步骤中,尽量减少错误非常重要。EUV 掩模是一种高精度模板,用于半导体制造过程中在硅片上创建复杂的图案。它充当模板,阻挡晶圆的某些区域暴露在 EUV 光下,从而将所需的图案蚀刻到硅片上。

在初始阶段,在 EUV 掩模进入扫描仪之前,可能会出现三种常见类型的缺陷:表面缺陷(构成许多观察到的缺陷)是由分层过程中暴露的底层材料引起的。其次,层内捕获的微小颗粒可能来自初始材料或构造过程中的处理。最后,分层过程可能会无意中在掩模表面产生缺陷,这些缺陷要么被完全覆盖,要么被部分覆盖。

下一阶段,光掩模也可能出现缺陷,因为 EUV 扫描仪本身可能就是缺陷的来源。扫描仪内的极端条件(如高温和高功率)可能会在曝光过程中将缺陷引入掩模。

在高功率 EUV 光刻过程中,温度会升至接近1,000°C,传统的 EUV 防护膜可以提供保护,但它们在加工过程中的劣化可能会通过热变形或污染物释放等机制损害掩模版和扫描仪。最重要的是,如果由传统金属硅化物制成的防护膜破裂,它们会像玻璃一样碎裂,造成不必要的、代价高昂的停机。

碳纳米管(CNT) 膜擅长过滤污染物以保护光掩模,但它们的功能远不止这一主要功能,Canatu对此也非常了解。虽然为 EUV 薄膜设计的超薄 CNT 网络可以最大限度地提高 EUV 透射率,同时保持出色的颗粒过滤效果,但更厚、更坚固的 Canatu CNT 膜也可用作光化掩模检查的碎片过滤器。这种特殊技术用于在 EUV 掩模进入扫描仪之前检查光掩模。

即使如今半导体制造技术取得了诸多进步,防止光掩模上的有害颗粒造成缺陷仍然是一项制造挑战。理想情况下,通过控制和减少杂质的存在,晶圆厂可以提高产量,从而实现更一致的芯片性能。然而,这一领域的性能仍然顽固地停滞不前。

碳纳米管在 EUV 光刻效率中的作用

近年来,CNT 在 EUV 光刻过程中保护光掩模免受缺陷影响的潜力才逐渐受到关注。事实上,CNT 光刻胶是提高 EUV 光刻产量和性能的关键因素:CNT 光刻胶由于其更高的透射率,估计可将生产率提高 7% 至 15%,从而使半导体性能更上一层楼。

Canatu 为 EUV 薄膜开发了先进的 CNT 膜(图 2),具有独特的性能组合。未涂层的 Canatu CNT 膜在 EUV 下具有高透射率(》 97%T)、最小眩光(《 0.2%)和真空下高热稳定性(》 1,500°C)。

Canatu CNT 可用于 EUV 薄膜、X 射线窗口和其他 EUV 应用。

高透射率意味着更多的 EUV 光穿过薄膜到达晶圆,从而提高产量。低光斑(散射)确保即使是最微小的特征也可以高精度地打印在晶圆上,而不会造成图案失真。高耐热性、化学惰性和高压差耐受性确保基于 CNT 膜的 EUV 薄膜能够承受下一代高功率扫描仪环境的强烈抽真空和通风循环,同时保持其光学特性。

ASML 称,最先进的高数值孔径 EUV 扫描仪将引入超过 500 W 的高功率水平,提高光学系统的聚焦和收集光线的能力(即数值孔径 [NA] 从 0.33 到 0.55),提供更高分辨率的成像能力。功率水平的提高直接有助于提高每小时晶圆产量 (WPH)。例如,400 W 光源每小时可打印 160 片晶圆,而 500 W 光源每小时可打印超过185 片晶圆。

然而,较高的功率水平和掩模版(光罩)应力将产生传统材料无法承受的高热负荷,从而导致薄膜变形,或者在其他情况下导致薄膜像玻璃一样破碎。

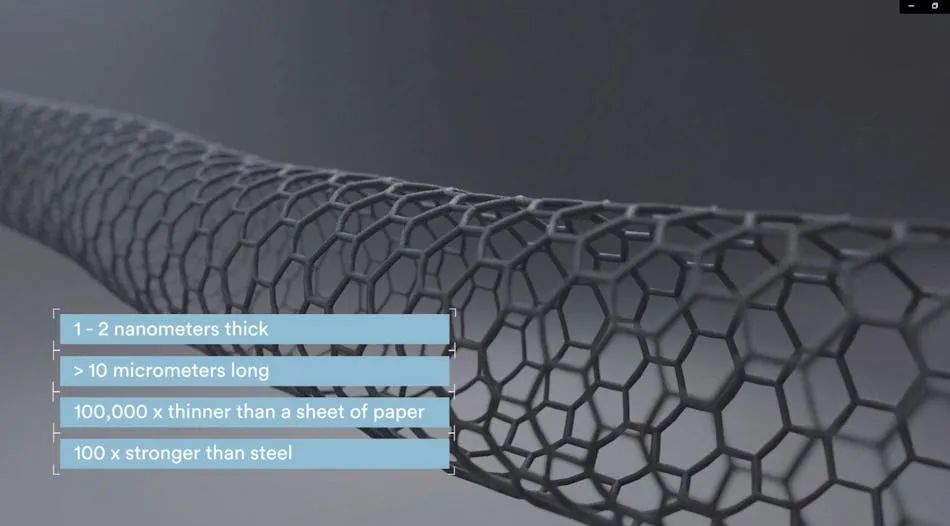

与 ASML 在 2023 年 SPIE 大会上的最新评论相呼应,碳纳米管(图 3)正在成为高功率扫描仪 EUV 薄膜最有前途的材料。继续研究和开发基于 CNT 膜的 EUV 薄膜技术对于充分发挥其潜力至关重要,但它对芯片制造未来的前景是不可否认的。

Canatu CNT 具有许多特性,包括:比纸张薄 100,000 倍、强度比钢高 100 倍、厚度为 1 至 2 纳米。

CNT 薄膜:精密芯片的纯度

随着 EUV 光刻技术彻底改变了半导体制造业,CNT 膜成为保护光掩模在掩模检查和 EUV 光刻工艺中免受污染的理想选择,同时确保芯片生产更清洁、更精确。CNT 的卓越性能使其成为 EUV 光刻技术的多功能和面向未来的材料,可减少缺陷、提高成品率,并最终实现生产更小、更快、更可靠的芯片——这是我们不断发展的技术格局的基石。

-

碳纳米管

+关注

关注

1文章

158浏览量

17752 -

光刻

+关注

关注

8文章

367浏览量

31396 -

EUV

+关注

关注

8文章

615浏览量

88959

原文标题:碳纳米管,超越摩尔定律的可能

文章出处:【微信号:DT-Semiconductor,微信公众号:DT半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

中国打造自己的EUV光刻胶标准!

光刻胶涂层如何实现纳米级均匀性?椭偏仪的工艺控制与缺陷分析

光刻机的“精度锚点”:石英压力传感器如何守护纳米级工艺

白光干涉仪在EUV光刻后的3D轮廓测量

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

用吉时利2450数字源表提升测试效率的实测应用

EUV光刻胶材料取得重要进展

中科院微电子所突破 EUV 光刻技术瓶颈

Keithley 2450数字源表纳米级材料测试的精密利器

改善光刻图形线宽变化的方法及白光干涉仪在光刻图形的测量

碳纳米管在EUV光刻效率中的作用

碳纳米管在EUV光刻效率中的作用

评论