本文介绍了集成电路制造中良率损失来源及分类。

良率的定义

良率是集成电路制造中最重要的指标之一。集成电路制造厂需对工艺和设备进行持续评估,以确保各项工艺步骤均满足预期目标,即每个步骤的结果都处于生产所需的工艺窗口范围内。这些窗口可能包括缺陷密度范围或薄膜厚度的最大与最小可接受值等。由于集成电路制造过程极为复杂,涉及数千个步骤,任何一个环节的微小失误都可能严重影响最终产品的功能,甚至导致报废,从而降低良率。因此,提高良率始终是所有晶圆厂的核心目标。良率是集成电路制造中最重要的指标之一。集成电路制造厂需对工艺和设备进行持续评估,以确保各项工艺步骤均满足预期目标,即每个步骤的结果都处于生产所需的工艺窗口范围内。这些窗口可能包括缺陷密度范围或薄膜厚度的最大与最小可接受值等。由于集成电路制造过程极为复杂,涉及数千个步骤,任何一个环节的微小失误都可能严重影响最终产品的功能,甚至导致报废,从而降低良率。因此,提高良率始终是所有晶圆厂的核心目标。

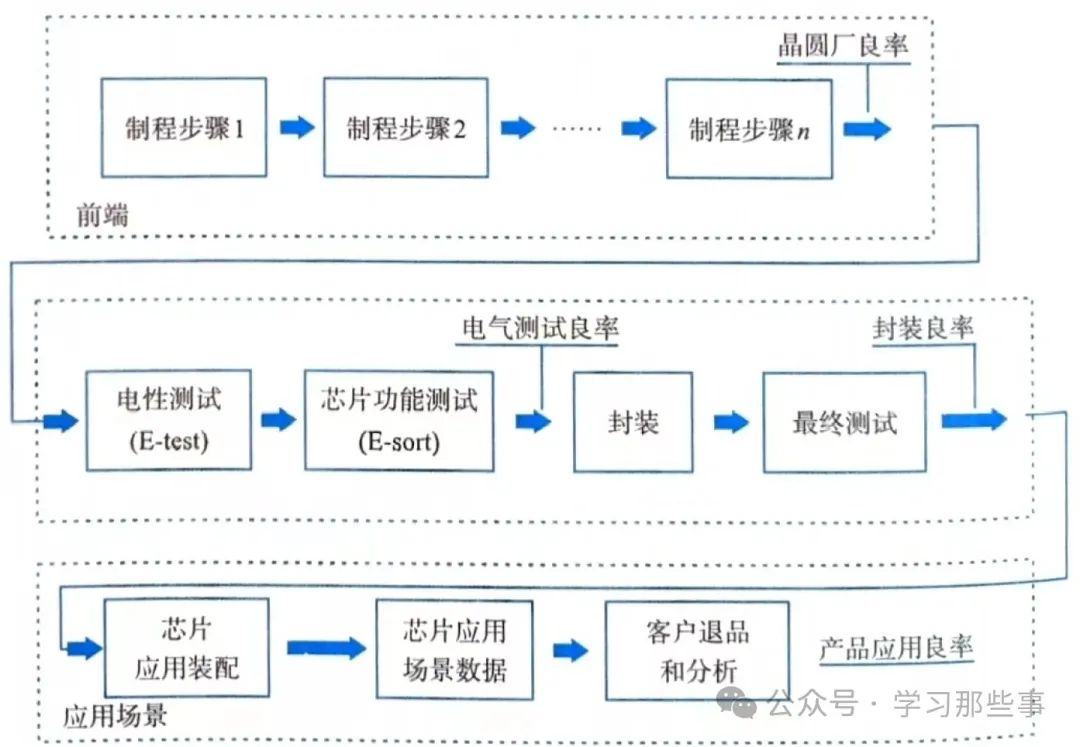

制造过程中的各种芯片良率

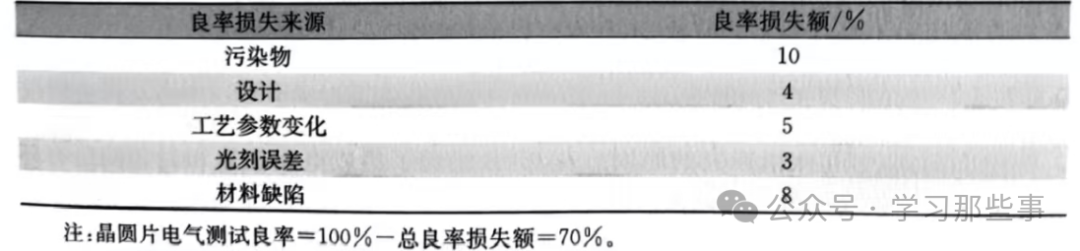

在多数制造行业中,良率通常指可用产品数量与总生产数量的比值。在集成电路行业中,良率则由晶圆上制造出的器件的功能性和可靠性来衡量。良率的定义一般可分为以下四类: (1)晶圆制造良率(或晶圆厂良率):指从晶圆厂成功生产出来的合格晶圆数量与投入生产的晶圆总数量之比。 (2)电气测试良率:指通过电气测试并正常工作的裸片数量与晶圆片中裸片总数之比。 (3)封装良率:指切割并封装后的芯片中,通过最终电气测试(FT)的芯片数量与总芯片数量之比。 (4)产品应用良率:指实际使用中合格芯片的比例。具体计算为应用装配芯片总数减去客户退回芯片数量后的结果,再除以应用装配芯片总数。产品应用良率理论上应达到100%。如果未达标(即出现性能问题导致退货),需对产品失效进行分析,追溯设计、制造、测试、封装等环节,以找到根本原因。 在半导体集成电路芯片制造中,良率通常指电气测试良率,这是所有良率指标中最复杂、最难提升的部分。与之相比,其余三种良率在多数情况下都可以接近甚至达到100%。然而,想要使电气测试良率达到100%几乎是不可能的。在本文中,“良率”一词若无特别说明,均特指电气测试良率。 提高良率是所有半导体集成电路制造企业追求的核心目标之一,因为良率直接反映了最终可以销售的产品数量与总生产数量之间的比例。良率的提升对晶圆制造的成本具有重要影响。在大规模生产的背景下,哪怕良率仅提升0.5%或1%,都能够大幅降低每片晶圆的平均制造成本。良率的高低与设备性能(工艺能力)、员工培训质量、生产组织效率以及晶圆厂的整体设计和建设水平密切相关。 良率损失的来源 在集成电路制造的各个环节中,良率损失的原因多种多样,可能由缺陷、故障、工艺波动或设计问题等因素导致。下表概述了某条生产线晶圆片电气测试良率损失的主要来源。在集成电路制造的各个环节中,良率损失的原因多种多样,可能由缺陷、故障、工艺波动或设计问题等因素导致。下表概述了某条生产线晶圆片电气测试良率损失的主要来源。

各阶段良率损失范例

从总体上看,良率损失可分为两种类型:硬性损失(灾难性)和软性损失(参数性)。

硬性损失(灾难性)

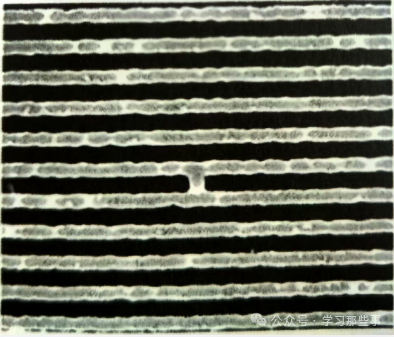

硬性损失指芯片因严重功能故障而完全无法正常工作,例如开路或短路等。这类损失的主要原因包括人为的重大操作失误(例如选用错误的离子注入参数)、材料颗粒缺陷以及材料缺失等。一个典型的案例是铜互连工艺中出现的金属线桥接问题,如图所示。由于金属边缘存在多余的材料,导致相邻金属线之间形成桥接,最终引发短路故障。

金属线桥接故障

2. 软性损失(参数性) 软性损失则是指芯片的基本功能正常,但未能满足某些性能或功耗指标。这类良率损失通常由一个或多个电路参数的变化引起。当这些参数偏离设计中的预期分布时,芯片的某些性能可能不符合规格要求。例如,一个芯片可能在特定电压下正常运行,但在其他所需工作电压范围内无法满足要求。深亚微米工艺技术中的漏电流问题也是典型的参数性良率损失案例。单个晶体管可能因工艺不完善而产生细微的漏电流,而当大量晶体管的漏电流累积达到某个临界值时,就会引发芯片的失效。此外,在微处理器生产中,由于工艺差异导致的晶体管性能波动会直接影响芯片的处理速度。这种性能差异使得速度较低的微处理器只能以较低价格出售,给厂商带来经济损失。在某些特殊情况下,例如应用专用集成电路(ASIC)中,如果性能低于某一设定阈值,可能导致产品完全无法销售,造成更严重的经济后果。

3. 与测试相关的良率损失 此外,还存在部分与测试过程相关的良率损失。由于任何测试流程都无法完全覆盖所有可能的故障与潜在问题,因此会导致一定比例的产量损失。这种损失与测试程序的覆盖度、合理性以及工艺缺陷水平息息相关。然而,这类损失并非直接由制造工艺本身引起,因此不属于本文讨论的范畴。

良率损失的分类

如前所述,良率损失的原因多种多样,覆盖了集成电路制造和封装的各个环节。根据不同的划分标准,良率损失可以分为以下几种类型:

工艺变化性良率损失 vs. 环境变化性良率损失 在集成电路制造过程中,工艺的波动(如掩模未对准、步进器聚焦不佳等)会引发物理性的良率损失。这类工艺变化性损失可以通过提升工艺稳定性来减少。而在集成电路的实际使用中,周围环境的变化(如温度、电压等物理因素的波动)可能导致环境变化性良率损失。某些特殊应用的芯片需要在极端环境下运行(如高温、高压、高气压等),在这种情况下,即使在常规环境中能正常工作的芯片,到了极端环境下也可能发生失效,进而导致良率下降。减少此类损失对工艺的稳定性和精确性提出了更高的要求。 工艺变化性导致的良率损失通常可以在芯片的早期功能性电气测试中被发现,便于工程师迅速分析原因并采取措施。而环境变化性损失则可能在成品芯片的实际应用阶段才被发现,这可能会导致产品被客户退回,从而延长良率学习周期(yield learning cycle)。

系统性良率损失 vs. 随机性良率损失

系统性良率损失是指具有一定规律的损失,例如金属凹陷或光刻邻近效应,这类损失通常会影响同一批次的晶圆,而非单片晶圆。这类问题较容易被检测出来,且可以通过建模和预测找到根本原因。相比之下,随机性良率损失由难以预知的随机变化(如材料波动、掺杂剂浓度的细微偏差等)引起,难以进行预测或分析,因而改进这类良率损失的难度较大。

晶粒裸片间良率损失 vs. 晶粒裸片内良率损失

根据工艺波动的空间尺度,良率损失可进一步划分为晶粒裸片间的良率损失和晶粒裸片内的良率损失。晶粒裸片间的变化可能出现在同一晶圆片的不同裸片之间,也可能存在于不同晶圆片或批次之间,例如材料成分的差异。就像自然界没有完全相同的两片树叶一样,这种微小的差异是不可避免的,因此芯片设计时会考虑这种变化,并在一定范围内允许参数的波动。然而,当参数变化超出设计容忍范围时,就会导致良率下降。 另一方面,晶粒裸片内的良率损失是指单个晶粒裸片内部的参数波动,例如同一晶粒裸片中相同电路元件的性能差异。为了应对这种内部变化,通常在设计中会加入保护带或采用补偿设计,以减小内部扰动的影响并降低相关良率损失。

尺寸变化性良率损失 vs. 拓扑变化性良率损失

尺寸变化主要体现在器件边缘的形态差异、裸片内部横向尺寸的偏差以及跨裸片的线宽变化等方面。这些变化通常会引发器件性能参数的波动。在尺寸变化性良率损失中,常见的原因包括栅极长度的偏差、线端回拉以及连接柱的重叠。这类变化多发生在光刻和刻蚀工艺过程中,并且与芯片的布局设计模式密切相关。随着器件尺寸的不断缩小,即使是微小的尺寸变化也可能对电路性能造成显著影响。例如,在32nm及以下工艺节点中,线边缘粗糙度(Line Edge Roughness, LER)已经成为影响器件性能和良率的关键问题之一。 拓扑变化性良率损失通常由化学物质导致的介电质腐蚀或金属凹陷引起。在制造过程中,这种现象多见于生产线后段金属互连线的缺陷,以及前段工艺(FEOL)中浅沟槽隔离(STI)结构的缺陷。此外,化学机械研磨(Chemical Mechanical Polishing, CMP)工艺的不完善也往往导致拓扑不均匀性。拓扑变化会引发诸多问题,如互连电阻和电容的波动,同时还会影响后续光刻工序的对焦精度,进而引起线宽变化并导致良率下降。

-

集成电路

+关注

关注

5465文章

12702浏览量

375892 -

制造

+关注

关注

2文章

563浏览量

24865 -

良率

+关注

关注

0文章

6浏览量

5564

原文标题:集成电路制造中良率损失来源及分类

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

详解集成电路中的无源元件

UPS电源在半导体集成电路制造中选型与应用

台阶仪在集成电路制造中的应用:高端光刻胶材料纯化研究进展

集成电路制造中薄膜生长设备的类型和作用

集成电路制造中薄膜生长工艺的发展历程和分类

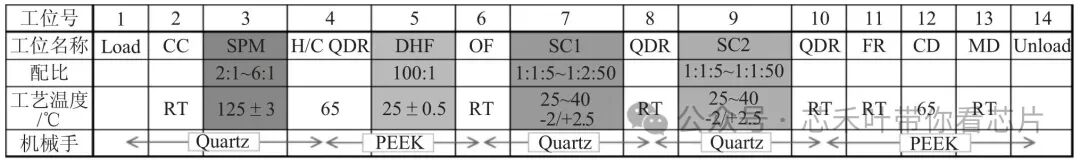

集成电路制造中常用湿法清洗和腐蚀工艺介绍

集成电路制造中薄膜刻蚀的概念和工艺流程

PDK在集成电路领域的定义、组成和作用

广立微DE-YMS系统助力紫光同芯良率管理

解锁集成电路制造新建项目的防震黑科技-江苏泊苏系统集成有限公司

集成电路制造中良率损失来源及分类

集成电路制造中良率损失来源及分类

评论