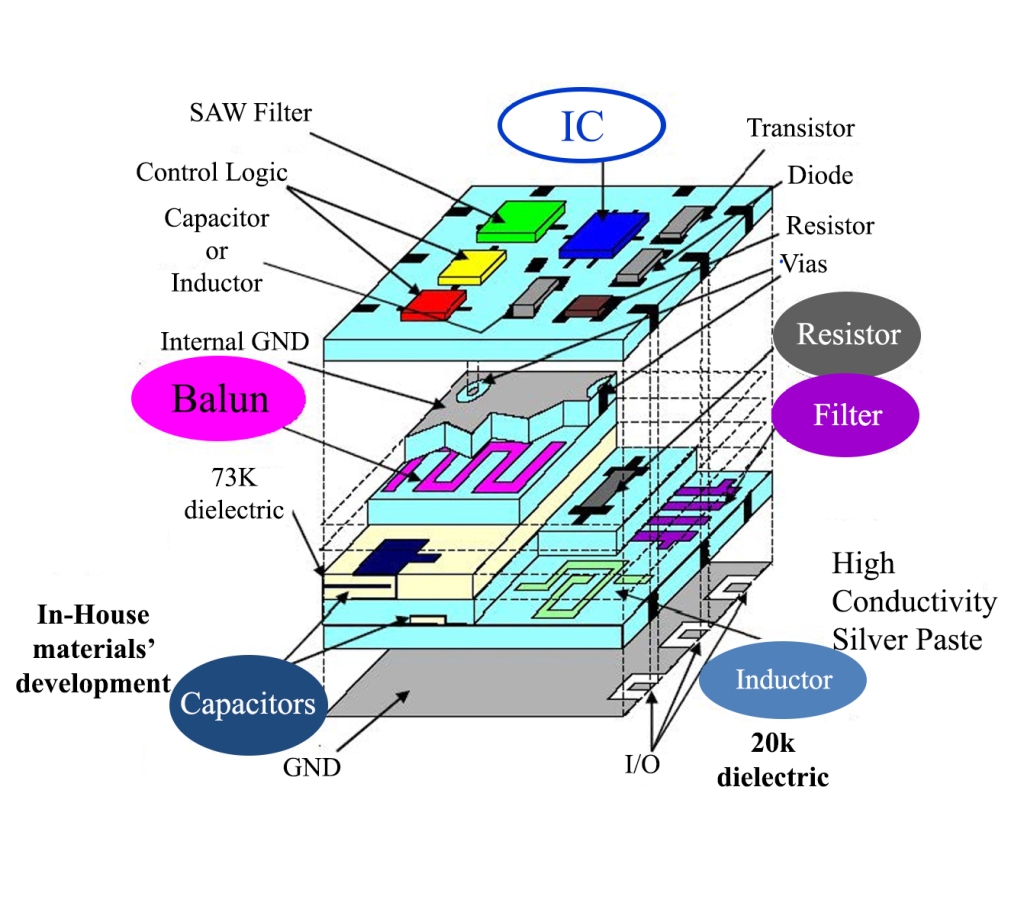

部分集成电路,除了晶体管等有源元件,还需要应用电阻、电容或电感等无源元件。与晶体管相比.匕任任云口用牧大面积,因此,无源器件的制作对于集成电路缩微有重要影响。本节将简要介绍无源器件的主要制造工艺。

3.8.1 扩散电阻和薄膜电阻

集成电路中的电阻根据其形成工艺可分为扩散电阻和薄膜电阻。扩散电阻是在硅层中利用光刻工艺界定的SiO2窗口,通过离子注人或扩散工艺把相反导电类型的杂质掺人硅层,形成利用Pn结与周围隔离的电阻条。薄膜电阻则是在介质膜上沉积一层导电薄膜(如掺杂多晶硅),然后利用光刻技术刻蚀出特定的电阻条图形。电阻条的形状可以是直条型,也可以是曲折型。图3.56展示这两类扩散电阻的俯视图和截面图[G1。设电阻条的电阻率为p,长为L,宽为W,厚为d,则该电阻条的电阻为

其物理意义为当长宽比等于1时该方块的薄层电阻。它可以通过四探针法等技术在大面积电阻层上测量出来。薄膜电阻总的电阻值则由"薄层电阻线条方块数"得到。实际上,这一结论不仅限于均匀掺杂情形,它对于厚度方向不均匀掺杂的情形也适用。

对于实际电阻条,在接触端面附近或曲折型电阻条的转角附近还需要考虑电流不均匀流动的效应。对于图3.56中的直条型电阻,如接触面电阻为0.65R,则其总阻值约为(9十2X0.65)Rs。对于曲折型电阻条,转角处电流主要密集于内侧转角处,所以,转角处的一个方块阻值小于R,也可用0.65R。近似计算[31]。

3.8.2 集成电容

电容在集成电路中有广泛应用,如在3.7节讨论的DRAM等存储芯片中。集成电路中的电容有3种,分别是P结电容、MOS电容和MIM电容。图3.57为这3种集成电容的示意图[13]

当p结反偏时,对于直流来讲处于截止状态,但对于交流来讲它是一个电容,即所谓的pn结势垒电容,它是随偏压可变的电容,可用于某些特殊场合,如高频调谐、通信等电路。

MOS电容可通过在硅衬底上生长热氧化层及上下的导电层形成,如图3.57(b)所示,在n型衬底上形成一个p扩散层作为下电极,在SiO2上淀积一层重掺杂多晶硅、金属硅化物或金属作为上电极。由于下电极为重掺杂层,这种MOS电容的电容值与偏压无关,其单位面积电容值为eo/tos。为增大电容值,可通过减薄SiO2厚度实现,也可通过应用高介电常数(高k)介质实现。与集成pn结电容相比,集成MOS电容还具有串联电阻小的优点。集成MIMI电容的上下电极均由金属构成,介质层则通常采用高k材料。其电容值也与偏压无关,单位面积电容值为e;/t。

3.8.3 集成电感

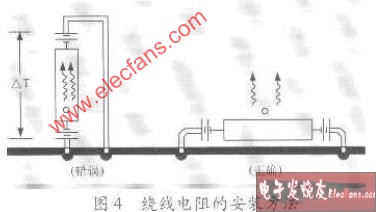

随着硅器件技术不断演进,硅集成芯片在射频(RF)技术中有越来越多应用。在射频集成电路中,电感是关键元件,如何利用微细加工技术,在硅衬底上制作优质集成电感成为重要课题之一。硅衬底上已可制作多种形状集成电感,其中制作较简便、应用较普遍的是薄膜螺旋形电感,如图3.58所示[。这种电感的主要制作工艺步骤如下:先在氧化衬底上淀积金属层,经光刻刻蚀后作为电感的下电极;然后,淀积介质隔离层,刻出通孔;再在其上淀积第二层金属,并通过通孔与下电极相连;最后,经光刻在第二层金属上刻蚀出螺旋形图形的电感结构。

相对于集成电阻和集成电容,集成电感的大小尚无严格解析式可以用来计算,通常需要借助TCAD模拟软件来分析。在集成电感的建模过程中,通常还需要考虑金属电阻、氧化层电容、金属线间电容、衬底电阻、金属对衬底电容以及金属线间互感等寄生效应。图3.58(c)为一简化集成电感模型。其中,L为电感,R:为金属电阻,Cp和Cr为金属对衬底的耦合电容,Rws和Rwutlg为金属线下的衬底电阻。

评价电感的重要参数是品质因子Q,其定义为Q=oL/R,其中,)为频率,L为电感,R为金属线电阻。Q值越高,在电阻上的损耗就越小,电路特性也越好。在较低频率下,Q会随。增加而线性增高,但当频率很高时,由于寄生电阻和电容的影响,Q又会随。下降。可以通过多种方法提高Q值,如使用低k介质降低C应用厚膜金属或低阻金属(如Cu代替AI)以降低R1,还可以用SOI结构来消除Rs的影响。

-

集成电路

+关注

关注

5465文章

12702浏览量

375890 -

晶体管

+关注

关注

78文章

10449浏览量

148733 -

无源元件

+关注

关注

1文章

1297浏览量

17533

原文标题:集成电路中的无源元件------硅基集成芯片制造工艺原理

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

经验分享:如何选择运放电路设计中的无源元件

集成无源元件技术对PCB技术的影响

什么是集成无源元件?对PCB技术发展产生了什么影响?

集成无源元件对PCB技术发展有什么样的影响

无源元件在硬件设计中如何选择与应用?

详解集成电路中的无源元件

详解集成电路中的无源元件

评论