在人工智能(AI)技术蓬勃发展的今天,芯片的复杂度正以前所未有的速度飙升,轻松跨越了百亿逻辑门级别的大关。这一趋势不仅推动了半导体行业的快速发展,也对硬件仿真系统提出了更高的挑战和要求。在近日的ICCAD-Expo 2024上,思尔芯研发总监余勇发表了精彩技术演讲,他深入探讨了AI时代下高性能硬件仿真系统的重要性。他指出:“随着AI技术的广泛应用,芯片的复杂度急剧增加,传统硬件仿真的系统运行性能已难以满足当前的设计需求。因此,思尔芯迭代升级了其OmniArk芯神鼎国产硬件仿真系统,该系统支持从2亿到96亿门的灵活配置,系统运行性能高达4-6MHz,能够满足复杂芯片设计的仿真需求。”

PART.1

新一代国产硬件仿真

思尔芯新一代国产硬件仿真系统亮点纷呈。它支持从2亿到96亿门的灵活配置,系统运行性能高达4-6MHz,足以应对复杂芯片设计的仿真需求。高效的全自动编译技术,结合增量编译的加速优势,使得编译效率飙升至8000万门/小时,为设计师赢得了宝贵的时间。

在信号调试方面,系统配备了静态探针和动态探针,实现了信号的全可视性。Backup/Replay、Save/Restore等调试功能的加入,更是让调试过程变得便捷而高效。此外,系统还具备强大的多用户能力和动态资源调度管理功能,确保了资源的最大化利用和系统的稳定运行。

丰富的接口与存储解决方案,如Transactors、Memory Models、Daughter Cards、Speed Adaptors等,为不同用户模式的开发提供了全面的验证IP库,满足了绝大部分验证应用的需求。

新一代芯神鼎硬件仿真系统凭借其卓越的性能和丰富的功能,广泛应用于系统架构探索、硬件调试、软件开发、全系统验证以及软硬件协同等多个领域。

PART.2

精准的信号调试

在硬件仿真领域,精准的信号调试是确保芯片设计正确性和稳定性的关键。面对日益复杂的芯片设计,如何高效地定位并解决潜在的问题,成为了每一位硬件工程师面临的挑战。思尔芯新一代硬件仿真系统便提供了诸如Backup/Replay和Save/Restore等强大的调试功能,极大地提升了调试的精准度和效率。

1

随机性问题调试

Backup/Replay的神奇力量

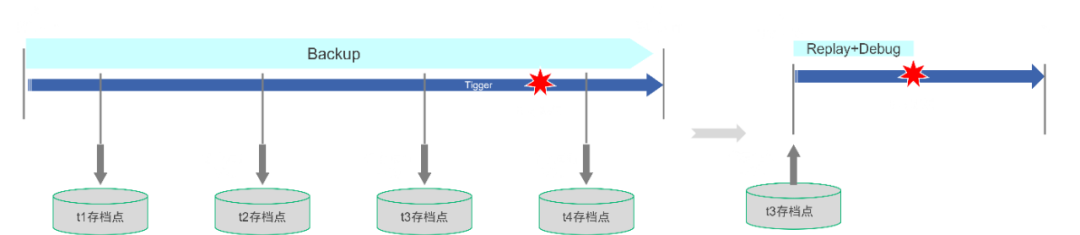

Backup/Replay功能在硬件仿真中扮演着至关重要的角色。它允许工程师在仿真运行过程中,对特定时刻的系统状态进行备份,并在需要时重新播放(Replay)这一时刻之后的所有操作。这一功能在解决随机性触发的bug时尤为有效。

应用场景1:稳定的重现bug现象

面对那些难以捉摸、随机性触发的bug,传统的调试方法往往难以重现问题。而Backup/Replay功能则能够稳定地重新呈现bug现象,使工程师能够避免重新仿真运行却无法重现bug的尴尬局面。通过精确地定位到bug触发的时刻,工程师可以更加深入地分析问题,找到问题的根源。

应用场景2:更加精准的调试窗口,提升调试效率

当正常运行阶段出现bug后,工程师往往需要从海量的仿真数据中寻找线索。而Backup/Replay功能则允许工程师从接近出bug仿真时刻的backup存档点开始replay,并在此阶段开启FFV(Fast Forward Verification,快速前向验证)功能进行调试。这样,工程师无需从头开始仿真运行,从而大大节省了调试时间,提升了调试效率。

应用场景3:更灵活的硬件资源使用

在Replay阶段,由于不需要外部接口环境的支持,工程师可以更加灵活地使用硬件资源来完成调试任务。这一特性使得工程师能够在有限的硬件资源下,更加高效地解决复杂的问题。

2

从指定仿真时间点恢复调试

Save/Restore的便捷之处

Save/Restore功能同样在硬件仿真中发挥着不可替代的作用。它允许工程师在仿真过程中的任意时刻保存系统的运行状态,并在需要时从这一状态恢复运行。

应用场景1:跳过OS启动阶段,节省仿真时间

在嵌入式系统或操作系统的仿真中,OS启动阶段往往耗时较长。通过Save/Restore功能,工程师可以在OS启动后保存运行状态,并在后续仿真中直接从这一状态恢复运行。这样工程师就可以跳过繁琐的OS启动过程,专注于系统功能的验证和调试,从而大大节省了仿真时间。

应用场景2:并行执行多个testcase

在复杂的芯片设计验证中,工程师通常需要执行多个testcase来确保系统的稳定性和正确性。通过Save/Restore功能,工程师可以从某个仿真时间点开始,并行执行多个testcase,提高验证效率和覆盖率。

简单来说,就是当工程师突然有事要中断或者想先暂停一下,他可以保存当前进度,以便日后继续。同时,当硬件资源有限时,工程师们可通过该功能轮流使用机器。通过Save/Restore功能,他们可以一个接一个地用这台机器,避免浪费资源,从而实现资源的最大化利用。

由此可见,Backup/Replay和Save/Restore等精准的信号调试功能为硬件仿真调试带来了前所未有的便捷和效率。它们不仅帮助工程师更加准确地定位和解决潜在的问题,还极大地提升了硬件资源的利用率和工作效率。

PART.3

写在最后

在人工智能(AI)技术快速发展的背景下,思尔芯作为国内首家数字EDA企业,积极响应行业变革,不断创新与突破。面对芯片复杂度飙升带来的挑战,思尔芯推出了迭代升级的OmniArk芯神鼎国产硬件仿真系统,以卓越的性能和丰富的功能,为芯片设计提供了坚实的技术支撑。

思尔芯深知,精准的信号调试是确保芯片设计正确性和稳定性的关键。因此,新一代硬件仿真系统在信号调试方面下足了功夫,为工程师提供了多种便捷的调试工具和功能。这些功能不仅帮助工程师快速定位并解决潜在问题,还极大地提升了硬件资源的利用率和工作效率。

此外,思尔芯还注重用户体验和资源最大化利用。系统支持多用户同时在线,实现了资源的共享和灵活调度。同时,通过提供丰富的接口与存储解决方案,系统满足了不同用户模式的开发需求,为芯片设计的创新和发展提供了有力支持。

思尔芯将继续秉持创新理念,不断提升技术水平和服务质量,以更加优质的国产硬件仿真解决方案,助力芯片设计行业在AI时代下实现更加快速和可持续的发展。

-

芯片

+关注

关注

463文章

54422浏览量

469244 -

AI

+关注

关注

91文章

41101浏览量

302579 -

硬件仿真

+关注

关注

1文章

31浏览量

19594

发布评论请先 登录

思尔芯再获 “2026年度创新EDA公司”,以生态之力赋能复杂芯片

浅谈复杂芯片设计中的SPICE仿真困境

思尔芯、MachineWare与Andes晶心科技联合推出RISC-V协同仿真方案,加速芯片开发

思尔芯荣登“国产EDA工具口碑榜”,以“芯神瞳”原型验证解决方案赋能芯片创新

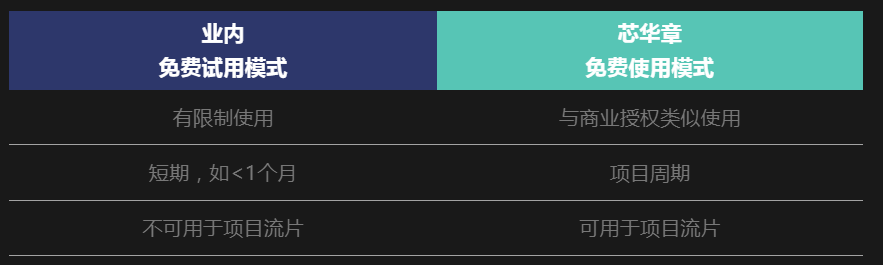

芯华章开放免费使用商用级仿真器GalaxSim,加速中国芯片初创公司发展

【「AI芯片:科技探索与AGI愿景」阅读体验】+AI芯片的需求和挑战

硬核加速,软硬协同!混合仿真赋能RISC-V芯片敏捷开发

【书籍评测活动NO.64】AI芯片,从过去走向未来:《AI芯片:科技探索与AGI愿景》

思尔芯携手Andes晶心科技,加速先进RISC-V 芯片开发

AI时代下芯片复杂度飙升,思尔芯国产硬件仿真加速芯片创新

AI时代下芯片复杂度飙升,思尔芯国产硬件仿真加速芯片创新

评论