电子发烧友网报道(文/吴子鹏)英特尔CEO基辛格此前表示,摩尔定律并没有失效,只是变慢了,节奏周期正在放缓至三年。当然,摩尔定律不仅是周期从18个月变为了3年,且开发先进制程成本高昂,经济效益也变得越来越差。在这种情况下,超越摩尔逐渐成为打造高算力芯片的主流技术。

超越摩尔是后摩尔定律时代三大技术路线之一,强调利用层堆叠和高速接口技术将处理、模拟/射频、光电、能源、传感等功能单元集成在一个系统内,实现系统性能的提升,并降低大型SoC的开发成本。当前,先进封装技术路线非常多,且各家公司主攻方向不同,呈现百花齐放、百家争鸣的状态。

近日,在博闻创意会展(深圳)有限公司主办的elexcon2024深圳国际电子展上,专门设立了主题为“系统级封装SiP”的专业论坛,会议内容涵盖Chiplet芯片设计与测试、Chiplet互联标准与生态、2.5D/3D IC封装技术和SiP封装量产方案等。

博闻创意会展(深圳)有限公司主办的

elexcon2024深圳国际电子展“系统级封装SiP”论坛

Chiplet异构集成的机遇和挑战

如上所述,先进封装是指封装更多的集成电路 (IC) 以提高性能的多种创新技术,包括扇出 (FO) 型封装、晶圆级芯片规模封装 (WLCSP)、倒装芯片球栅阵列 (fcBGA)、倒装芯片CSP (fcCSP)、系统级封装 (SiP) 和2.5D/3D堆叠封装等。因此,在先进封装发展过程中,Chiplet(芯粒)异构集成是重要的底层技术之一。

与传统单片器件相比,Chiplet的设计和制造流程明显不同。芯和半导体联合创始人&总裁代文亮博士在elexcon2024深圳国际电子展“系统级封装SiP”论坛上演讲时表示,Chiplet异构集成正在推动高效能算力升级。传统单片器件的方式存在“存储墙”的问题,数据读取不仅延迟高,而且会产生额外的功耗和热量,通过将3DIC Chiplet、HBM和异构集成芯片技术融合,能够实现更高效能的算力架构体系。

芯和半导体联合创始人、总裁 代文亮博士

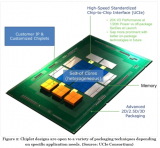

因此,Chiplet异构集成在当前大型SoC的设计制造过程中被广泛采用,代文亮博士在演讲中列举了几个例子,包括英特尔Gaudi 3、AMD Instinct MI300X加速器和英伟达Blackwell 200等。简单解读一下英特尔Gaudi 3,这是英特尔子公司Habana Labs推出的下一代Gaudi高性能人工智能加速器。英特尔Gaudi 3使用2.5D CoWoS封装来链接四个HBM2内存堆栈,每个堆栈8 GB,总共32 GB内存,聚合带宽为1 TB/s。

代文亮博士称,高算力终端正在让Chiplet异构集成系统加速下沉,包括数据中心领域的数据处理存储、AI训练和推理、数据交换传输等需求,AI终端领域的意识识别响应、数据处理存储等需求,以及智能汽车领域的自动驾驶ADAS、智能座舱体验等需求,都广泛采用了Chiplet异构集成系统。不过,他也强调,目前Chiplet异构集成系统尚处于产业早期,生态还不太成熟,需要头部芯片厂商、行业组织机构和下游应用厂商携手努力,共同完善产业生态建设。

从产业发展现状来看,目前Chiplet异构集成在Die to Die互联标准、先进封装和材料等方面都没有形成统一的行业标准。比如在Die to Die互联标准方面,目前UCIe、BoW、AIB、XSR、CCITA等标准都有行业巨头在推动,企业在打造Chiplet异构集成系统时需要尽可能多地考虑这些标准,以提升功能Die的普适性。

当然,也有机构在推动Chiplet异构集成在Die to Die互联标准上的统一,那就是UCIe产业联盟。UCIe的全称是Unified Chiplet Interconnect Express,定义了提供高带宽、低延迟、高效率、低成本的Die间互联的协议,用于CPU/CPU之间,CPU/Accellerator之间以及CPU和IO Die之间的互联。

UCIe产业联盟由英特尔牵头,联合了台积电、三星、日月光(ASE)、AMD、Arm、高通、谷歌、Meta(Facebook)、微软等行业巨头,目前共有超过120多家公司加入。在elexcon2024深圳国际电子展“系统级封装SiP”论坛上,阿里云智能集团首席云服务器架构师和研发总监、CXL和UCIe董事会成员陈健为大家详细介绍了UCIe协议的迭代以及UCIe 2.0里面的重要更新。

阿里云智能集团首席云服务器架构师和研发总监、CXL和UCIe董事会成员 陈健

陈健称,UCIe主要注重四大关键维度的演进,分别是:

·带宽密度

减少IO对硅片面积的影响,满足AI对高算力密度的需求。

·灵活性

高效支持自定义协议。

·可靠性

确保SiP的使用寿命。

·可测性

满足单硅片和多硅片的测试要求。

这些特性在UCIe 2.0规范更新中都得到了体现。今年8月初,UCIe产业联盟正式推出了UCIe 2.0规范,增加了对可管理性标准化系统架构的支持,并从整体上解决了SiP生命周期中从排序到现场管理的多个小芯片的可测试性、可管理性和调试(DFx)的设计挑战。引入可选的可管理性特性和UCIe DFx架构(UDA),其中包括每个芯片内用于测试、遥测和调试功能的管理结构,实现了与供应商无关的芯片互操作性,为SiP管理和DFx操作提供了灵活统一的方法。

同时,UCIe 2.0规范不仅显著提高了带宽密度和能效,还全面兼容了前代版本UCIe 1.1和UCIe 1.0,为行业用户提供了更加灵活和强大的解决方案。

先进封装和Chiplet异构集成相辅相成

在打造高算力芯片的过程中,Chiplet异构集成和先进封装技术属于是相互配合、相互促进。Chiplet异构集成是以小芯片的方式满足人工智能、网络、自动驾驶、高端PC 和高端游戏等领域的高算力需求,要将这些小芯片融合在一起,就离不开先进封装技术。因而,先进封装正在成为将多个Die集成到单个封装中的关键解决方案。

同时,Chiplet异构集成也在影响先进封装技术的发展,比如基板封装(Substrate packaging)、硅中介层封装(Silicon-interposer packaging)是应用于Chiplet异构集成的重要封装技术。目前,产业界正在积极探索玻璃基板和玻璃中介层。如果是将硅中介层换成玻璃中介层,就可以将芯片集成到大型封装中,同时提供更好的平整度,这对于HPC和AI应用程序至关重要。

当然,目前晶圆代工厂和封测厂商对于先进封装的理解会有区别,因此提供的先进封装方案也会有差异。市场主流当属台积电,目前该公司IC先进封装主要有TSMC-SoIC、InFO、CoWoS等,其中InFO是一种先进的扇出型晶圆级封装(FOWLP)技术,直接在芯片的外围形成更多的I/O连接点,技术拓展包括InFO-PoP、InFO-oS、InFO-LSI等;CoWoS是一种先进的2.5D封装技术,将多个不同功能的芯片首先封装到中介层上,然后将该结构封装在基板上,技术拓展包括CoWoS-S、CoWoS-R、CoWoS-L;TSMC-SoIC是3D IC封装方案,采用了无凸点的直接键合技术,主要包括CoW(Chip-on-Wafer)和WoW(Wafer-on-Wafer)两种形式。

在elexcon2024深圳国际电子展“系统级封装SiP”论坛上,日月光半导体制造股份有限公司资深副总陈光雄在《异质整合的创新与发展》主题报告中也介绍了日月光公司的先进封装方案。

日月光半导体制造股份有限公司资深副总陈光雄

陈光雄首先谈到了日月光的VIPack平台先进封装技术。VIPack由六大核心封装技术支柱组成,透过全面性整合的生态系统协同合作,包括基于高密度RDL的FOPoP、FOCoS、FOCoS-Bridge、FOSiP,以及基于硅穿孔(TSV)的2.5D/3D IC和Co-Packaged Optics。

其次,陈光雄介绍了日月光的SiPack平台,属于SiP 2.0平台,主要优化了尺寸、整合度、成本、开发周期、电性能和可靠性。具体表现为:

·减小尺寸,减少布局和组件数量,简化最终用途设计;

·减少封装、测试和包装成本;

·实现更灵活的模块化设计;

·降低系统总成本;

·带来更好的系统可靠性;

·增强环境和系统内的EMI屏蔽。

陈光雄举例称,借助日月光的SiPack平台,客户可以将原来55*112mm的PCB方案,缩小成一个18*18mm的先进封装方案,方案面积显著缩小,系统功率密度显著提升。

结语

根据Yole的统计数据,2023年全球先进封装市场规模约为439亿美元左右,同比增长19.62%。同时,预测数据显示,2024年全球先进封装市场份额将在整个封装市场中达到49%,预计将在2025年正式超越传统封装。

先进封装和Chiplet异构集成是打造高算力芯片的关键手段。当然,目前还处于产业初期,主要围绕晶圆代工巨头和封装巨头展开,未来将辐射到整个IC行业,进一步释放这个组合的潜力。在博闻创意会展(深圳)有限公司主办的elexcon2024深圳国际电子展上,我们也清晰地看到,厂商在寻求统一,这样技术的前景才会更好。

-

摩尔定律

+关注

关注

4文章

640浏览量

80621 -

AI芯片

+关注

关注

17文章

2066浏览量

36570 -

chiplet

+关注

关注

6文章

482浏览量

13505 -

UCIe

+关注

关注

0文章

52浏览量

1993 -

先进封装

+关注

关注

2文章

520浏览量

972

发布评论请先 登录

Chiplet封装设计中的信号与电源完整性挑战

摩尔线程副总裁王华:AI工厂全栈技术重构算力基建,开启国产 GPU 黄金时代

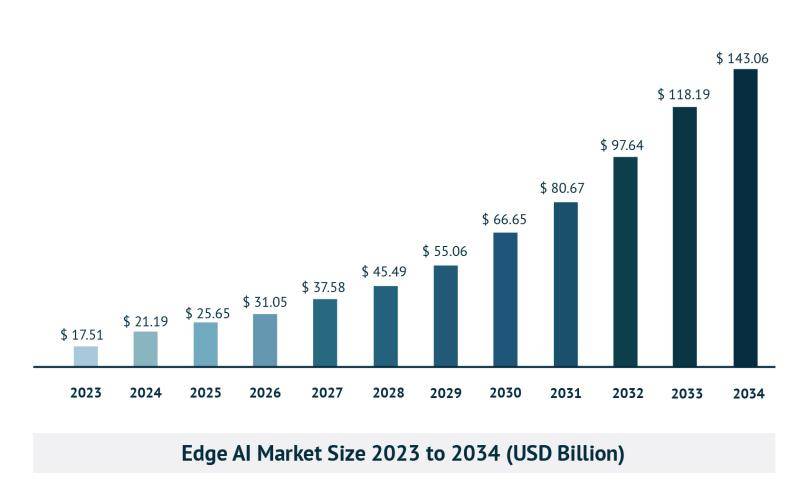

端侧AI百家争鸣,破局之道在何方?

高算力AI芯片主张“超越摩尔”,Chiplet与先进封装技术迎百家争鸣时代

高算力AI芯片主张“超越摩尔”,Chiplet与先进封装技术迎百家争鸣时代

评论