AMD或向UCIe靠拢?

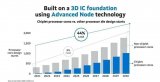

尽管AMD早在几年前便率先探索Chiplet(小芯片)设计的可能性,其中包括自行开发的Infinity Fabric高速互联技术。然而今时今日,他们正考虑采纳共享于英特尔等十家顶级科技公司的通用Chiplet的高速互联标准——UCIe。

眼下,众多的EPYC、Ryzen以及Instinct MI300系列芯片均依赖自研的Infinity Fabric技术完成小芯片间的连接,不过这一技术仍未避免延迟及能量效率不足的缺陷。此外,由于这是AMD独有的专利技术,其他第三方无法获准运用,因此在与其他厂商的小芯片互联过程中势必面临兼容性挑战。

对比之下,英特尔发起的通用Chiplet的高速互联标准——UCIe,它致力于确立一套开源且易互操作的标准。通过先进封装技术,多个来自不同供应商的小芯片可聚集一处,并得以实现高效的互联互通。

AMD阐释,UCIe不仅可以充当小芯片生态系统和数据库,同时也是第三方实施模块化Chiplet设计的契机;用户只须自产核心的小芯片,其余模块则可选配采用UCIe标准化的外来产品,如此可以有无限可能的组合,从而加速产品上市速度。然而想要实现这一境界的关键在于必须有均匀的互连标准以及成熟的设计平台支持。

尽管AMD积极参与UCIe标准联盟的行动,并有高管表达出对采用UCIe标准构建小芯片的兴趣所在,但最终是否将推出相应产品尚需进一步观望。

-

amd

+关注

关注

25文章

5707浏览量

140397 -

chiplet

+关注

关注

6文章

499浏览量

13645 -

UCIe

+关注

关注

0文章

53浏览量

2033

发布评论请先 登录

多Chiplet异构集成的先进互连技术

Robotec.ai与AMD Silo AI的合作实践

西门子EDA如何推动Chiplet技术商业化落地

跃昉科技受邀出席第四届HiPi Chiplet论坛

得一微电子受邀出席第四届HiPi Chiplet论坛

UCIe协议代际跃迁驱动开放芯粒生态构建

解构Chiplet,区分炒作与现实

Chiplet与先进封装全生态首秀即将登场!汇聚产业链核心力量共探生态协同新路径!

Cadence基于台积电N4工艺交付16GT/s UCIe Gen1 IP

新思科技UCIe IP解决方案实现片上网络互连

重磅!AMD将恢复向中国出口MI308芯片!

线控转向直流无刷电机的控制策略研究

技术资讯 I 完整的 UCIe 信号完整性分析流程和异构集成合规性检查

AMD将转向UCIe构建Chiplet

AMD将转向UCIe构建Chiplet

评论