3D 异质集成 (3DHI) 技术可将不同类型、垂直堆叠的半导体芯片或芯粒 (chiplet) 集成在一起,打造高性能系统。因此,处理器、内存和射频等不同功能可以集成到单个芯片或封装上,从而提高性能和效率。随着 3DHI 系统越来越复杂,UCIe (Universal Chiplet Interconnect Express) 标准变得非常重要,对于未来的先进封装和半导体系统设计而言极为关键。由于这些技术的专业性,以及呈指数级增长的计算需求,设计周期变慢,产品的上市时间线也被拉长。

Cadence 专门为简化设计流程而开发的解决方案可提供 UCIe 全方位信号完整性分析和异构集成的合规性检查。本文详细介绍了该分析解决方案和设计架构,并分享了来自 Cadence 及其客户的各种测试案例,这些客户在不断推动该行业标准的发展,也使得现有的分析能力面临挑战。

异构集成

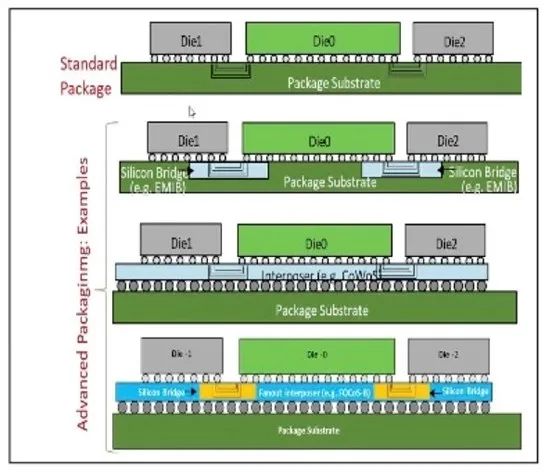

许多行业领导者目前都在进入异构集成领域,努力开拓新的机遇。下图显示了标准和先进封装的 2D 和 3D 应用场景。

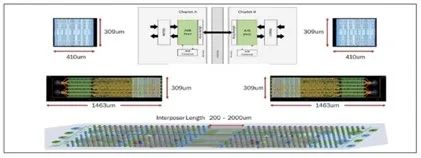

Chiplet(小芯粒)得到大规模使用的一个先决条件是出现 UCIe 等互连标准,以及拥有强大工具和设计流程,用于专门解决 chiplet 面临的问题。本文讨论了一种硅基板的异构集成,针对使用 UCIe 接口的 960Gbps 数据传输进行了优化。设计和验证 chiplet上的输入/输出(I/O)和 µbump 阵列时遵循了标准集成电路开发流程,而 chiplet 在硅基板上的集成则需要一个新的设计流程,以完整模拟中介层造成的信号失真。下图展示了 UCIe 接口的关键元件。

完整的信号完整性流程

信号和电源完整性 (SI/PI) 的完整的仿真和分析是系统设计不可或缺的一部分(见下图)。

Cadence Sigrity Signal and Power Integrity 和 Clarity 3D Solver 多物理场系统分析 (MSA) 软件可用于对设计进行全面仿真。Sigrity X SystemSI UCIe 合规工具包和晶体管到行为 (T2B) 模型转换功能可提供 UCIe 全方位信号完整性分析,并对异构集成进行合规性检查。Sigrity X SystemSI 用于瞬态(时域)分析和自动 UCIe 合规工具包检查。Clarity 3D Layout 用于对布设在中介层上的 UCIe 接口进行全波 3D 有限元法 (FEM) S 参数提取。

结论

本文介绍了一个利用 Cadence Sigrity X Platform/Clarity 3D Solver、Allegro X Platform 和 Virtuoso 平台实现的详细解决方案,其中包含一个完整的流程,包括对一个 8 层硅基板进行全 3D 提取,该硅基板已针对使用 UCIe 接口的 960Gbps 数据传输进行优化。该流程提供了 UCIe 完整的信号完整性分析,并对异构集成进行了合规性检查,还可以详细模拟 interposer 上的传输线效应。

-

芯片

+关注

关注

463文章

54411浏览量

469151 -

信号完整性

+关注

关注

68文章

1497浏览量

98237

发布评论请先 登录

技术资讯 I 完整的 UCIe 信号完整性分析流程和异构集成合规性检查

技术资讯 I 完整的 UCIe 信号完整性分析流程和异构集成合规性检查

评论