近年来,江波龙开启重投入模式,在企业级存储研发领域持续加大力度,打造eSSD+RDIMM产品应用组合和数据中心存储制造专线,目前已突破了多个领域的行业标杆客户,实现大规模量产和交付。

随着AI的快速发展,计算密集型工作负载对存储的低延迟、高带宽提出了前所未有的高要求。Compute Express Link(CXL)互连技术为数据中心的性能和效率提升开辟了新的途径。在前沿技术趋势的推动下,江波龙在本次CFMS2024率先发布并现场演示了其首款采用自研架构设计的FORESEE CXL 2.0内存拓展模块,支持内存池化共享,为企业级应用场景带来全新突破。该产品通过独特堆叠技术,能够基于16Gb SDP颗粒实现128GB大容量,相比业界同期水平实现成本大幅度下降的优势。

FORESEE CXL 2.0内存拓展模块基于 DDR5 DRAM开发,支持PCIe 5.0×8接口,理论带宽高达32GB/s,可与支持CXL规范及E3.S接口的背板和服务器主板实现无缝连接,并减少高昂的内存成本和闲置的内存资源,大幅提高内存利用率,从而有效拓展服务器的内存容量并提升带宽性能,助力HPC、云计算、AI等应用场景释放潜能。

在容量方面,FORESEE CXL 2.0内存拓展模块可实现多种容量选择,包括64GB、128GB、192GB以及正在研发中的512GB,充分满足了用户在不同计算应用中的存储需求。值得一提的是,与市场上主流的32GB和64GB同类型产品相比,FORESEE CXL 2.0内存拓展模块在容量上展现出了显著的优势。目前,FORESEE CXL 2.0内存拓展模块与LPCAMM2产品均已做好全面量产的准备,将有序投入生产制造,以满足市场需求。

-

内存

+关注

关注

9文章

3173浏览量

76112 -

拓展模块

+关注

关注

0文章

4浏览量

5769 -

FORESEE

+关注

关注

0文章

29浏览量

9542

发布评论请先 登录

紫光国芯荣获2025年度CXL产品技术创新奖

DDR存储拓展教程

蜂鸟E203的浮点指令集拓展(F拓展)

SkyOne® Ultra 2.0 前端模块,用于 FDD/TDD LTE 频段 7、30、38、40、41 skyworksinc

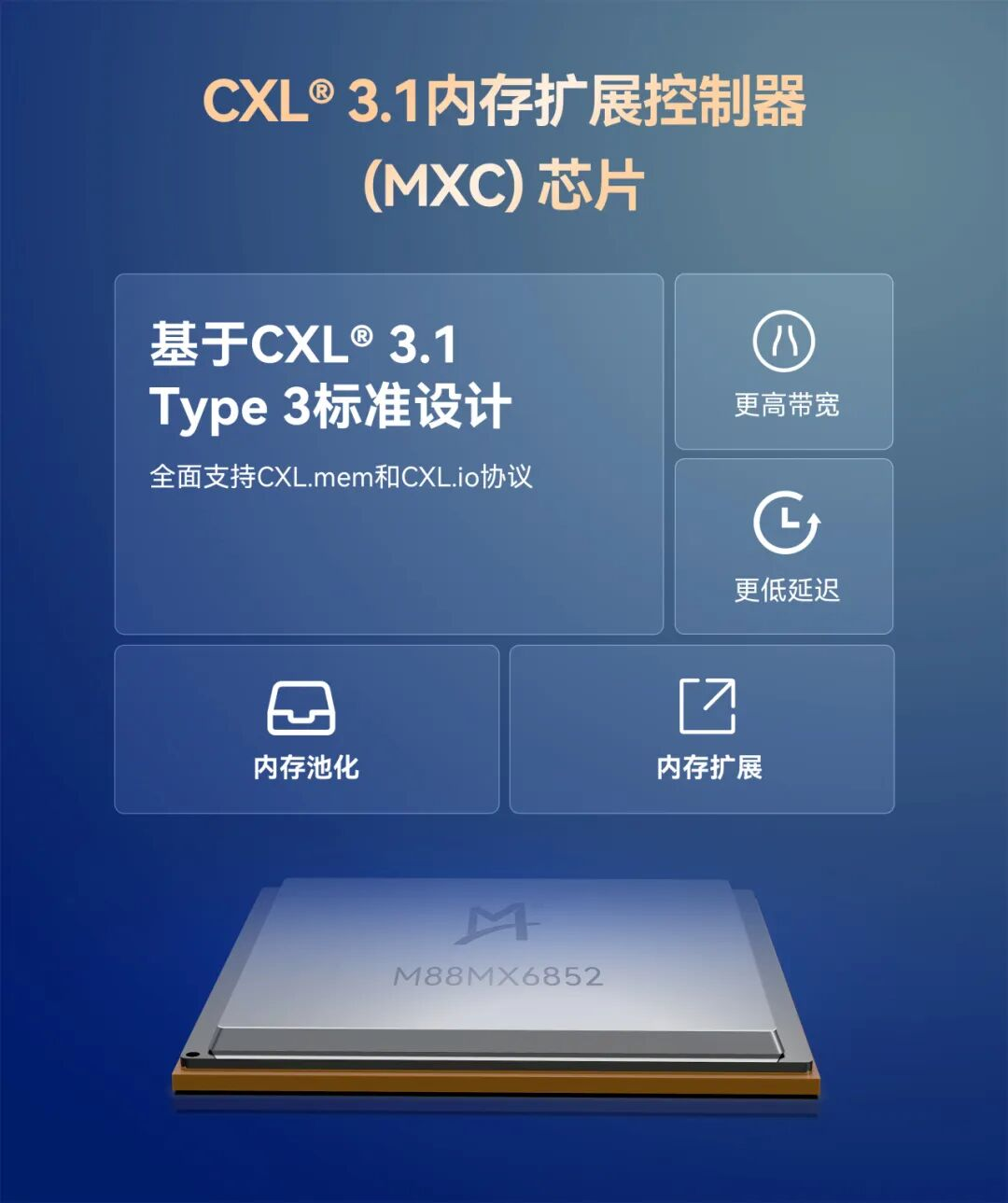

64GT/s+8000MT/s:澜起CXL 3.1芯片破解数据中心内存瓶颈

澜起科技推出CXL® 3.1内存扩展控制器,助力下一代数据中心基础设施性能升级

第二代AMD Versal Premium系列SoC满足各种CXL应用需求

世迈科技最新 128GB E3.S 2T CMM内存模块荣获 CXL 联盟整合商认证

Arm Neoverse CMN S3 推动Compute Express Link (CXL) 存储创新

新思科技解读CXL 3.1标准

FORESEE CXL 2.0内存拓展模块

FORESEE CXL 2.0内存拓展模块

评论