解析DS320PR822:PCIe 5.0和CXL 1.1的高性能线性转接驱动器

在高速数据传输领域,PCIe 5.0、CXL 1.1等接口技术的发展对信号传输的质量和稳定性提出了更高要求。DS320PR822作为一款专为支持这些高速接口而设计的线性转接驱动器,具有诸多卓越特性。本文将深入剖析DS320PR822的特性、应用、电气参数等方面,为电子工程师在实际设计中提供有价值的参考。

文件下载:ds320pr822.pdf

特性亮点

高速接口支持

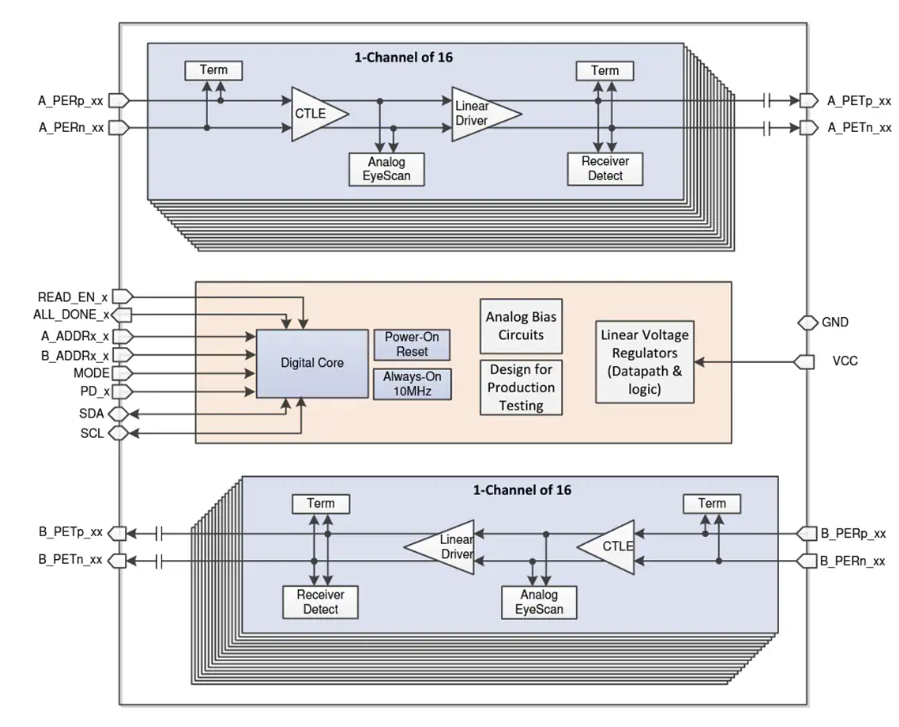

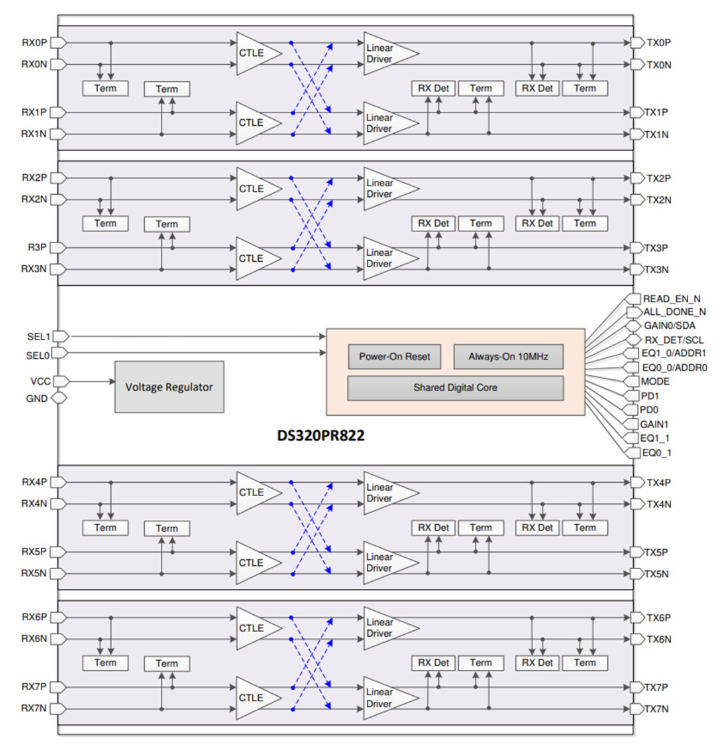

DS320PR822支持PCIe 5.0、CXL 2.0、UPI 2.0等速率高达32 Gbps的接口,同时还支持大多数交流耦合接口,如DP、SAS、SATA、XFI等,展现出了强大的兼容性和通用性。

均衡与低延迟设计

接收器部署了连续时间线性均衡器(CTLE),可提供可编程高频增强功能,打开因互连介质引起的码间串扰而关闭的输入眼图。CTLE在16GHz下可升至22dB,且具有100 ps的超低延迟和PRBS数据的75 fs低附加随机抖动,以及16GHz时 -10dB的极低回波损耗,能有效改善信号质量。

低功耗与抗干扰能力

该器件采用3.3V单电源,内部稳压器具有抗电源噪声能力,每通道有功功率仅160mW,无需散热器。数据路径使用内部稳压电源轨,高度抵抗板上的各种电源噪声,保证了在复杂电磁环境下的稳定工作。

灵活配置方式

提供引脚搭接、SMBus或EEPROM编程三种配置方式,还具备针对PCIe用例的自动接收器检测功能,与协议无关的线性转接驱动器可无缝支持PCIe链接训练,通过一个或多个DS320PR822支持x2、x4、x8、x16、x24总线宽度,满足不同应用场景的需求。

引脚功能解析

DS320PR822共有64个引脚,各引脚功能明确且多样。例如,ALL_DONE_N引脚在SMBus/I2C Primary模式下指示EEPROM寄存器加载操作的完成情况;MODE引脚可设置设备控制配置模式,有5种不同的电平设置可供选择;EQ和ADDR系列引脚在不同模式下分别用于设置接收器线性均衡器(CTLE)的增益和SMBus / I2C的二次地址。这些引脚的合理配置是实现器件各项功能的关键。

电气参数详解

绝对最大额定值

规定了器件在不同参数下的最大承受范围,如电源电压(VCC)在 -0.5V至4.0V之间,超出这些范围可能导致器件永久损坏。

ESD额定值

人体模型(HBM)为±2000V,带电设备模型(CDM)为±500V,表明了器件在静电防护方面的能力。

推荐工作条件

明确了电源电压、电源噪声容限、工作温度等参数的推荐范围,确保器件在正常工作时能够达到最佳性能。

直流和高速电气特性

涵盖了功率消耗、控制IO的电压和电流特性、接收器和发射器的电气参数等多个方面。例如,在不同的EQ和GAIN设置下,器件的平坦增益和EQ增益会有所不同,工程师需要根据实际应用需求进行合理调整。

功能模块与工作模式

线性均衡功能

DS320PR822的接收器采用连续时间线性均衡器(CTLE),通过高频提升和低频衰减来均衡无源通道的频率相关插入损耗。在Pin模式下,EQ引脚可设置不同通道的均衡增益;在SMBus/I2C模式下,各通道可独立编程,实现更精细的控制。

扁平增益控制

GAIN引脚可设置器件的扁平增益,在Pin模式下,不同的电平设置对应不同的增益值;在I²C模式下,每个通道也可独立设置。同时,需要注意输出信号的摆幅应在器件的线性范围内,以保证信号的质量。

接收器检测状态机

该器件部署了Rx检测状态机,可根据不同的引脚设置确定是否存在有效的PCI Express终端。在PCIe应用中,PD0/1引脚可与PCIe侧带信号连接,实现所需的RX检测功能。

交叉点功能

提供四个2x2交叉点多路复用器功能,通过SEL引脚可选择信号路径为直连或交叉连接,在所有设备控制模式下均有效。

工作模式

- Active PCIe Mode:PCIe状态机启用,PD0和PD1引脚驱动为低,用于重驱动和均衡PCIe信号,提高信号完整性。

- Active Buffer Mode:PCIe状态机禁用,适用于非PCIe应用,作为缓冲器提供线性均衡。

- Standby Mode:PD1和PD0引脚为高,器件进入待机模式,节省功耗。

编程与配置

引脚模式

通过2级和5级引脚对器件进行控制和信号完整性优化设置。其中,8个5级输入引脚使用电阻分压器设置有效电平,外部电阻需具有10%或更好的公差。

SMBUS/I2C寄存器控制接口

当MODE = L2时,通过标准I2C或SMBus接口进行配置,接口速率可达400 kHz。DS320PR822有共享寄存器和通道寄存器两种类型,分别用于设备级配置和各通道的独立配置。

SMBus/I2C Primary模式配置

将MODE引脚设置为L1,器件可从EEPROM读取配置信息。EEPROM加载操作在设备首次上电后仅进行一次,完成后ALL_DONE_N引脚将变为低电平。

应用与设计要点

典型应用场景

DS320PR822可用于机架式服务器、微服务器、塔式服务器、高性能计算、硬件加速器、网络连接存储、存储区域网络(SAN)和主机总线适配器(HBA)卡、网络接口卡(NIC)、台式计算机或主板等多种领域,还可用于实现PCI Express x2、x4、x8、x16等不同总线宽度的2x2交叉点配置。

UPI x24通道交叉点配置

设计要求

在与PCIe CEM连接器接口时,使用85Ω阻抗的走线,对差分对的P和N走线进行长度匹配;采用均匀的走线宽度和间距;在每个通道段的接收器端附近放置交流耦合电容,推荐使用220nF的电容;对连接器过孔和信号过孔进行背钻,以减少残桩长度;使用参考平面过孔确保低电感的回流路径。

详细设计步骤

将DS320PR822放置在CPU Tx和CPU Rx之间,保证器件输出引脚的信号摆幅在其线性范围内。根据通道损耗调整EQ设置,以优化接收端的眼图。在SMBus/I2C模式下,需使用上拉电阻将SCL和SDA引脚连接到3.3V电源。

应用曲线分析

通过对比有无DS320PR822的PCIe 5.0链路,发现该器件能够将链路的总通道损耗从36dB扩展到58dB,实现约22dB的延伸能力,但实际延伸效果受多种信号完整性因素影响,建议进行信号完整性仿真。

电源与布局建议

电源设计

电源应满足推荐工作条件中的直流电压、交流噪声和启动斜坡时间要求。无需特殊的电源滤波,仅需标准的电源去耦,包括每个VCC引脚的0.1µF电容、每个器件的1.0µF大容量电容和每个电源总线的10µF大容量电容。同时,电压调节器输出引脚需在附近使用0.1µF的去耦电容。

布局设计

- 去耦电容应尽量靠近VCC引脚,若电路板设计允许,可放置在器件正下方。

- 高速差分信号应紧密耦合、偏斜匹配并进行阻抗控制,尽量避免使用过孔,若必须使用,需采取措施减少过孔残桩。

- 可在高速差分信号焊盘下方使用GND relief来改善信号完整性,同时在器件正下方放置GND过孔,以提高热导率。

DS320PR822以其高性能、低功耗、灵活配置等特点,为高速数据传输应用提供了优秀的解决方案。电子工程师在设计过程中,需充分理解其特性、电气参数、功能模块和应用要点,结合实际需求进行合理的配置和布局,以确保系统的稳定性和可靠性。在实际应用中,你是否遇到过类似高速接口设计的挑战?又是如何解决的呢?欢迎在评论区分享你的经验和见解。

-

高速接口

+关注

关注

1文章

71浏览量

15224

发布评论请先 登录

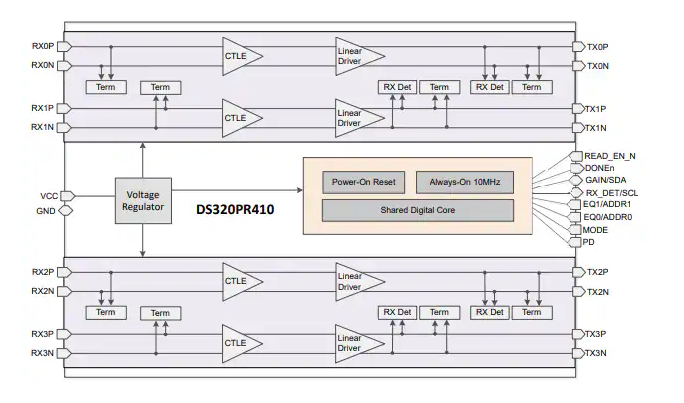

DS320PR410支持PCIe5.0、CXL 2.0的四通道线性转接驱动器数据表

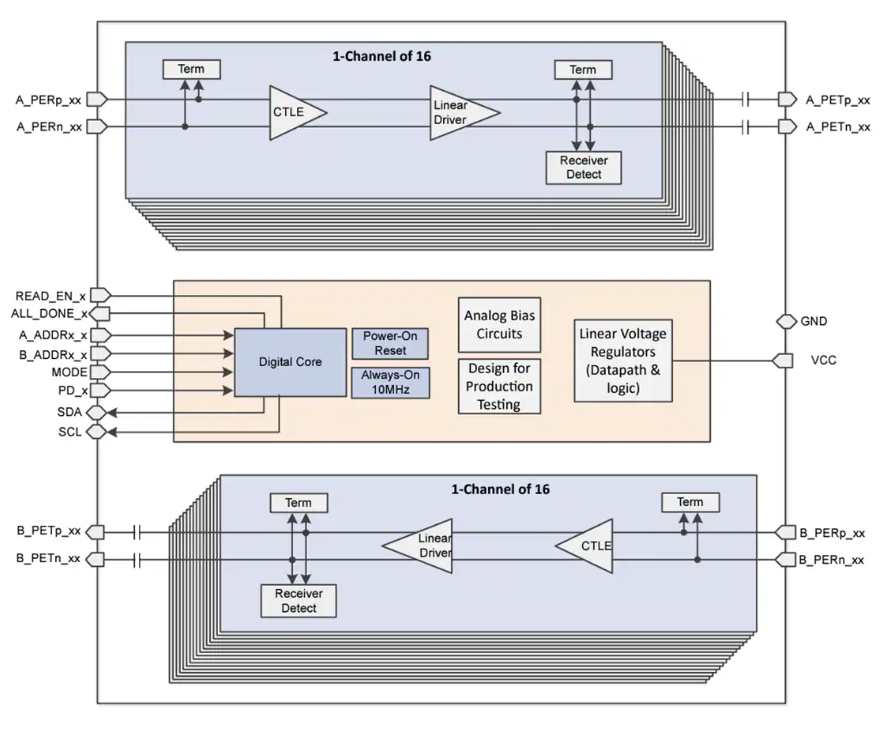

DS320PR1601 32Gbps 16通道PCIe 5.0、CXL 2.0线性转接驱动器数据表

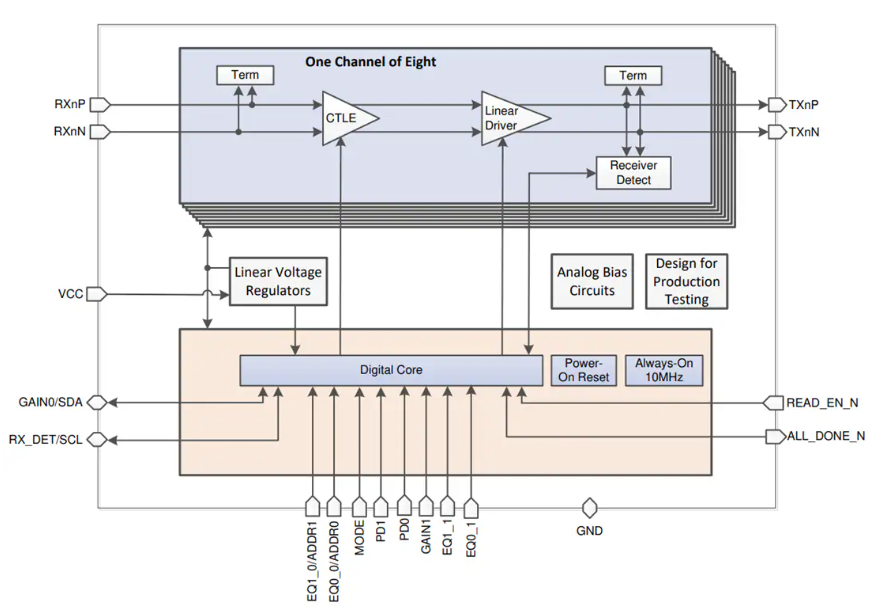

DS160PR822 PCIe 4.0 16Gbps 8通道线性转接驱动器数据表

DS320PR822用于PCle 5.0、CXL 1.1的线性驱动器数据表

DS160PR1601 PCIe 16Gbps线性转接驱动器技术解析与应用指南

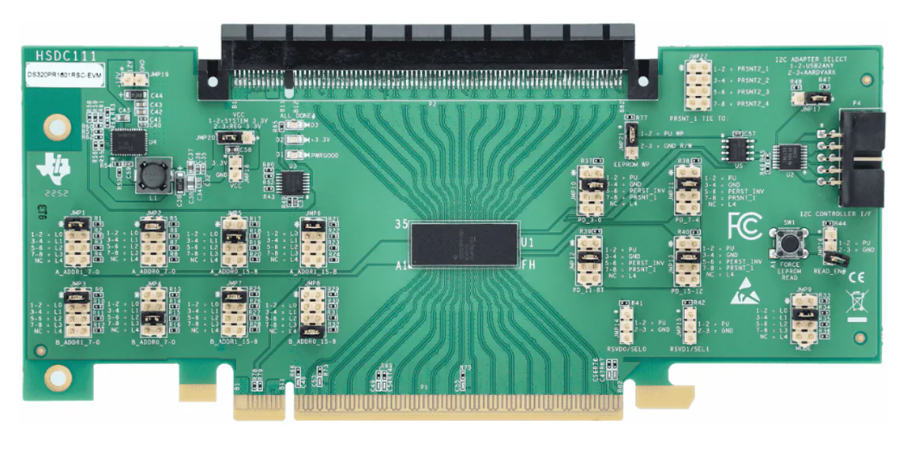

DS320PR1601RSC-EVM线性转接驱动器评估模块技术解析

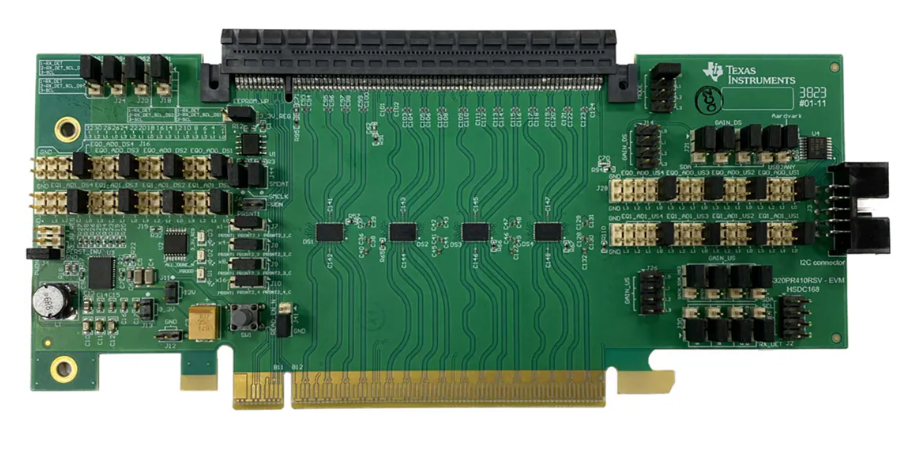

DS320PR410-RSC-EVM PCIe 5.0线性重驱动器评估模块技术解析

解析DS320PR822:PCIe 5.0和CXL 1.1的高性能线性转接驱动器

解析DS320PR822:PCIe 5.0和CXL 1.1的高性能线性转接驱动器

评论