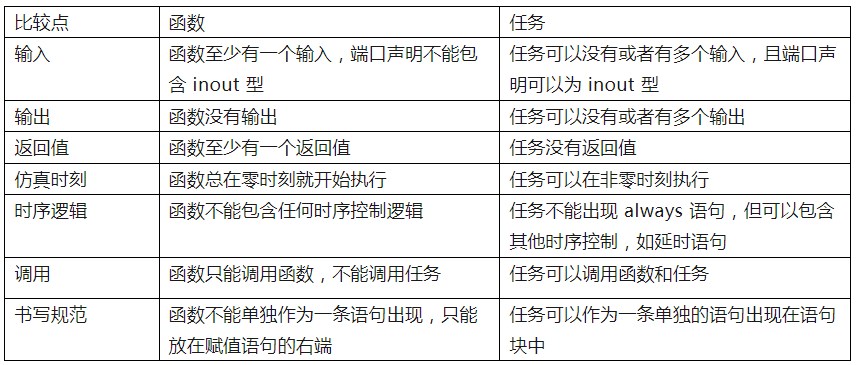

在verilog中,函数和任务均用来描述共同的代码段,并且在模式内任意位置被调用,提高代码效率,让代码更加的直观,提高代码可读性。但是在实际使用的过程中,函数和任务也存在诸多的不同,下面将对而这进行对比,方便学习理解。

| 比较 | 函数 | 任务 |

|---|---|---|

| 输入 | 函数至少需要包含一个输入,端口类型不能包含inout类型 | 任务可以没有或者有多个输入,且端口声明可以为inout类型 |

| 输出 | 函数无输出 | 任务可以没有或者有多个输出 |

| 返回值 | 函数有至少一个返回值 | 任务无返回值 |

| 仿真时间 | 函数从零时刻开始执行 | 任务可以在非零时刻执行 |

| 时序逻辑 | 函数不包含时序逻辑 | 任务不能出现always语句,但是可以使用延时之类的语句 |

| 调用 | 函数可以调用函数但是不能调用任务 | 任务可以调用任务和函数 |

| 语法规范 | 函数只能出现在赋值语句的右端 | 任务可以作为单独的语句出现 |

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Verilog

+关注

关注

31文章

1374浏览量

114726 -

函数

+关注

关注

3文章

4422浏览量

67855 -

任务

+关注

关注

1文章

20浏览量

8725

发布评论请先 登录

相关推荐

热点推荐

verilog模块的调用、任务和函数

在做模块划分时,通常会出现这种情形,某个大的模块中包含了一个或多个功能子模块,verilog是通过模块调用或称为模块实例化的方式来实现这些子模块与高层模块的连接的.

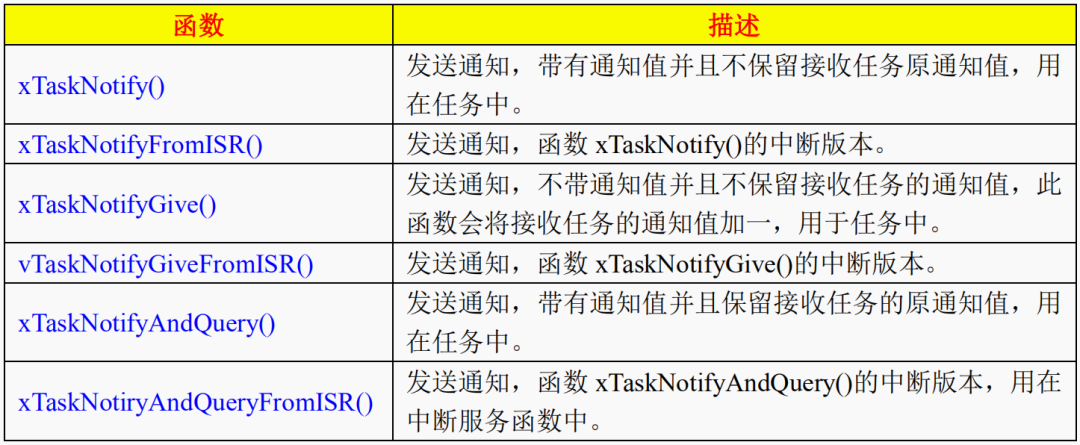

FreeRTOS任务应用函数介绍

* constpulTotalRunTime ); 该函数向TaskStatus_t结构体填充相关信息,系统中每一个任务的信息都可以填充到TaskStatus_t结构体数组中,数组大

Verilog HDL语言中任务与函数的比较

其中,返回值的类型和位宽是可选项,如果缺省会返回一位寄存器类型数据。Verilog HDL认为函数的定义隐式地声明了与函数同名的寄存器。函数的定义把

Verilog数字系统设计——任务和函数二(系统任务readmemb或readmemh)

Verilog数字系统设计十任务和函数实验2文章目录Verilog数字系统设计十前言一、Verilog系统

发表于 12-05 19:06

•7次下载

Verilog数字系统设计——任务和函数一(斐波那契数列)

Verilog数字系统设计九任务和函数实验1文章目录Verilog数字系统设计九前言一、任务和函数

发表于 12-05 19:06

•9次下载

Verilog设计中函数和任务的作用分析

任务和函数在Verilog中用于描述常用的功能行为。与其在不同的地方复制相同的代码,不如根据需求使用函数或任务,这是一种良好且常见的做法。为

Verilog系统函数和边沿检测

“ 本文主要分享了在Verilog设计过程中一些经验与知识点,主要包括Verilog仿真时常用的系统任务、双向端口的使用(inout)、边沿检测”

FreeRTOS中其他任务API函数

1、函数 uxTaskPriorityGet() 此函数用来获取指定任务的优先级,要使用此函数的话宏 INCLUDE_uxTaskPriorityGet 应 该定义为 1。 2、

verilog function函数的用法

Verilog 是一种硬件描述语言 (HDL),主要用于描述数字电子电路的行为和结构。在 Verilog 中,函数 (Function) 是一种用于执行特定

verilog中函数和任务对比

verilog中函数和任务对比

评论