Verilog提供了很多对文件操作的系统任务和函数,例如打开关闭文件、向文件写入值、从文件读出值等等。

当我们使用这些文件操作时,需要注意文件属性和变量内容,选择正确的系统任务,提供相关参数,以避免一些不必要的错误。这里主要介绍关于文件打开/关闭、文件写入和文件读出相关的操作。

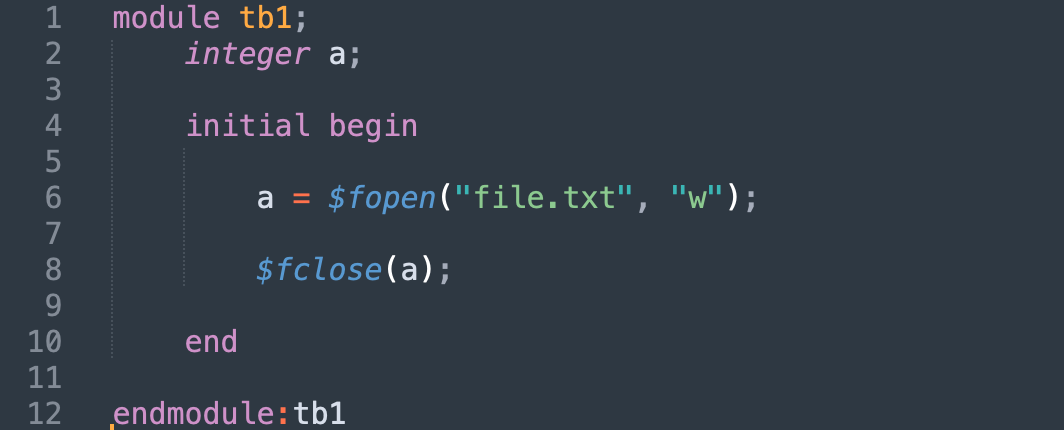

文件打开/关闭

| 文件打开 | a=$fopen("file.txt","w") | 打开file.txt文件,a为返回32bit文件描述符 |

| 文件关闭 | $fclose(a) | 关闭a描述的对应文件 |

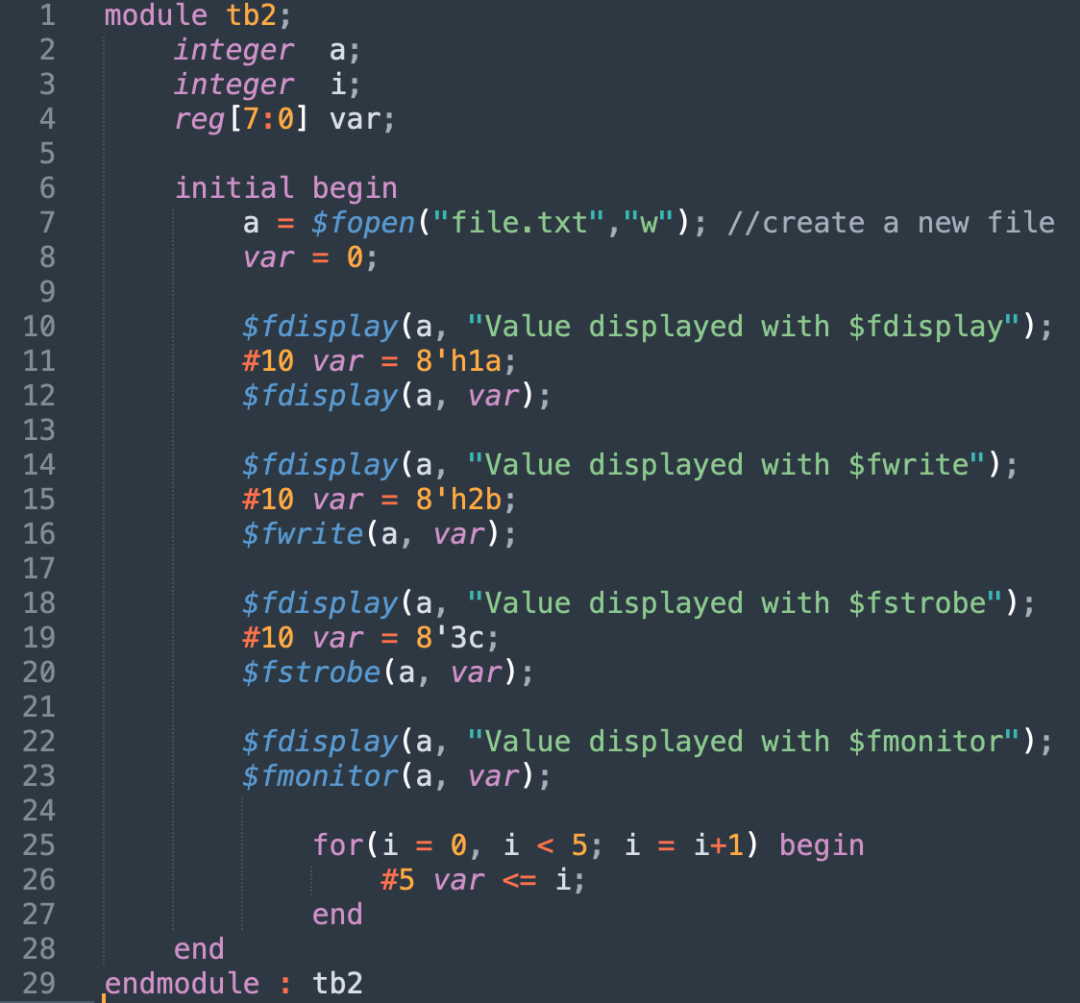

文件写入

| $fdisplay | 按顺序或条件写,自动换行 |

| $fwrite | 按顺序或条件写,不自动换行 |

| $fstrobe | 语句执行完毕后选通写文件 |

| $fmonitor | 只要有数据变换就写文件 |

文件读出

| $fgetc | 按字符读文件 |

| $fgets | 按行读文件 |

| $fscanf | 按格式读文件 |

| $fread | 按二进制读文件 |

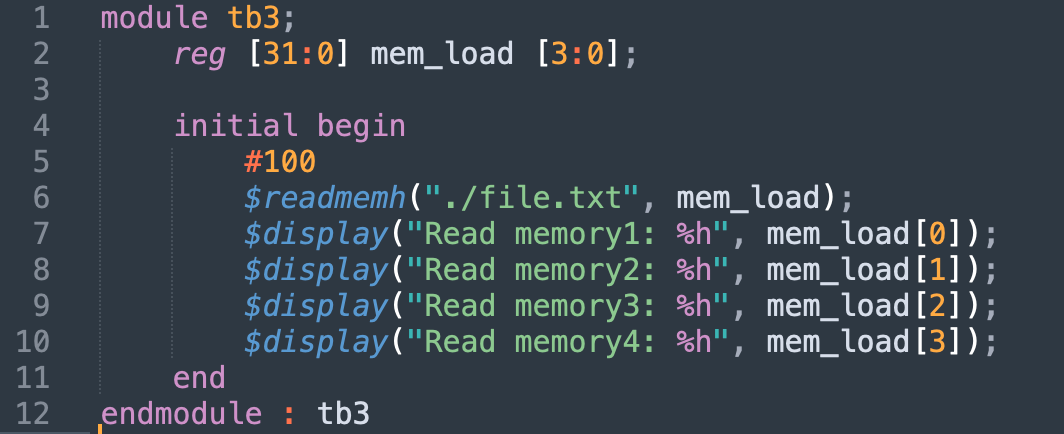

除此之外,还有两个常用的系统任务$readmemb和$readmemh,用于从文件中读取数据到存储器中。读取的内容只包括:空白位置(空格、换行、制表格(tab和form-feeds),注释行、二进制或十六进制的数字。

假设file.txt文件中的数据为

12345678

5a5a5a5a

deadbeef

87654321

本文主要介绍常用的文件操作系统任务,其余没介绍的大家可以按需学习。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Verilog

+关注

关注

31文章

1374浏览量

114736 -

函数

+关注

关注

3文章

4422浏览量

67873 -

文件操作

+关注

关注

0文章

7浏览量

5477

原文标题:Verilog中关于文件操作的系统任务

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

关于verilog中的生成块和任务

本帖最后由 耶稣牛肚 于 2017-1-4 20:27 编辑

自学verilog,看到生成块和任务的时候有一些迷茫,希望大神讲解一下。生成块书上说本质是将多条重复语句化为一条起到简化的作用

发表于 01-04 20:25

可以在硬件(Verilog)中更轻松地完成此任务吗?

数据。我最初的想法是可以使用某种形式的软件(C,C ++)来完成这项任务。我对回读机制的理解是否正确?可以在硬件(Verilog)中更轻松地完成此任务吗?对于那些做过回读的人,你使用了

发表于 05-29 13:55

【资料】RT-Threa操作系统中任务的概念及实现任务所用到的数据结构

的概念,所有任务都在同一个地址空间中,此时系统中唯一的进程就是我们烧录的整个系统可执行文件。通常在类似RT-Thread这类实地址运行的嵌入

发表于 03-23 15:11

如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真

本文将介绍如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真。 Icarus Verilog Icarus V

FPGA中如何使用Verilog处理图像

的完整 Verilog 代码 。 在这个FPGA Verilog项目中,一些简单的处理操作都是在Verilog中实现的,比如反相、亮度控制和

UCOSIII操作系统学习笔记——任务

RTOS系统RTOS全程为:Real Time OS,就是实时操作系统。实时操作系统分为硬实时和软实时。硬实时要求在规定时间内必须完成操作,硬件实时

发表于 12-02 13:51

•2次下载

Verilog数字系统设计——任务和函数二(系统任务readmemb或readmemh)

Verilog数字系统设计十任务和函数实验2文章目录Verilog数字系统设计十前言一、Verilog

发表于 12-05 19:06

•7次下载

Verilog设计中函数和任务的作用分析

任务和函数在Verilog中用于描述常用的功能行为。与其在不同的地方复制相同的代码,不如根据需求使用函数或任务,这是一种良好且常见的做法。为了便于代码维护,最好使用子例程之类的函数或任务

Verilog系统函数和边沿检测

“ 本文主要分享了在Verilog设计过程中一些经验与知识点,主要包括Verilog仿真时常用的系统任务、双向端口的使用(inout)、边沿检测”

verilog中函数和任务对比

在verilog中,函数和任务均用来描述共同的代码段,并且在模式内任意位置被调用,提高代码效率,让代码更加的直观,提高代码可读性。但是在实际使用的过程中,函数和

verilog中for循环是串行执行还是并行执行

在Verilog中,for循环是并行执行的。Verilog是一种硬件描述语言,用于描述和设计数字电路和系统。在硬件系统

Verilog中关于文件操作的系统任务

Verilog中关于文件操作的系统任务

评论