鉴于摩尔定律的效能逐渐减弱,芯片制造商纷纷探索新策略提升处理器性能,如推动架构创新,加大芯片面积,采用多芯乃至晶圆级芯片等方案,如美商Cerebras推出的WSE系列AI芯片。近期,中国科学院计算技术研究所的专家在《基础研究》期刊发布了一篇论文,深入剖析了光刻与小芯片Chiplet的局限性,并提出了一种新的大芯片结构概念,即Zhejiang。此款产品是一经研发的具备256颗核心的多芯计算复合体。

值得关注的是,中国科学院计算技术研究所还打算将这款基于RISC-V架构的大芯片进阶为拥有1600颗核心的巨无霸计算设备。

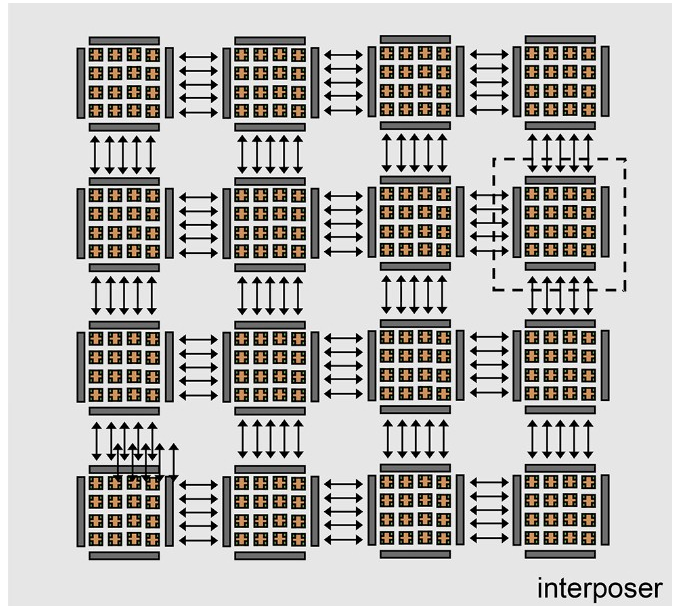

根据目前所探知的信息,Zhejiang是一个由16个小芯片构成,其中每片均包含16个RISC-V内核。研究人员指出,可以在单一独立组件内增加100片这样的小芯片,之前我司将这种设备称为插槽,但现在看来它更像一个系统板。关于这100片小芯片将如何搭配以及各片将支持何种内存结构(因为有1600个内核)仍有待观察。

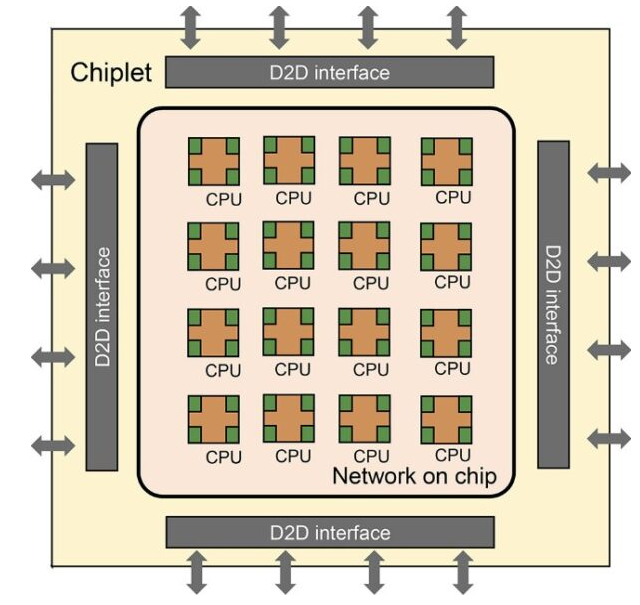

以下是Zhejiang RISC-V小芯片的框图:

以下是如何使用中介层将16个小芯片连接在一起形成具有共享内存的256核计算复合体,从而实现芯片间(D2D)互连:

来自中国科学院的专家自述,Zhejiang将会引入22纳米制程工艺打造。

有关大芯片计算引擎的构造问题,专家预估其零部件数量将高达上兆个,占地达数千平方毫米,采用封装式小芯片或者计算及储存单元的晶圆级整合。针对百亿亿次高性能计算机及人工智能领域,我们相信中国科学院极有可能正考虑采用HBM堆叠式DRAM或其他可行的替代品,例如英特尔和SK海力士共同研发的MCR内存。而因为RISC-V内核对本地SRAM有着庞大需求,因此这或许可以减少对HBM内存的依赖,且可借用MCR双泵浦技术加快DDR5内存运行速度。

-

处理器

+关注

关注

68文章

20339浏览量

255270 -

芯片

+关注

关注

463文章

54463浏览量

469614 -

HBM

+关注

关注

2文章

435浏览量

15887 -

RISC-V

+关注

关注

49文章

2954浏览量

53586

发布评论请先 登录

新思科技ImperasDV解决方案让RISC-V处理器验证效率翻倍

Banana Pi BPI-CM6 计算模块将 8 核 RISC-V 处理器带入 CM4 外形尺寸

突破!深圳诺奖实验室发布量产级RISC-V处理器IP

直播预约 |开源芯片系列讲座第30期:“一生一芯”计划——从零开始设计自己的RISC-V处理器芯片

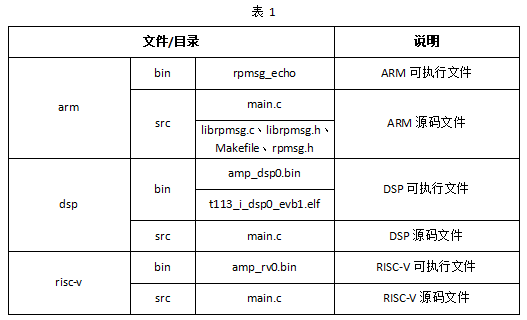

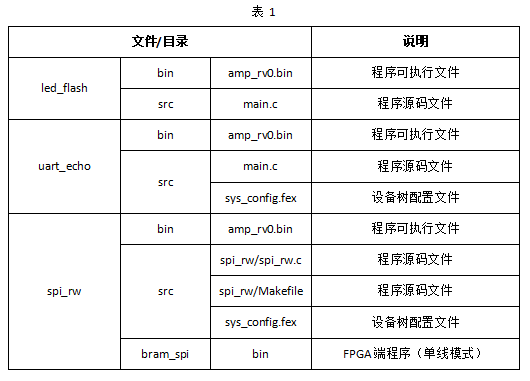

国产!全志T113-i 双核Cortex-A7@1.2GHz 工业开发板—ARM + DSP、RISC-V核间通信开发案例

国产!全志T113-i 双核Cortex-A7@1.2GHz 工业开发板—RISC-V案例开发手册(上)

2025 RISC-V中国峰会 | 匠芯创SoC芯片引领工业应用新潮流

明晚开播 |开源芯片系列讲座第28期:高性能RISC-V微处理器芯片

普华基础软件亮相2025 RISC-V中国峰会

时擎科技亮相2025 RISC-V中国峰会,深度解析高性能RISC-V SoC技术挑战与创新

睿思芯科携灵羽处理器亮相2025 RISC-V中国峰会

包云岗:原位替代 ARM,并未真正发挥 RISC-V 的优势

直播预约 |开源芯片系列讲座第28期:高性能RISC-V微处理器芯片

沁恒微电子:从互连互通应用推动RISC-V落地发展

中国科学家发表“大芯片”论文:国产256核RISC-V处理器

中国科学家发表“大芯片”论文:国产256核RISC-V处理器

评论