由于 RISC-V 是一个开放性的 ISA,它允许任何开发者自由设计和扩展定制处理器。基于 RISC-V 的处理器必须保持与不断增长的支持工具和软件生态系统的兼容性。

RISC-V 处理器验证需求

RISC-V 处理器验证需要一种能够匹配 ISA 可配置和可扩展特性的解决方案,满足以下特定需求:

能够与用户现有的环境协同工作,并且应利用诸如 RISC-V 验证接口 (RVVI) 等开放标准接口,以实现高效和复用。

应支持行业最佳实践,例如约束随机激励和功能覆盖率。

解决方案必须应对处理器特定的挑战,例如验证 DUT(待测单元)在响应异步事件时的行为。

新思科技 ImperasDV 解决方案

新思科技推出的 ImperasDV 是满足所有这些要求的解决方案。

ImperasDV 是一种针对基于 RISC-V 指令集架构(ISA)的定制处理器的前端设计验证解决方案。它包括参考模型、验证组件、功能覆盖率、测试套件以及调试器等核心组件。

ImperasDV 使用 ImperasFPM(快速处理器模型)作为设计验证的参考模型。该模型可以配置基本 ISA 和扩展指令,包括设计者定制的功能,以匹配待测处理器。

ImperasDV 可以用于 SystemVerilog/UVM 测试平台,或任何具有 C 语言接口的平台。它使用 RVVI-TRACE 接口连接到待测处理器,并提供架构状态的持续比较和检查。

ImperasFC 则是一个 RISC-V 指令集的 SystemVerilog 功能覆盖模型,可以为 RISC-V ISA 中的每个扩展提供自动生成的功能覆盖率模型。

ImperasTS 提供针对 RISC-V ISA 的复杂和可配置扩展集的测试套件,用来确保设计和 ISA 之间的兼容性和一致性。

ImperasDV 使用锁步连续比较的设计验证方法,这是一种协同仿真方法,其中 RTL 和参考模型以锁步方式运行。同一个程序在 RTL 和 ImperasFPM 上并行执行,每条指令完成时,比较两者的架构状态,状态不匹配会立即报告为错误。

通过这种全面的设计验证方法,实现高效验证,更快发现错误,立即报告,方便开发者在故障点进行调试。

ImperasDV 技术优势

ImperasDV 拥有显著的技术优势,主要表现在以下几个方面:

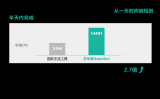

显著缩短处理器设计验证进度,高效的验证方法能显著减少整体验证周期。

支持验证最佳实践,包括功能覆盖率和约束随机测试生成。

实现复杂功能的设计验证,例如中断、调试模式、特权模式、虚拟内存、多核、多发射以及乱序流水线等。

支持定制功能的设计验证,可扩展以验证用户自定义的处理器特性。

采用锁步连续比较方法,RTL 与参考模型协同仿真,指令完成后立即比较架构状态。

验证异步事件的专有同步技术可有效处理异步事件,减少错误来源。

硬件与软件开发共享同一参考模型,提高一致性,支持跨领域验证和开发。

端到端的验证和仿真工具集

新思科技在验证领域一直处于领先地位,为客户提供一系列端到端的验证和仿真工具集。ImperasDV 与新思科技其他验证工具都可以完美结合。与 VCS 一起进行 RISC-V RTL 仿真,功能覆盖率输出会发送到调试和验证管理平台 Verdi。新思科技 VCS 与 ImperasDV 的结合降低了 RTL 风险并加速验证进度。

结语

新思科技汇聚行业顶尖专家,不断革新工具,始终走在最新技术应用的前沿,在 RISC-V 验证领域也持续与合作伙伴保持深厚且值得信赖的关系,为合作伙伴提供卓越的产品和服务。

-

处理器

+关注

关注

68文章

20325浏览量

254693 -

新思科技

+关注

关注

5文章

977浏览量

52985 -

RISC-V

+关注

关注

49文章

2941浏览量

53519

原文标题:精准排错!ImperasDV让RISC-V处理器验证更高效、更精准

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

新思科技邀您共赴2026玄铁RISC-V生态大会

新思科技VC Formal解决方案在RISC-V验证中的应用

新思科技ARC-V处理器驱动RISC-V市场无限机遇

重磅合作!Quintauris 联手 SiFive,加速 RISC-V 在嵌入式与 AI 领域落地

新思科技全栈工具链助力RISC-V设计高效进阶

开芯院采用芯华章高性能数字仿真器GalaxSim,RISC-V 验证获近3倍效率提升

为什么RISC-V是嵌入式应用的最佳选择

基于E203 RISC-V的音频信号处理系统 -协处理器的乘累加过程

明晚开播 |开源芯片系列讲座第28期:高性能RISC-V微处理器芯片

2025新思科技RISC-V科技日活动圆满结束

芯华章RISC-V敏捷验证方案再升级

开芯院采用芯华章P2E硬件验证平台加速RISC-V验证

直播预约 |开源芯片系列讲座第28期:高性能RISC-V微处理器芯片

新思科技ImperasDV解决方案让RISC-V处理器验证效率翻倍

新思科技ImperasDV解决方案让RISC-V处理器验证效率翻倍

评论