PCB层叠设计是什么?又有什么样的作用?

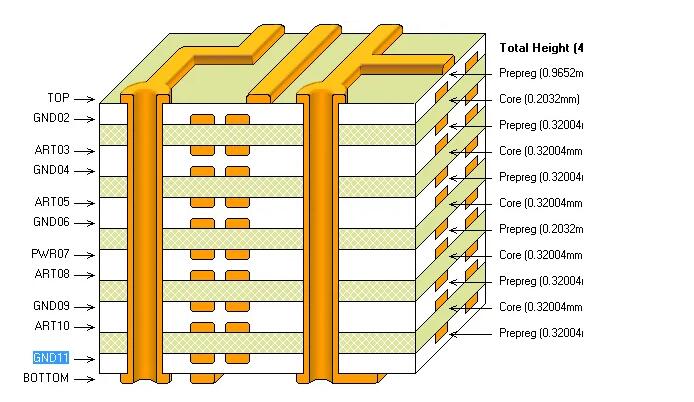

PCB层叠设计又称为PCB层压设计,是指在印刷电路板的设计过程中,通过合理地选择不同层之间的层间结构和层间材料,以及设计每层的布线、焊盘和电源分布等布局,来达到优化电路性能、降低电磁干扰、提高信号完整性和实现电路功能要求的一种设计方法。

作为PCB设计的重要环节,PCB层叠设计对于电路性能和可靠性具有重要影响。下面将详细介绍PCB层叠设计的作用及相关技术细节。

首先,PCB层叠设计的主要目标是优化电路性能。通过合理选择层间结构和层间材料,可以有效减小信号传输的损耗,提高信号完整性和稳定性,降低信号失真和串扰的风险。这对于高速数字信号、高频模拟信号的传输非常重要。层叠设计还可以改善信号的传播速度和电流分布,提高电路的工作频率和响应时间。另外,合理的电源规划和分布可以提供稳定的电源供应,减小电源噪声对电路的影响。

其次,PCB层叠设计对于减少电磁干扰非常关键。在复杂的电子产品中,各个电路模块之间存在电磁干扰的风险。通过使用合适的层间隔离和屏蔽措施,可以减少信号之间的相互干扰,增强信号的抗干扰能力。同时,PCB层叠设计还可以提高PCB的抗辐射能力,减小外部干扰对电路的影响。

此外,PCB层叠设计还可以提高电路的可靠性和稳定性。通过合理分布电源和地线,可以降低电源纹波和噪声,提高电路对温度变化和电源波动的抗干扰能力。层叠设计还能够提高PCB的机械强度和抗振能力,减少机械振动对电路的影响。另外,PCB层叠还能够提供通过内层引线进行信号连接的方式,减少了外部布线的数量,提高了PCB的可靠性和免疫能力。

在具体实施PCB层叠设计时,需要考虑多个因素。首先,需要根据电路的功能和性能要求确定所需的层数。通常,复杂的电路需要更多的层数来实现功能的需求。其次,需要在设计过程中合理选择层间隔离和屏蔽材料。不同的层间材料具有不同的介电常数和损耗因子,需要根据电路信号特性进行选择。同时,也需要考虑材料的成本和供应情况。在布线和引脚分配方面,需要根据信号的敏感度和噪声容忍度,进行合理的布局和分配。此外,还需要把握好层间引线和层间连接的设计,以确保信号的质量和传输效果。

综上所述,PCB层叠设计是优化电路性能、降低电磁干扰、提高信号完整性和实现电路功能要求的重要手段。通过合理选择层间结构和材料、设计布线和引脚分配,可以提高电路的性能和可靠性,降低电磁干扰的风险,从而实现电子产品的高质量设计。在实际工程中,需要根据具体的应用需求和电路特性,综合考虑各个方面的因素,并结合设计规范和经验进行层叠设计,以取得最佳的效果。

-

PCB设计

+关注

关注

396文章

4939浏览量

95786 -

电磁干扰

+关注

关注

36文章

2505浏览量

108084 -

PCB层叠

+关注

关注

0文章

5浏览量

1423

发布评论请先 登录

PCB电路板不涂三防漆有什么影响?会怎么样?

当前VisionFive开发板上的JH7100 SoC对于NVDLA软件站适配的情况是什么样的?

如何设置HDI PCB布局?

【「Altium Designer 25 电路设计精进实践」阅读体验】+第六章节 PCB设计

基于SiC MOSFET和低寄生电感 PCB 层叠母排的 50kHz变频器设计

PCB:无线产品稳定运行的“骨架”

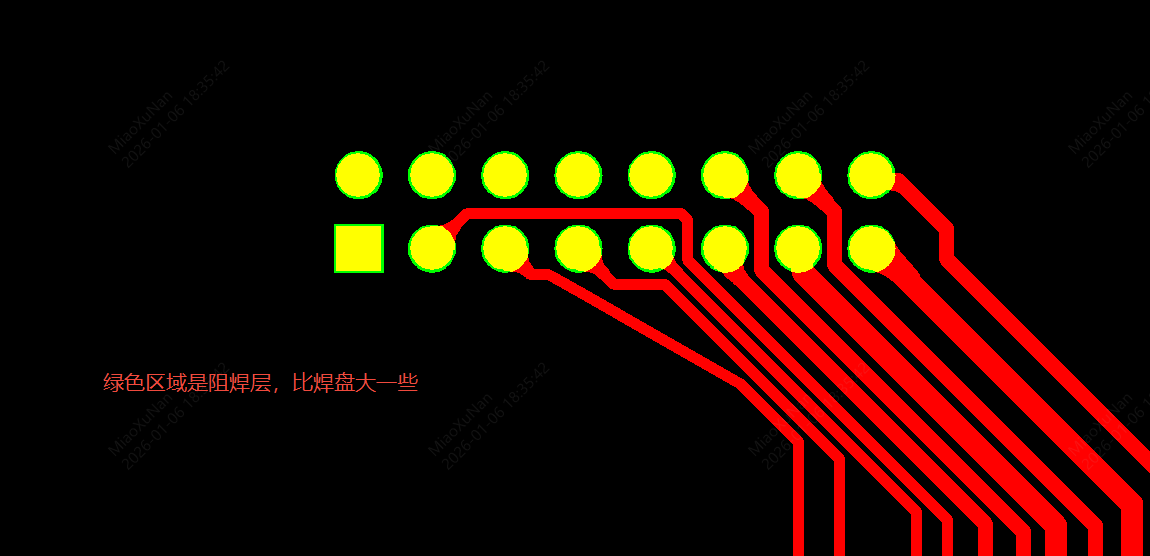

PCB阻焊层与助焊层的本质区别

UWB 蓝牙6.0 WIFI的功耗大概什么样的

SCADA数据采集站应该配什么样的UPS电源?选错可能让数据全丢!

如何优化层叠结构以提高PCB线路板整体性能简述

PCB层叠结构设计的先决条件

高层数层叠结构PCB的布线策略

PCB层叠设计是什么?又有什么样的作用?

PCB层叠设计是什么?又有什么样的作用?

评论