作者:Paul McLellan,来源:Cadence楷登PCB及封装资源中心

莎士比亚在《罗欧与朱丽叶》中写道:“名字有何重要?玫瑰不叫玫瑰,依旧芳香如故。”

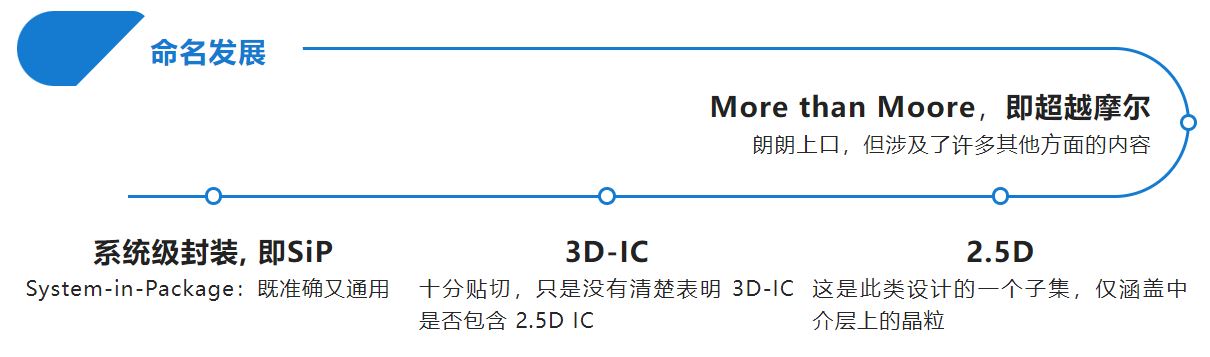

然而在过去 10 年中,尤其是过去 5 年左右,每当我们将不止一个晶粒置于一个封装内时,我们就想为其增加一个新的命名:

……此外还有很多不同的专用名词,显然不适合用作整个行业的通用名称。

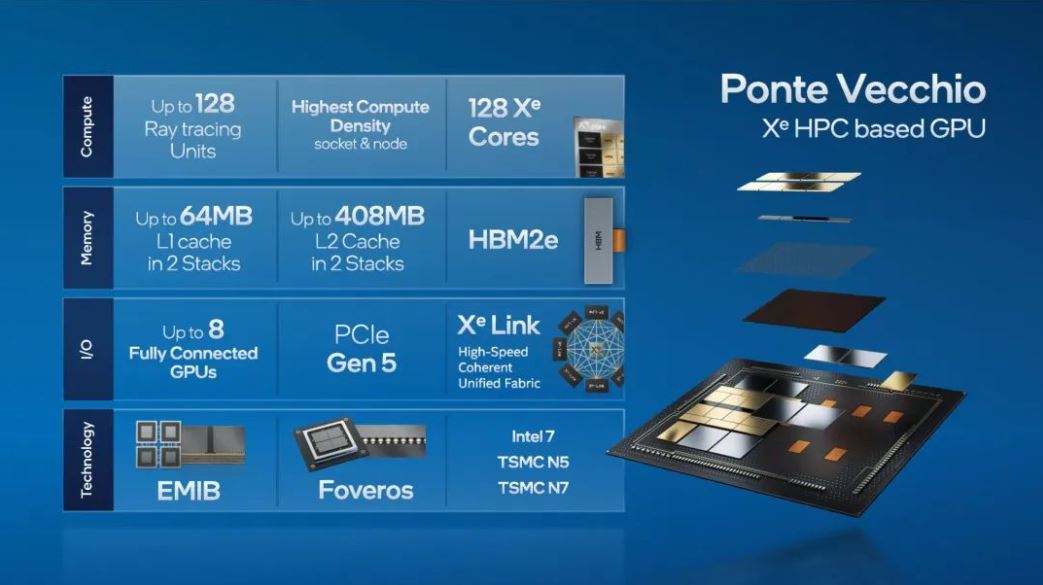

最新出现的一个名称是“异构集成(heterogeneous integration)”或“3D 异构集成(3D heterogeneous integration)”,目前的关注度越来越高。这个词涵盖的内容非常丰富,从向处理器添加"高带宽存储器 (HBM) "堆栈,到 Intel的 Ponte Vecchio 产品(复杂性方面的登峰造极者)——

在 5 个不同的制程节点上装进了超过 47 块小芯片(chiplets),晶体管总数量超过 1000 亿!

这是当之无愧的异构集成!

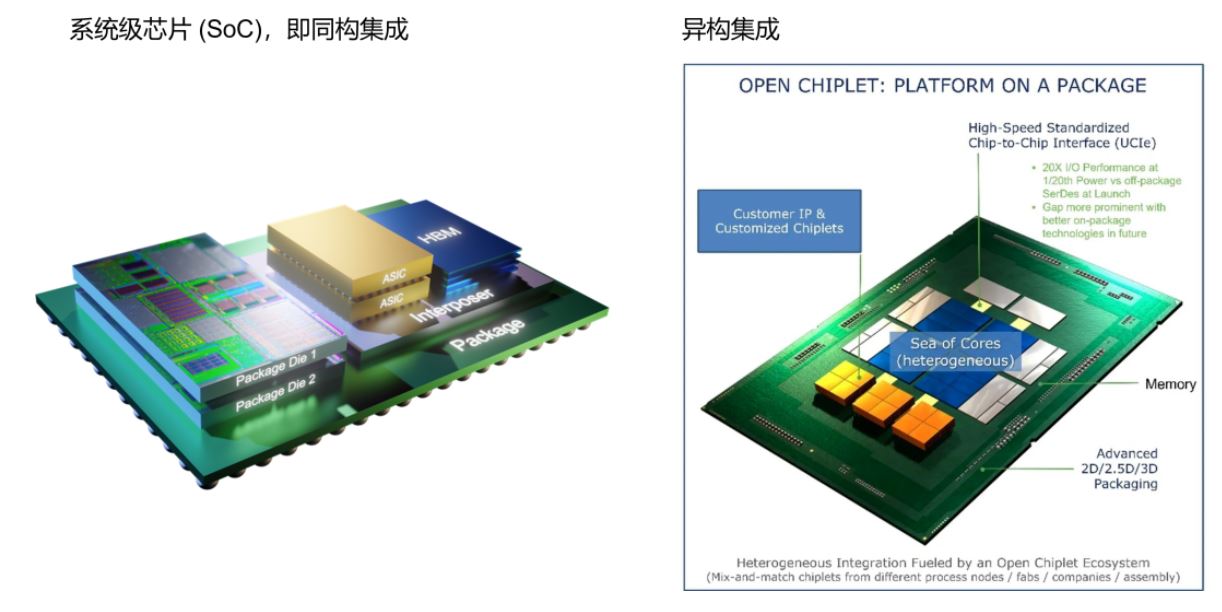

但是,“异构集成”这一词语依然存在一个问题:我们该如何称呼采用这种技术的设计?我认为,“系统级封装”(SiP) 一词就很贴切。所以说,异构集成是用于创建 SiP 的技术。

显然,与异构集成形成鲜明对比的是同构集成,即系统级芯片 (SoC)。同构集成最大的缺点在于,必须在同一个半导体制程节点中完成所有组件。如果需要集成差别较大的模块,例如光子学、射频、模拟、DRAM、MRAM 等等,这项工作就会变得非常棘手。

挑战来自成本方面,而不是技术。例如,我们知道如何将 DRAM 摆放在逻辑晶粒上,但实际上,即使芯片上有非 DRAM 的部分(DRAM 掩膜是空白的),我们也要为它们支付成本。同构集成的另一个问题是晶粒的尺寸可能会非常大。如果尺寸过大,晶粒可能会超出光刻极限,最终将无法制造。但即便没有超出极限,如果芯片面积相同,与四个单独的小晶粒相比,大晶粒的良率也会比较差。

《异构集成 (HI) 与系统级芯片 (SoC) 有何区别?》一文详细讲述了这两种设计工艺之间的区别以及各自的优势和注意事项,欢迎点击阅读。

COTS 小芯片

自动化程度更高的异构集成流程存在很多技术挑战。但最值得关注的问题是在商业领域。在此强调:这些问题暂时还没有答案。

COTS 指的是“commercial off the shelf(即商用现成品)”。通常情况下,它用于国防等专门行业,将可以轻松购买的芯片与必须为特定用途设计的专门芯片区分开来。关于异构集成,最值得关注的问题之一是 COTS 小芯片是否可用。或许最极端的情况是,能否用Intel的微处理器、NVIDIA的 GPU 和Qualcomm的 5G 调制解调器来构建一个 SiP?

目前已经有一些 COTS 小芯片(或小芯片堆栈)是可用的,如高带宽存储器 (HBM) 和 CMOS 图像传感器 (CIS) 视觉/AI 子系统。

为了扩大这一市场,让 COTS 小芯片可用,有几个重大问题需要解决:

小芯片将以芯片的形式提供,还是仅仅作为授权 IP 提供?

如果有实际的小芯片可用,那么谁将持有库存?

这是否仍将是一个“酒香不怕巷子深”的市场,依然要按需生产小芯片,只有在收到确定的订单后才会进行生产?

谁来管理小芯片的生产运营?

是否会出现新的公司来创造/服务这个市场?

这些问题在很大程度上归结为谁将承担财务风险:最终用户、中间商(如分销商)、设计小芯片的公司、代工厂,还是其他公司或供应商。就像任何价值链一样,所有参与者都希望将自己获得的收入/利润最大化,并试图将其他供应商商品化。当然,如果每个人在这方面都过于激进,那么就很有可能酿成杀鸡取卵的悲剧。或者变成揠苗助长,那么这种市场将永远不会成熟。

审核编辑 黄宇

-

芯片

+关注

关注

463文章

54441浏览量

469425 -

COTS

+关注

关注

0文章

23浏览量

11179 -

异构集成

+关注

关注

0文章

42浏览量

2356

发布评论请先 登录

PLA 3D打印材料使用年限是多久?耗材与成品的真实寿命解析

一径科技NZ系列广角全场景3D激光雷达全面赋能商用清洁机器人

2D、2.5D与3D封装技术的区别与应用解析

奥比中光领跑韩国机器人3D视觉市场

西门子EDA重塑3D IC设计:突破高效协同、可靠验证、散热及应力管理多重门

iTOF技术,多样化的3D视觉应用

3D封装的优势、结构类型与特点

华大九天推出芯粒(Chiplet)与2.5D/3D先进封装版图设计解决方案Empyrean Storm

3D异构集成与 COTS (商用现成品)小芯片的发展问题

3D异构集成与 COTS (商用现成品)小芯片的发展问题

评论