随着领先的芯片制造商继续将finFET以及很快的纳米片晶体管缩小到越来越小的间距,使用铜及其衬垫和阻挡金属,较小的金属线将变得难以维持。接下来会发生什么以及何时发生,仍有待确定。

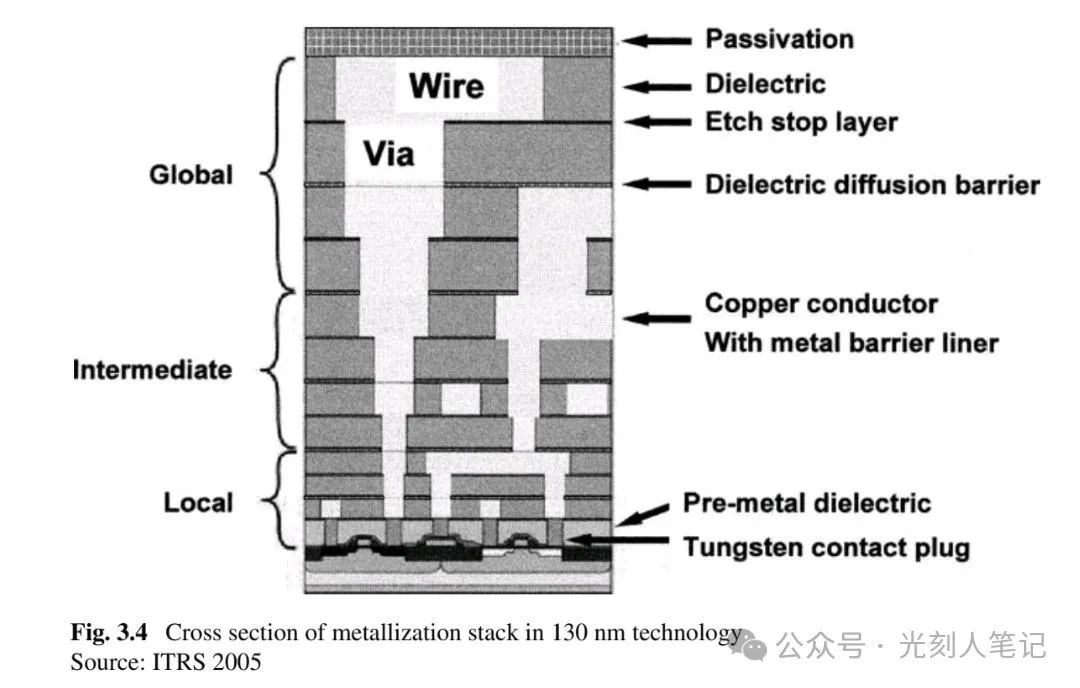

自从IBM在20世纪90年代向业界引入采用双镶嵌工艺的铜互连以来,半导体行业一直在利用铜的高导电性、低电阻率和可靠互连的优势。但随着电阻和电容的增加,RC延迟将继续显着影响器件性能。

与此同时,系统性能驱动因素使得在可能的情况下将存储设备移至生产线后端变得有吸引力。如果业界开始引入具有较低热预算的互连工艺,那么存储器或其他设备集成之类的事情就变得可行。但首先,必须解决延伸铜线和引入背面配电方案的直接工程挑战。

铜的里程更长

在2nm逻辑节点,铜线和通孔正在通过创造性的方式延伸。一些吸引力的选择包括限制阻挡层和衬垫材料的电阻率影响,要么通过使这些薄膜更薄——从化学气相沉积(CVD)到原子层沉积(ALD)——要么消除它们,例如沿着通孔和线路之间的垂直路径。

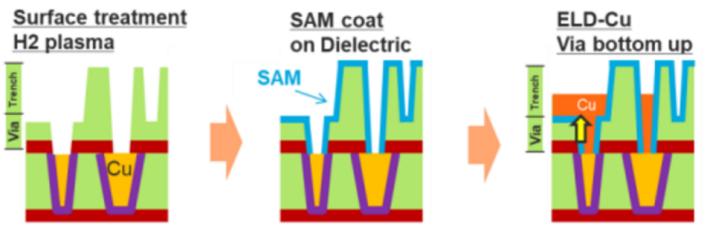

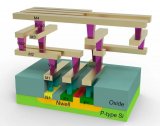

图1

图2

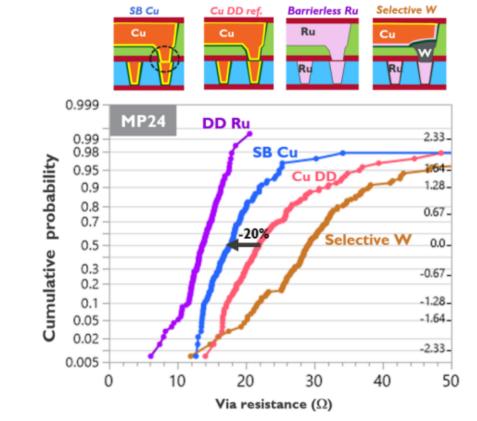

英思特测试了预通孔填充工艺,该工艺在铜填充下不使用阻挡层(TaN),而是在无电沉积(ELD)后进行沉积。微小过孔是互连链中的薄弱环节(图2),关键工艺步骤是在对通孔底部暴露的铜进行原位界面工程之后,仅在电介质上进行选择性ALD TaN阻挡层沉积,通过消除势垒,通孔电阻可降低20%。在较小的尺寸下,减少量会更大。

连接背面电源

背面供电(BPD)是一种从晶圆背面向晶体管供电的创新方法,从而释放正面互连以仅传输信号。这缓解了拥塞,利用晶圆背面进行配电,可以有效增加芯片的功能面积,而无需增加其占地面积。

背面电源集成的较大挑战之一是如何以电气方式连接晶圆正面和背面。较具挑战性的方案涉及到源外延的直接背面接触。通孔将很小且纵横比很高,还需要与外延层进行低电阻接触,就像正面的源极/漏极接触一样。因此,钨填充物或可能是钼将是可能的选择。

结论

如今,双镶嵌铜的间距已扩展到20纳米,但涉及钌或其他替代金属的减材方案即将发生根本性变化。就电阻率而言,随着尺寸降至17 x 17nm以下,钌变得有吸引力。公司可以使用无障碍通孔底部来获得额外收益,同时为伟大的转型做好准备。

审核编辑 黄宇

-

半导体

+关注

关注

339文章

31279浏览量

266786 -

晶圆

+关注

关注

53文章

5451浏览量

132780 -

晶体管

+关注

关注

78文章

10443浏览量

148703

发布评论请先 登录

Molex收购Teramount:CPO互连技术开启算力与能效的“双赢时代”

Co/TiN界面对钴互连电阻率的影响

MACOM公司推出高密度铜互连解决方案

京东方华灿光电和新相微正式签署战略合作协议

隆基绿能计划量产铜基太阳能电池

晶科储能进一步扩大英国储能项目布局

一文详解3D光电互连技术

TSV工艺中的硅晶圆减薄与铜平坦化技术

泡沫铜:独特性能、制备工艺与性能研究中的微观洞察

基于硅基异构集成的BGA互连可靠性研究

铜对芯片制造中的重要作用

从微米到纳米,铜-铜混合键合重塑3D封装技术格局

一文详解铜互连工艺

研究铜互连的规模能扩大到什么程度

研究铜互连的规模能扩大到什么程度

评论