电磁干扰的主要方式是传导干扰、辐射干扰、共阻抗耦合和感应耦合。对这几种途径产生的干扰我们应采用的相应对策:传导采取滤波,辐射干扰采用屏蔽和接地等措施,就能够大大提高产品的抵抗电磁干扰的能力,也可以有效的降低对外界的电磁干扰。本文从滤波设计、接地设计、屏蔽设计和PCB布局布线技巧四个角度,介绍EMC的设计技巧。

一、EMC滤波设计技巧

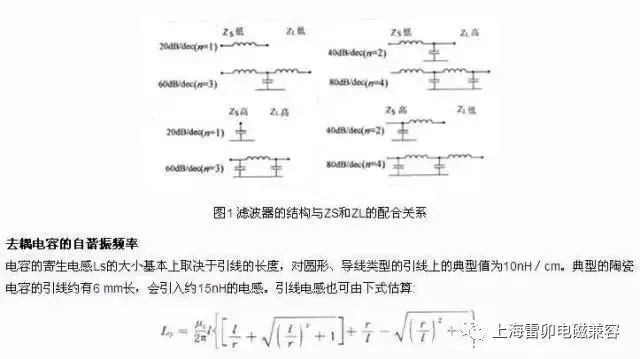

EMC设计中的滤波器通常指由L,C构成的低通滤波器。滤波器结构的选择是由"最大不匹配原则"决定的。即在任何滤波器中,电容两端存在高阻抗,电感两端存在低阻抗。图1是利用最大不匹配原则得到的滤波器的结构与ZS和ZL的配合关系,每种情形给出了2种结构及相应的衰减斜率(n表示滤波器中电容元件和电感元件的总数)。

其中:l和r分别为引线的长度和半径。寄生电感会与电容产生串联谐振,即自谐振,在自谐振频率fo处,去耦电容呈现的阻抗最小,去耦效果最好。但对频率f高于f/o的噪声成份,去耦电容呈电感性,阻抗随频率的升高而变大,使去耦或旁路作用大大下降。实践中,应根据噪声的最高频率fmax来选择去耦电容的自谐振频率f0,最佳取值为fo=fmax。

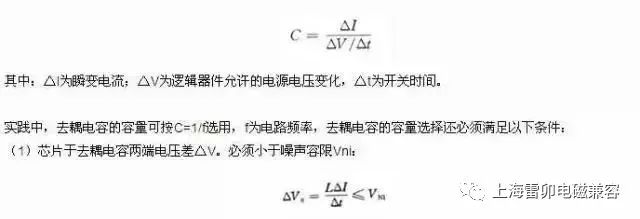

去耦电容容量的选择 在数字系统中,去耦电容的容量通常按下式估算:

二、EMC接地设计

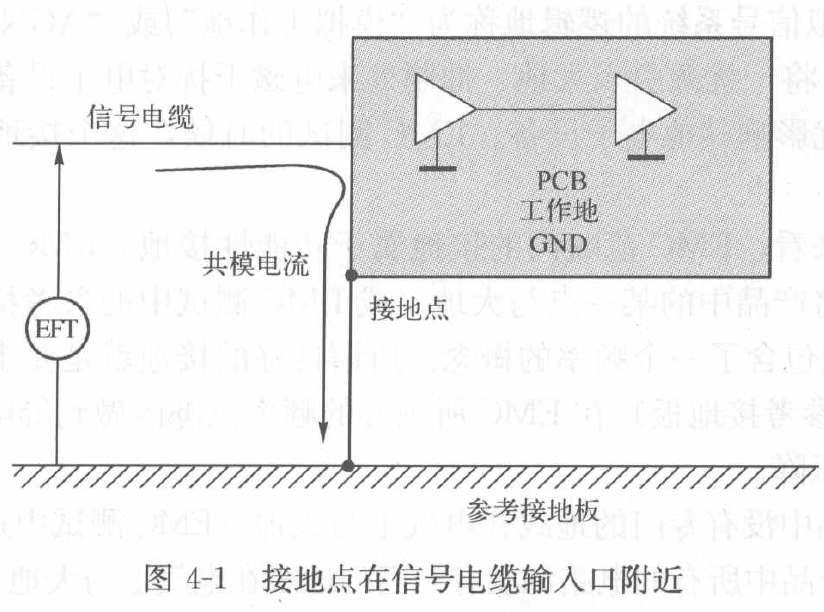

接地是最有效的抑制骚扰源的方法,可解决50%的EMC问题。系统基准地与大地相连,可抑制电磁骚扰。外壳金属件直接接大地,还可以提供静电电荷的泄漏通路,防止静电积累。

在地线设计中应注意以下几点:

(1)正确选择单点接地与多点接地

在低频电路中,信号的工作频率小于1MHz,它的布线和器件间的电感影响较小,而接地电路形成的环流对干扰影响较大,因而应采用单点接地。当信号工作频率大于10MHz时,地线阻抗变得很大,此时应尽量降低地线阻抗,应采用就近多点接地。当工作频率在1~10MHz时,如果采用一点接地,其地线长度不应超过波长的1/20,否则应采用多点接地法。

电路板上既有高速逻辑电路,又有线性电路,应使它们尽量分开,而两者的地线不要相混,分别与电源端地线相连。要尽量加大线性电路的接地面积

(3)尽量加粗接地线

若接地线很细,接地电位则随电流的变化而变化,致使电子设备的定时信号电平不稳,抗噪声性能变坏。因此应将接地线尽量加粗,使它能通过三位于印制电路板的允许电流。如有可能,接地线的宽度应大于3mm。

(4)将接地线构成闭环路

设计只由数字电路组成的印制电路板的地线系统时,将接地线做成闭环路可以明显的提高抗噪声能力。其原因在于:印制电路板上有很多集成电路组件,尤其遇有耗电多的组件时,因受接地线粗细的限制,会在地结上产生较大的电位差,引起抗噪声能力下降,若将接地结构成环路,则会缩小电位差值,提高电子设备的抗噪声能力。

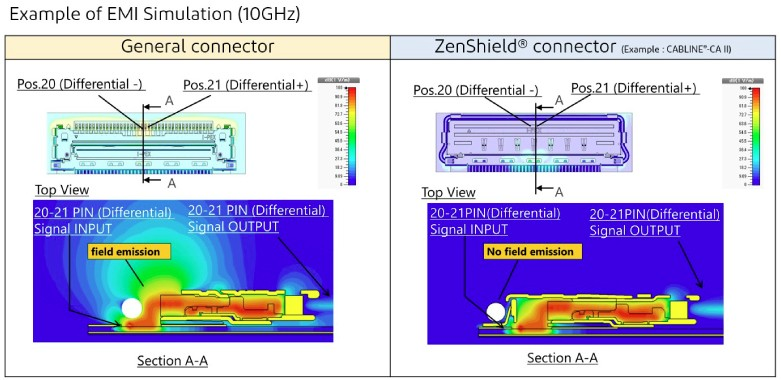

三、EMC屏蔽设计

屏蔽就是以金属隔离的原理来控制某一区域的电场或磁场对另一区域的干扰。它包括两个含义:一是将电路、电缆或整个系统的干扰源包围起来,防止电磁干扰向外扩散;二是用屏蔽体将接收电路、设备或系统包围起来,防止它们受到外界电磁干扰的影响。屏蔽按照机理可以分为电场屏蔽、磁场屏蔽、电磁场屏蔽三种不同方式。

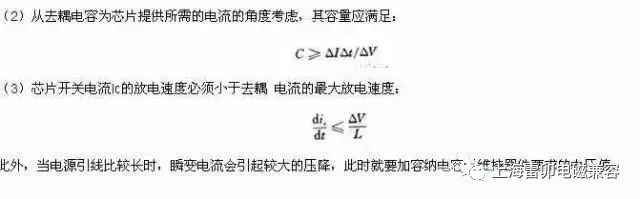

电场屏蔽电子设备中的电场通常是交变电场,因此可以将两个系统间的电场感应认为是两个系统之间分布电容Cj的耦合,如图2所示。

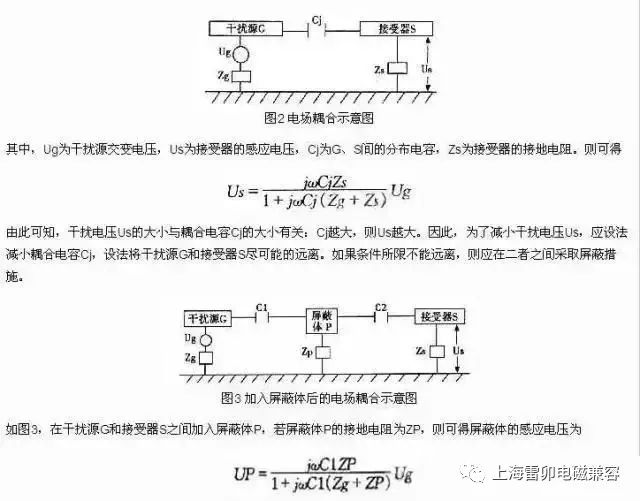

则接受器上的感应电压为:

由此可知,要使接受器的感应电压Us减小,Zp应尽可能的小。所以,屏蔽体必须选择导电性能良好的材料,而且须有良好的接地。否则,因为Cl>Cj,C2>Cj,若屏蔽体的接地电阻较大,将使屏蔽体加入后造成的干扰反而变得更大。

磁场屏蔽是指对低频磁场和高频磁场的屏蔽。

低频磁场的屏蔽采用高导磁率的铁磁性材料。利用铁磁性材料的高导磁率对干扰磁场进行分路,使通过空气的磁通大为减少,从而降低对被干扰源的影响,起到磁场屏蔽的作用。由于是磁分路,所以屏蔽材料屏蔽材料 的磁导率U越高,屏蔽罩屏蔽罩越厚,磁分路流过的磁通越多,屏蔽效果越好。

高频磁场的屏蔽采用低电阻率的良导体作为屏蔽材料屏蔽材料。外界高频磁场在屏蔽体中产生涡流,涡流形成的磁场抑制和抵消外界磁场,从而起到了屏蔽的作用。与低频磁屏蔽不同,由于高频涡流的趋肤效应,屏蔽体的尺寸并不是屏蔽效果的关键所在,而且屏蔽体接地与否和屏蔽效果也没有关系。但对于高频磁屏蔽的金属良导体而言,若有良好的接地,则同时具备了电场屏蔽和磁场屏蔽的效果。所以,通常高频磁屏蔽的屏蔽体也应接地。

电磁场屏蔽电磁场屏蔽是利用屏蔽体对电场和磁场同时加以屏蔽,一般用来对高频电磁场进行屏蔽。由前述可知,对于频率较高的干扰电压,选择良导体制作屏蔽体,且有良好的接地,则可起到对电场和磁场同时进行屏蔽的效果。但是必须注意,对高频磁场屏蔽的涡流不仅对外来干扰产生抵制作用,同时还可能对被屏蔽体保护的设备内部带来不利的影响,从而产生新的干扰。

四、PCB设计之布局布线策略

1.选择合理的导线宽度

由于瞬变电流在印制线条上所产生的冲击干扰主要是由印制导线的电感成分造成的,因此应尽量减小印制导线的电感量。印制导线的电感量与其长度成正比,与其宽度成反比,因而短而精的导线对抑制干扰是有利的。时钟引线、行驱动器或总线驱动器的信号线常常载有大的瞬变电流,印制导线要尽可能地短。对于分立组件电路,印制导线宽度在1.5mm左右时,即可完全满足要求;对于集成电路,印制导线宽度可在0.2~1.0mm之间选择。

2.采用正确的布线策略

布线时需要注意的几个方面:

(1)保持环路面积最小,降低干扰对系统的影响,提高系统的抗干扰性能。并联的导线紧紧放在一起,使用一条粗导线进行连接,信号线紧挨地平面布线可以降低干扰。电源与地之间增加高频滤波电容。

(2)使导线长度尽可能的缩短,减小印制板的面积,降低导线上的干扰。

(3)采用完整的地平面设计,采用多层板设计,铺设地层,便于干扰信号泄放。

(4)使电子元件远离可能会发生放电的平面如机箱面板、把手、螺钉等,保持机壳与地良好接触,为干扰提供良好的泄放通道。对敏感信号包地处理,降低干扰。

(5)尽量采用贴片元器件

(6)模拟地与数字地在PCB与外界连接处进行一点接地。

(7)高速逻辑电路应靠近连接器边缘,低速逻辑电路和存储器则应布置在远离连接器处,中速逻辑电路则布置在高速逻辑电路和低速逻辑电路之间。

(8)电路板上的印制线宽度不要突变,拐角应采用圆弧形,不要直角或尖角。

(9)时钟线、信号线也尽可能靠近地线,并且走线不要过长,以减小回路的环面积。

3.印制电路板的尺寸与器件的布置

印制电路板大小要适中,过大时印制线条长,阻抗增加,不仅抗噪声能力下降,成本也高;过小,则散热不好,同时易受临近线条干扰。在器件布置方面与其它逻辑电路一样,应把相互有关的器件尽量放得靠近些,这样可以获得较好的抗噪声效果。时钟发生器、晶振和CPU的时钟输入端都易产生噪声,要相互靠近些。易产生噪声的器件、小电流电路、大电流电路等应尽量远离逻辑电路,如有可能,应另做电路板。

-

pcb

+关注

关注

4417文章

23967浏览量

426184 -

滤波

+关注

关注

10文章

711浏览量

58071 -

接地

+关注

关注

7文章

875浏览量

47989 -

emc

+关注

关注

177文章

4453浏览量

192273

发布评论请先 登录

辐射超标、静电复位等等这些EMC问题背后藏着什么?

SAW 滤波器 PCB Layout 与 ESD 小技巧总结

改善EMC的PCB设计原理

【实战总结】EMC测试反复不过?8年整改老兵教你避开90%的无效努力

EMC整改实用小技巧

产品接地设计与 EMC 分析:打造电磁兼容的坚实基础

PCB的EMC设计(二):模块划分及特殊器件的布局

四大视角看EMC设计:滤波、接地、屏蔽、PCB布局

四大视角看EMC设计:滤波、接地、屏蔽、PCB布局

评论