本文将重点介绍如何在无需久等 SI 和 PI 专家反馈的情况下,助力 PCB 设计团队在预算范围内按时交付合格的产品。

对于当今设计高速、高密电路板的工程师来说,信号完整性 (SI) 和电源完整性 (PI) 是重中之重。而在设计早期阶段发现 SI/PI 问题,有助于加快设计签核,以免重新设计。

在签核高速 PCB 设计时,工程师需要解决三个关键问题:电源分析、SerDes 链路合规和 DDR 存储器接口合规。电源传输网络(Power Delivery Network, PDN) 必须充足、高效和稳定,信号质量必须符合存储器接口和串行链路合规规范。

1

设计分析框架

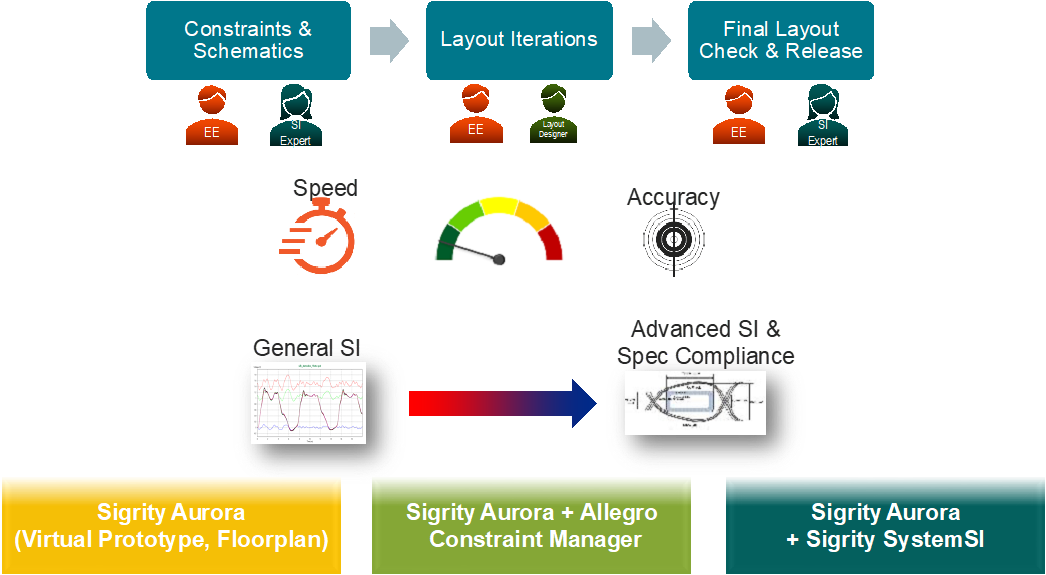

设计 PCB 时需要考虑几个重要框架(图 1)。

图 1:设计分析框架

设计的第一步是原理图;第二步是 layout,并在 layout 的后期阶段进行详细分析以确保 layout 功能符合预期。在设计周期中,任务、优先事项和工作重点都会变化,但有一条经验法则经久不衰:发现和纠正问题越早越好。

一般来说,设计流程的后期阶段才会进行详细的仿真、分析和优化,通常是验证和签核的最后一步。一旦此时发现需求和性能方面的缺陷,就需要花费额外的时间和人力来解决,不可避免地导致项目超出预算并延迟产品上市;然而这些问题原本在设计早期阶段就可以发现并解决——要在当今竞争激烈的电子市场中保持领先,则不能再将分析和验证放在设计流程的最后阶段;而是从设计流程的初始阶段开始,就采用设计同步分析 (In-design Analysis, IDA) 方法集成仿真和分析,将分析和验证视为在芯片、封装、电路板和完整系统级设计层面的各个阶段中都不可分割的一部分。

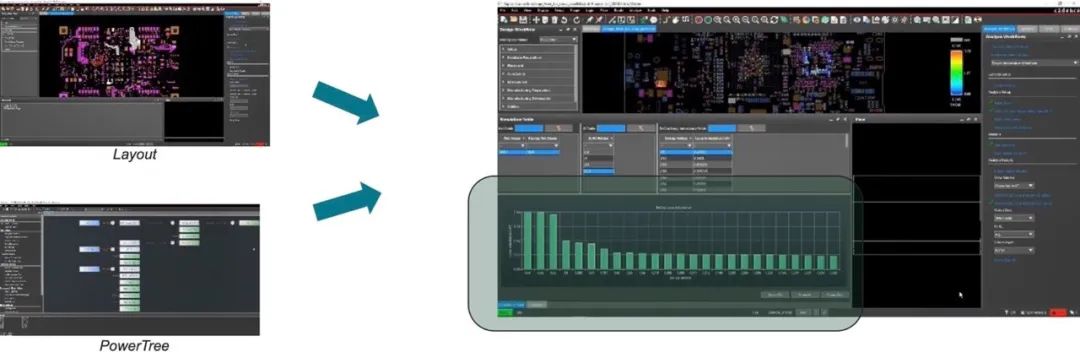

图 2:Allegro PCB Designer layout 环境中的设计同步分析工作流程与Cadence Sigrity Aurora PCB 分析软件集成

设计团队是设计过程中的一个重要因素。在设计初期, SI 工程师会来帮助理解设计约束等问题;在 layout 设计阶段,layout 设计专家将进行设计;而到了最终 layout 验证阶段,SI 工程师又将再次参与;但是在整个设计过程中,SI 工程师不一定能随时提供帮助。因此,要想按时交付设计并保质保量,PCB 设计人员需要具备独立执行普通 SI/PI 仿真的能力。在 PCB 设计环境中直接嵌入仿真工作流程,赋能设计人员,有助于确保设计符合预期并按时交付。

串扰和阻抗匹配等普遍的 SI/PI 问题往往需要在设计初期被快速解决。在设计后期,仿真的细节精确度非常重要,但在开始阶段,设计人员通常只需要确保方向正确。仿真精度与速度往往无法兼得,需要取舍。如果在一开始就需要细节精确度,设计人员可以缩小工作范围,只考虑设计的一个部分;而如果整个设计必须尽早进行精确仿真,那么分析工作流程可以利用复杂的分布式计算资源,确保速度精度双管齐下。

2

电源设计分析工作流程

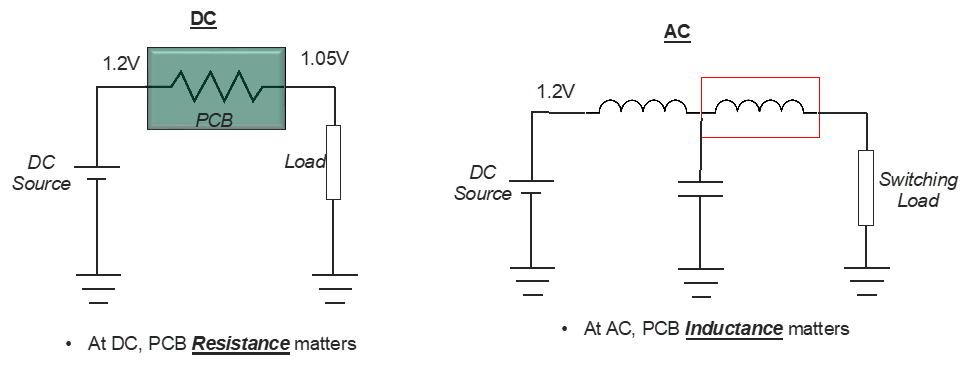

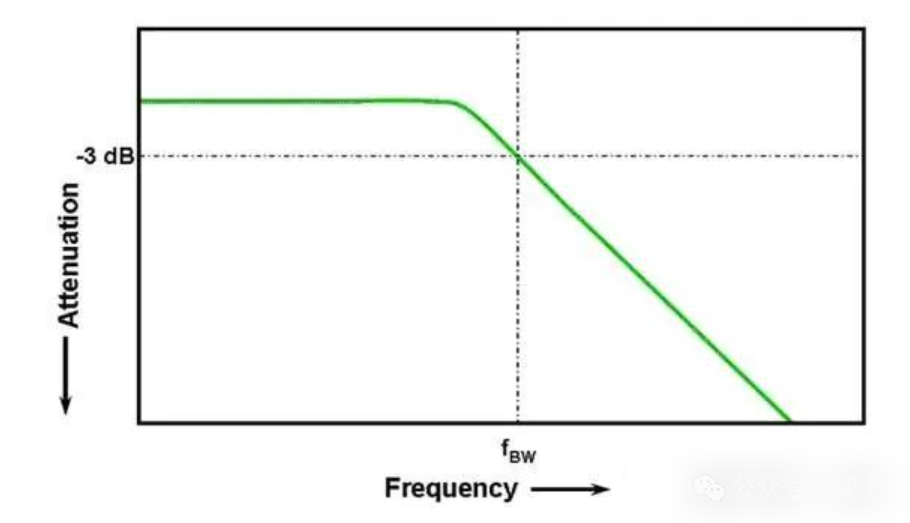

PCB 设计人员面临的一个主要挑战是为负载供电。电源正确的直流(幅度)和交流(纹波)对于发射 (Tx) 和接收 (Rx) 信号至关重要(图 3)。

图 3:发射和接收信号的元件需要充足且稳定的直流和交流电源

对于直流电路,电阻很重要;对交流电路来说,重要的则是电感。直流电路包括直流电源、PCB 和 IC 负载,电流需要流向这些负载。直流电源流过 PCB 上的铜,因其电阻并非是无穷小, PCB 上会存在压降,导致负载侧电压的幅度很可能会比原始电源的幅度低,因此需要分析负载端的电压是否足够。每种IC对供电电压都有要求,设计人员必须确保 IC 芯片获得了所需的电压。

直流分析的重点是 PCB 电阻。对于交流分析,逻辑和输入/输出 (I/O) 电路每秒要开关数百万个晶体管,每次晶体管开关时,都需要立即获得电流,这不太可能来自直流电源,因为 PCB 更像是一个电感器。在较高的开关频率下,电感阻抗远远大于电阻阻抗。因此,PCB 的电感十分关键。电感在很大程度上取决于 PCB 的几何形状,需要格外关注 PCB layout。电压调节器模块 (Voltage Regulator Module, VRM) 的电感几乎一定会过高,因此需要使用局部去耦电容来提供开关负载所需的瞬时电流。电容器与其负载之间的电感量很重要:电感越大,电容器的效能就越低,因此必须找到与负载连接的电感较高的电容器,并想办法降低电感。

电源工作流程:布线前

在设计流程的开始阶段,设计人员需要面对几十上百页的原理图、几十个电压轨,以及正确设置电源连接的要求。面对庞大而复杂的电源结构,如果能够以可视化的方式查看电源、负载、无源压降等位置,设计人员在避免短路或电源连接错误等问题上会更加得心应手。Cadence Sigrity PowerTree 能够可视化原理图中的电源连接,帮助设计人员在设计早期快速仿真,并发现意外的电阻降低或连接不当,以便在电路图中进行修正,避免布线后酿成大错。

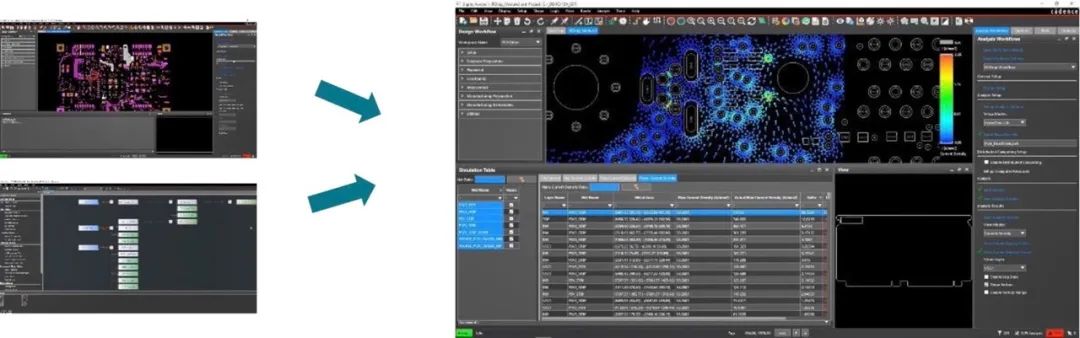

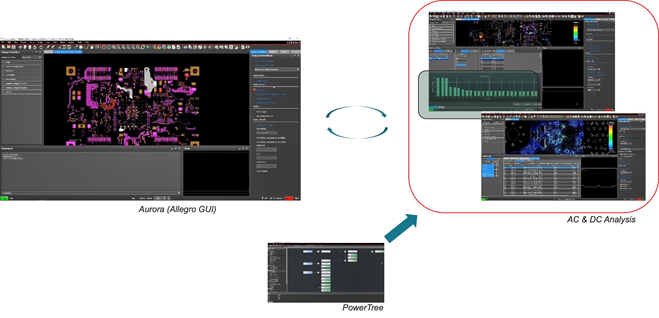

电源工作流程:layout 分析

在 layout 分析工作流程中,工程师可以使用之前创建的 PowerTree 文件与 layout 设计师合作创建电路板文件,分析直流电路并发现电流瓶颈。在进行直流分析时,需要重点了解流向 IC 负载的 VRM 源电流的大小、IC 获得的电流大小以及哪些 VRM 连接到哪些IC。PowerTree 文件已经捕获了所有这些信息,可以在 layout 环境中提供运行直流压降分析的一切所需,实现压降、电流、电流密度、过孔电流等参数的可视化(图 4)。

图 4:PCB layout 与 PowerTree 相结合,进行压降分析

还可以利用 CadenceCelsius Thermal Solver 中的电热协同仿真功能进行热影响分析,以了解电流密度的大小、产生的热量,以及是否可以有效散热。

交流分析以类似的方式进行。设计人员拥有电路板和 PowerTree 文件,可以快速运行交流分析,查看数百/数千个去耦电容的放置是否妥当,以及电容器与过孔的距离是否可以接受(图 5)。所选过孔上每个电容器的电感都会显示出来,设计人员可以快速查看环路电感中的异常值,发现去耦电容的不佳位置。如果有一个小型去耦电容的电感值过高,就意味着 layout 出了问题,设计人员需要先更改 layout,之后再继续设计。

图 5:PCB layout 与 PowerTree 相结合,进行去耦电容位置分析

IDA 可以利用 PowerTree 在布线前阶段已经获得的信息,帮助设计人员快速了解 layout 的质量,并在设计流程的早期解决问题。

3

SerDes 合规设计流程

SerDes 收发器的工作频率极高,会导致许多问题,所以在设计方面的容错率很低。未进行均衡的 SerDes 设计在接收器处可能无法获得良好的眼图,因此要使用 IBIS-AMI 模型模拟 Tx 和 Rx 处的均衡,以显示展开的眼图。在高速信号下,层之间的过渡非常敏感,必须选择合适的介电材料,甚至是过孔的位置也变得十分重要,以便尽量减少对通道的影响。

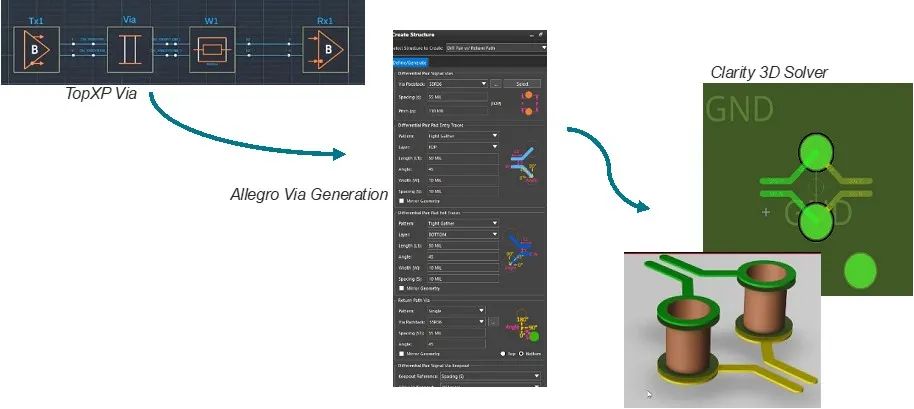

高速 SerDes 通道的 PCB 设计人员通常会在设计初期与 SI 专家一起研究过孔结构。过孔结构的优化可决定串行链路合规测试能否通过。

SerDes 设计挑战和解决方案

电气工程的基本规则是,速度越高,需要考虑的细节就越多。对于以前在低速设计中可以忽略的小结构,如果设计不当,可能会在高速设计中产生灾难性的影响。过孔会造成阻抗不连续,降低信号质量。因此需要仔细设计过孔结构,以便预测它的行为。

传统的做法是在原理图阶段预先设计结构中的每个过孔,满足速度要求。而利用设计工具中内置的技术,可以更高效地完成这一耗时的手工流程,轻松设计、仿真和优化用于高速信号传输的过孔。

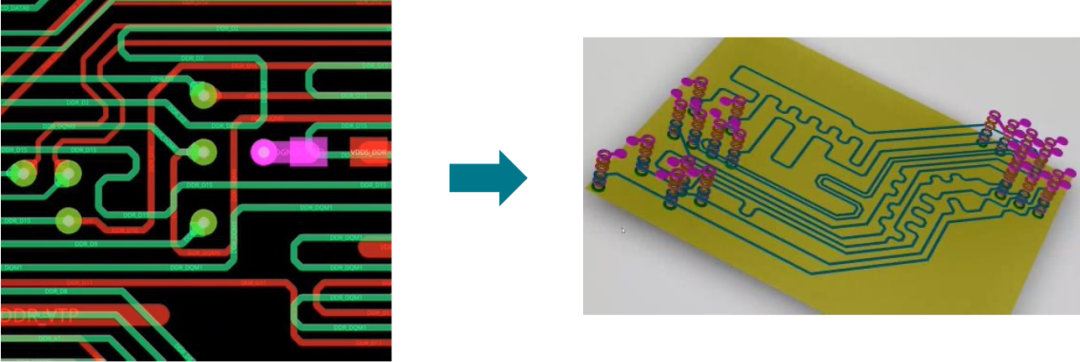

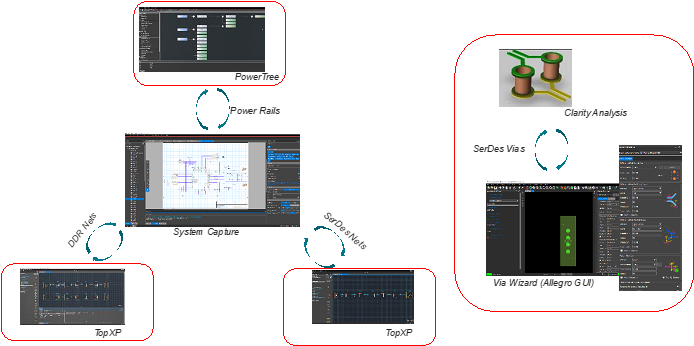

Cadence Sigrity Aurora 工作流程包括过孔向导,可快速生成基于 Allegro 的过孔结构。利用这一自动化流程,工程师可以在简单易用的 Allegro 环境中自行创建过孔结构,然后使用 Cadence Clarity 3D Solver 进行分析(图 6)。

图 6:利用 Sigrity Aurora 过孔向导工作流程,快速生成基于 Allegro 的过孔结构,并使用 Clarity 3D Solver 对过孔进行分析和优化

按照惯例,这属于 SI 专家的工作范畴,但有了 IDA 工具,PCB 设计人员不必依赖 SI 专家的帮助,可以自主完成。整个流程简单易用,包括设置结构,然后在过孔向导环境中打开 Clarity 3D Solver,运行仿真,评估结构的有效性,并在流程早期阶段进行调整。

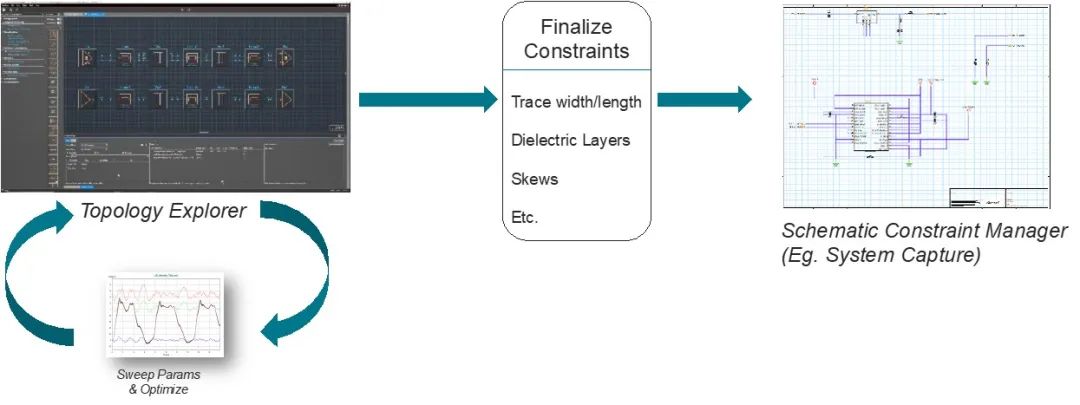

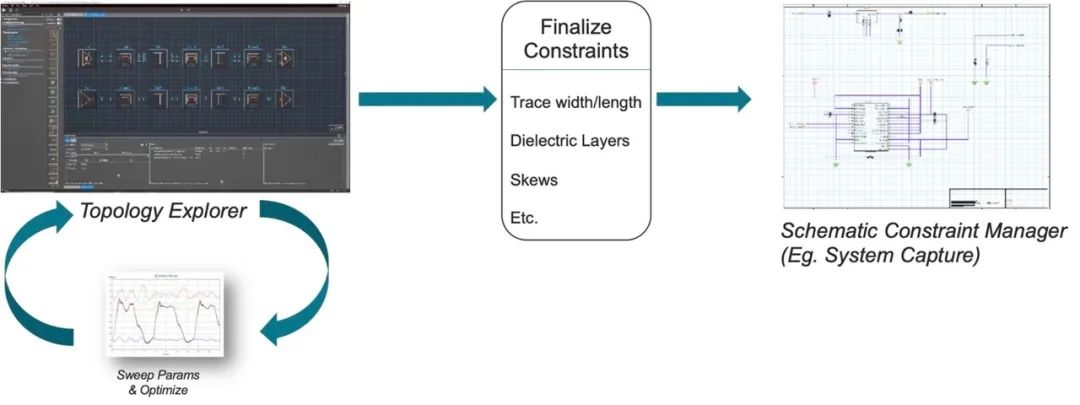

SerDes 面临的另一个挑战是通道设计中的损耗。在高速运行时,介质材料的损耗可能非常大,因此对通道性能而言,选择合适的材料、长度等至关重要。许多问题,如堆叠、走线宽度和距接地平面的高度,都需要预先确定。使用 Sigrity Topology Explorer(TopXp)工具对设计中提取的信号进行仿真,设置并扫描参数扫描,将最小/最大长度/间距值输入 Allegro 原理图规则管理器(Allegro System Capture)。初步规则和原理图流程如图 7 所示。随着设计的推进,根据最终确定的堆叠和材料,可以对这些规则进行调整。

图 7:使用 Sigrity Topology Explorer (TopXp) 中的 sweep manager 工具处理 SerDes 规则和原理图工作流程

原理图阶段结束后,开始进入 layout 阶段,下一个挑战是规范合规。规范取决于技术:PCIe、USB 等,每种技术都有自己的要求,所以这是一个复杂的过程。在分析过程中,一定要使用正确的发射器和接收器 IBIS-AMI 模型。对于通道,可以使用 Cadence 工具来准确地建立通道模型和地址规范。

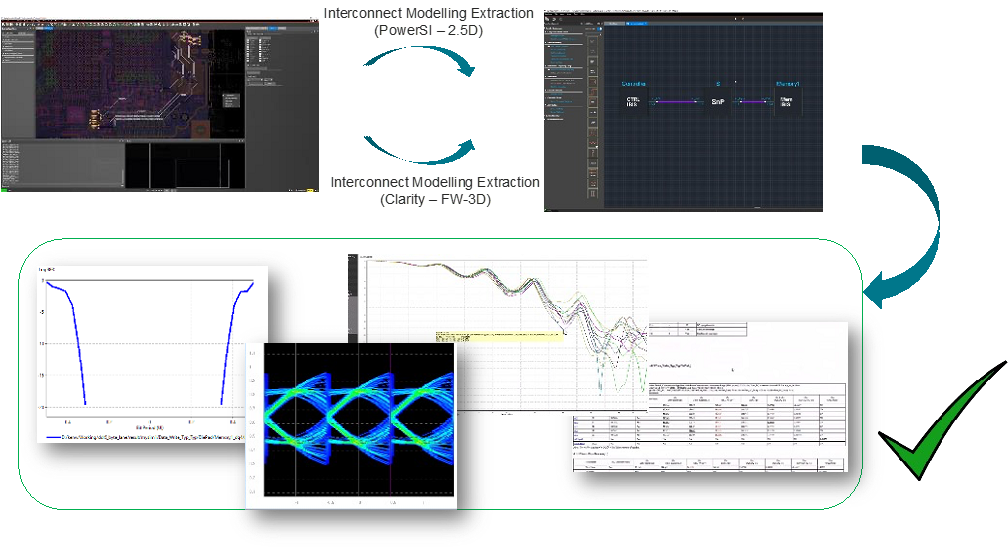

具体而言,可以使用 layout 设计师创建的电路板文件,选择几个或所有通道(取决于时间是否充足),然后对整个通道运行 2.5 或全 3D 分析(图 8)。

图 8:通道准确建模,实现规范合规的工作流程

利用通道提取的结果,可以根据所需的协议运行合规分析。这类分析可能需要重复几次,因为往往会出现一些在初步阶段没有确定的模糊要求,需要额外的迭代。

4

DDR 合规分析流程

DDR 的速度不如 SerDes 快,在某些方面也没有 SerDes 那么复杂,但会带来更多的信号完整性挑战。某些 DDR 的速度可能与 SerDes 的最低速度重叠,而且有大量的单端和差分网络,它们都需要满足复杂的信号完整性要求。

DDR 设计挑战

早期阶段的 DDR 信号完整性问题通常涉及阻抗匹配和信号不连续、双列直插式内存模块 (Dual In-line Memory Modules ,DIMM) 等桩线、端接优化和走线串扰等普遍的问题。尽管是基本要求,但重要的是要确保考虑到这些以及更复杂的问题,而且越早越好。为此,与 SerDes 一样,可以通过Sigrity Topology Explorer进行扫描,从而快速检查这些问题。通过仿真扫描可以确定约束条件,并将其与原理图一起保存(图 9)。

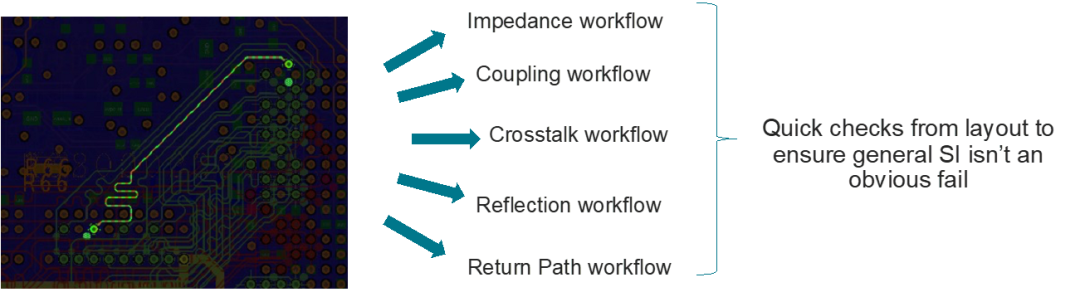

图 9:在原理图规则管理器中优化 TopXp 拓扑扫描

生成带规则的初步原理图后,即进入 layout 阶段。在这一阶段,IDA 可为 PCB 设计人员提供早期布局验证,增强对layout 正确性的信心。为此,可以在 Allegro layout 环境中使用 Sigrity Aurora 工作流程快速运行一系列惯例的 SI 分析(阻抗、耦合、串扰、反射、返回路径等),在走线上直观地显示问题所在,减少 SI 专家和 layout 设计人员的反复沟通,及时准确地快速解决问题,缩短设计时间。

如果 layout 设计人员无法解决上述问题,则可以再次使用 Sigrity Typology Explorer来运行迭代。如此一来,设计人员还可以在 layout 阶段对初步规则进行精细调整,更新数值,使之可用于其他信号。

除了通常在原理图和 layout 阶段解决的一般信号完整性问题外,DDR 的性质带来了三个其他挑战:同步开关噪声 (Simultaneous Switching Noise, SSN)、过孔串扰和 JEDEC 标准合规。

SSN 挑战

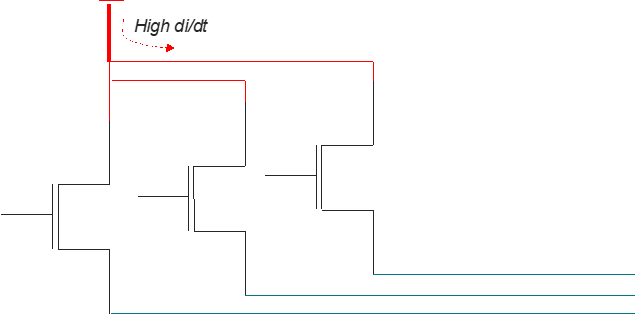

在 SSN 中,晶体管驱动单个比特的输出,从电压轨获取所需功率并将其输入到网络中。通常,可从 IBIS 文件或分析中捕获晶体管的行为。使用 DDR 时,多个网络可以同时切换,并且状态之间的转换会有高电流变化率 (di/dt) 要求,这会影响电压电平,反过来又影响转换(图 10)。有两种模型对 SSN 的精确建模至关重要:兼顾电源影响的 IBIS 模型和 PDN 精确模型。

图 10:多个网络可同时切换,这对 di/dt 有很高的要求,因此电压电平和转换相互影响

返回路径过孔的挑战

在图 11 左侧,绿色的线代表数据线 (DQ) 信号过孔,粉红色区域是接地 (GND) 过孔,它将两个接地平面拼接在一起。在图片右侧,其中一个信号在绿色顶层上有一条走线,而第二条线将作为具有理想返回路径的参考线。

图 11:信号过孔的返回路径

然而,返回电流必须流到倒数第二层,为此要找到最近的路径。信号直接流向信号过孔,而返回路径则位于信号的正下方,然后信号必须找到通向缝合过孔的路径,然后再返回,这样就又回到底层。所有信号过孔都会经历同样的情况——它们都使用相同的缝合过孔作为返回路径,从而导致过孔-过孔串扰。这是一种 3D 现象,而不是简单的 2D 并行的问题。需要进行 2.5 或 3D 分析来准确建模,借助 Sigrity Aurora 分析工作流程,即便不是 SI 专家也能完成这一任务。

JEDEC 规范的复杂性

JEDEC 的要求非常复杂,并且含有许多符号或缩略语(Vix, tDQSS, tDSS, tDS, tDSH tDH, tVAC 等....)。此外,不同技术(如 DDR、低功耗 DDR (Low Power DDR, LPDDR)、图形 DDR (Graphics DDR, GDDR))、不同版本(DDR3 与 DDR4)以及不同总线(如地址与数据、时钟信号 (Clock Signal, CLK) 与 DQ 选通 (DQ Strbe, DQS))的要求也各不相同。

例如,DDR4 数据要求矩形眼图模板,需要测量误码率 (Bit Error Rate, BER), DDR5 则要求的是菱形。在 Cadence PCB layout 环境中的分析工作流程中,可以使用 Sigrity PowerSI 和 Clarity 3D Solver 提取引擎,进行详细、精确的互连建模,轻松应对 SSN、返回路径过孔和 JEDEC 规范合规挑战。

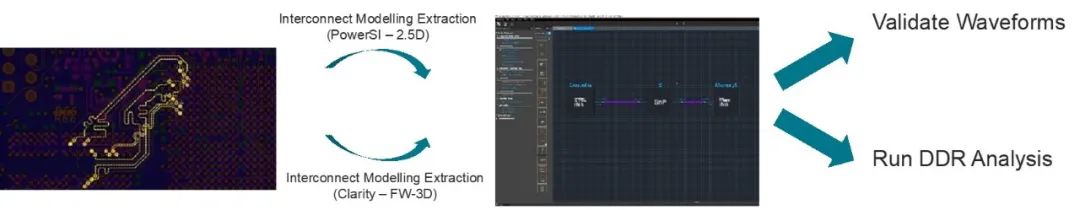

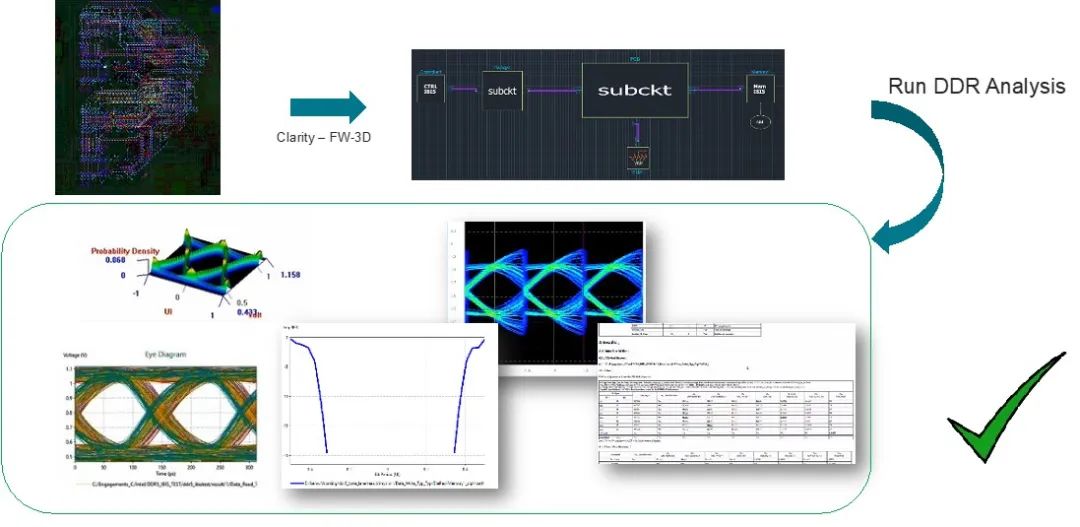

互连模型提取

在 DDR 工作流程的后期,网络已经铺设完成,初步的 DDR 检查也已经完成。现在,需要提取 2.5 或 3D 互连模型进行 layout 验证。按时间安排,可以针对一个部分、一个通道或几个信号进行提取。根据已提取的信息,可执行快速波形验证,确保波形正确(图 12),还可以使用 Sigrity PowerSI 2.5D 或 Clarity 3D Solver 运行快速 DDR 分析,确保设计满足所有要求。

图 12:提取互连模型用于验证波形和运行 DDR 分析

通过这种流程,设计人员还可以有条不紊地检查过孔串扰效应、兼顾电源影响的效应和其他高级效应,确保通道符合 DDR 规范。同样,这一流程使 PCB 设计人员能够独立完成大部分验证工作,减少对 SI 专家的依赖。

然后,在最终检查中,使用 Clarity 3D Solver 对整个电路模块进行全波 3D 仿真分析,确保捕捉到每个细节,并运行 DDR 合规分析检查(图 13)。

图 13:在最终设计检查中,使用 Clarity 3D Solver 对整个模块进行 DDR 分析

对于合规分析,仿真工作流程会针对所选的特定协议提供所有结果。如果设计通过这一流程,就表示电路板的功能一切正常。

5

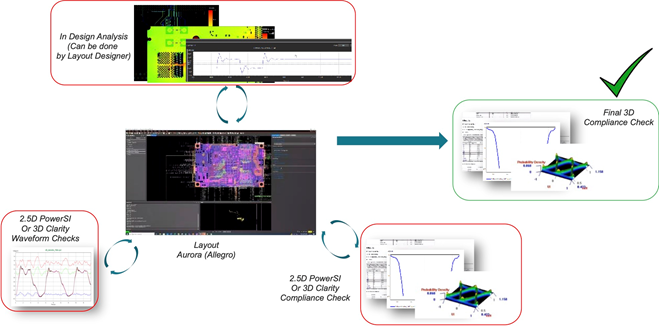

电路板设计示例

本例是一个真实的 PCB 设计,展示了如何使用 Cadence Allegro/Sigrity/Clarity来简化设计过程。图 14 展示了设计的规则阶段。

图 14:PCB 设计实例的规则阶段

该设计处于原理图阶段,PowerTree 文件用于显示电源轨并验证其设置是否正确。在这一阶段,还将运行一些迭代 DDR 仿真,以确保首次通过的规则正确无误。也可以采用同样的流程运行 SerDes 仿真,确保选择合适的电介质、堆叠准确无误等。与此同时,设计人员可以使用 Clarity 3D Solver为 SerDes 设计设置正确的通孔结构并运行分析,然后将其用于 layout 中。

下一阶段是电源分析,如图 15 所示。

图 15:PCB 设计实例的电源分析阶段

现在可以使用初期的 layout 和先前设置的 PowerTree 文件来执行初步的交流和直流分析,确保有足够的电源平面用于直流压降,并且电感足够低,以便电容器在高频下有效工作。由于 layout 和 PowerTree 文件在前一阶段已经完成设置,这一阶段进行起来要快得多,也容易得多。

图 16:PCB 实例的高速设计阶段

在这一阶段,PCB 设计人员与 layout 专家一起运行惯例 SI 分析,找出信号不连续的问题。使用 Cadence 流程,layout 设计人员可以直观地发现并纠正问题,而无需让 PCB 设计人员参与迭代。设计交回到 PCB 设计人员手中时,细节问题已经纠正,设计版面更加整洁,花费的时间也更少。PCB 设计可以直接进入 2.5D 或 3D 通道提取阶段,以执行波形检查,甚至还可以执行一些合规检查。此时已接近设计的尾声,因此可能只需要检查某些层的合规性。

最后一步是使用 Clarity 3D Solver 对 SerDes 和 DDR 进行完整的全波 3D 合规检查,以验证整个设计。

本文结论

利用设计同步分析 (IDA) 在设计流程早期发现 SI/PI 问题,有助于快速完成复杂的高速和/或高密度电路板的验证和最终签核。虽然 PCB 设计人员可能需要稍长的时间,来完成设计迭代并纠正基本的 SI/PI 问题,但这样可以减少重新设计,为项目节省大量的时间和成本。

本文重点阐述了要成功将产品推向市场,PCB 设计团队需要解决的三大关键问题:电源分析、SerDes 链路合规和 DDR 存储器接口合规。采用上述方法,PCB 设计人员能够依靠自己的力量,在预算范围内按时交付合格的产品,而无需等待 SI 和 PI 专家抽出时间提供帮助,也不必使用复杂难懂的分析工具。

-

电源

+关注

关注

185文章

18985浏览量

264545 -

pcb

+关注

关注

4417文章

23965浏览量

426177 -

电路板

+关注

关注

140文章

5344浏览量

109019 -

PCB设计

+关注

关注

396文章

4939浏览量

95780

发布评论请先 登录

PCB板表面张力对三防漆涂覆的影响,如何改善?

华为发布智能体通信网络的三大关键技术能力

高速PCB谐振威力,不容小觑

三防漆PCB设计六大关键要素解析 |铬锐特实业|东莞三防漆

FPGA DSP模块使用中的十大关键陷阱

从FPGA应用前景视角解读Gartner 2026十大关键技术趋势(下)

从FPGA应用前景视角解读Gartner 2026十大关键技术趋势(上)

开源鸿蒙在三大关键领域落地规模化商用案例

为什么高速信号链路 = 芯片 + PCB + 极细同轴线束三者匹配?

工控板SMT贴片加工:七大关键工艺要求详解

中国信通院发布“2025云计算十大关键词”

改善高速 PCB 签核的三大关键

改善高速 PCB 签核的三大关键

评论