FPGA的BRAM和LUT等资源都是有限的,在FPGA开发过程中,可能经常遇到BRAM或者LUT资源不够用的情况。

一般建议BRAM和LUT资源的消耗不要超过80%,当然高端一点的FPGA芯片也可以放宽到90%,超过这个限制,可能就会出现时序违例较严重的情况,导致上板运行出现异常的情况。

今天分享一下BRAM资源使用优化策略,以Vivado的 Block Memory Generator为例 。

1、Distribute BRAM或URAM 替代BRAM

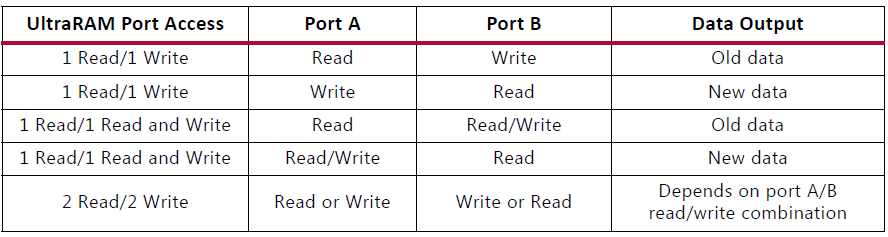

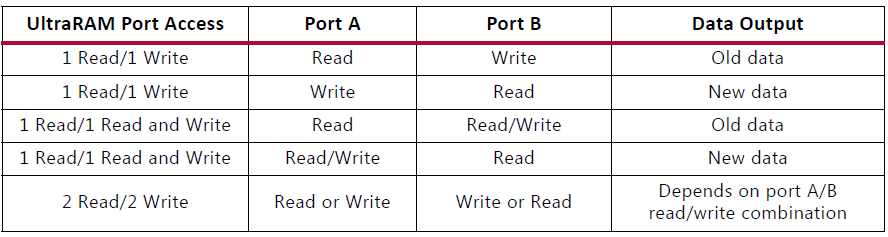

存储深度和宽度较小,且LUT资源或URAM有富裕,可以用“Distribute BRAM”或“URAM”来替代。

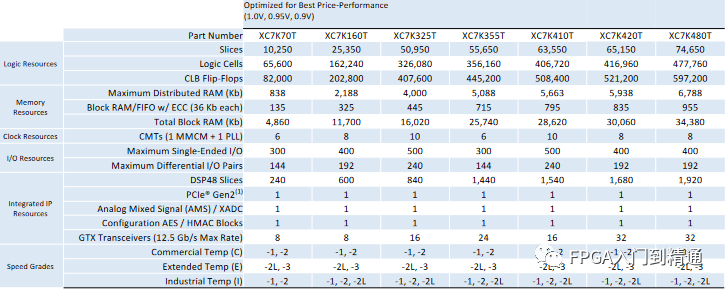

这里需要注意使用的FPGA芯片型号,是否带URAM资源。

- (* ram_style = "block" *)表示用Block RAM实现

- (* ram_style = "reg" *)表示用寄存器实现

- (* ram_style = "distributed" *)表示用分布式 RAM实现

- (* ram_style = "uram" *)表示用uram实现

这里给出代码示例:

// FPGA 双口 RAM

module dual_port_ram(

input clk,

input [7:0] data_in,

input [5:0] wr_addr,

input wr_en,

input [5:0] rd_addr,

output reg [7:0] data_out

);

// 声明双口 RAM 存储器

(* ram_style = "block" *)reg [7:0] ram[63:0];

// 时钟上升沿写入

always @(posedge clk) begin

if (wr_en)

ram[wr_addr] <= data_in;

end

// 读取;

always @(posedge clk) begin

data_out <= ram[rd_addr];

end

endmodule

2、双口ROM替代单口ROM

如果工程中,有两个以上的ROM或RAM使用的是相同的数据,可以使用双口替代单口模式,资源消耗是一样的,这样就可以节省一个或多个ROM IP。

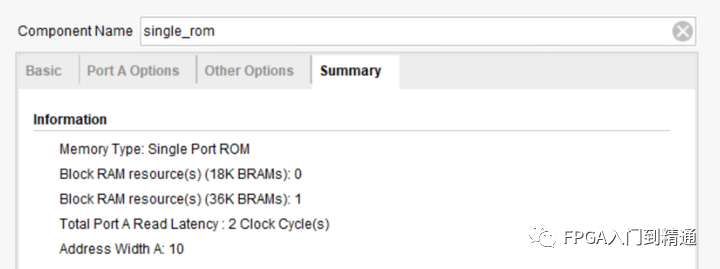

这里对比一下“数据宽度为32,存储深度为1024”的单口和双口模式下的资源消耗。

3、合理的数据宽度和深度设置

要想FPGA BRAM资源消耗优化,更关键的是优化FPGA工程的缓存大小设计,计算理论上缓存数据的位宽和最大深度,选择出合适的参数。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22503浏览量

639275 -

芯片

+关注

关注

463文章

54429浏览量

469374 -

ROM

+关注

关注

4文章

579浏览量

89373 -

资源

+关注

关注

0文章

59浏览量

18429 -

BRAM

+关注

关注

0文章

43浏览量

11708

发布评论请先 登录

相关推荐

热点推荐

【FPGA ZYNQ Ultrascale+ MPSOC教程】33.BRAM实现PS与PL交互

有时CPU需要与PL进行小批量的数据交换,可以通过BRAM模块,也就是Block RAM实现此要求。本章通过Zynq的GP Master接口读写PL端的BRAM,实现与PL的交互。在本实验中加入了自定义的FPGA程序,并利用AX

FPGA资源优化方法

各位大神,小弟最近在做一个项目,由于之前选用的FPGA资源不够,现在需要将程序的资源占用率降下来。经过我的冥思苦想,也找不到好的方法,不知道各位大神平时工作中降低资源利用率的方法有哪些

发表于 04-04 00:32

【InTime试用体验】使用简易、策略选择精确度高的一款时序优化软件

解决FPGA时序优化问题的软件。InTime 内嵌学习引擎,可以智能分析FPGA设计,为综合和布局布线提供更优的策略组合。同时,根据对器件、设计和工具特点的了解,以及独有的算法,InT

发表于 07-05 11:00

FPGA实现基于Vivado的BRAM IP核的使用

的使用。 BRAM是FPGA定制的RAM资源,有着较大的存储空间,且在日常的工程中使用较为频繁。BRAM以阵列的方式排布于FPGA的

使用FPGA调用RAM资源的详细说明

FPGA可以调用分布式RAM和块RAM两种RAM,当我们编写verilog代码的时候如果合理的编写就可以使我们想要的RAM被综合成BRAM(Block RAM)或者DRAM(Distributed

发表于 12-30 16:27

•9次下载

FPGA布局及资源优化

DDR3。 2.FPGA架构设计问题 我们知道,FPGA片上分布着各种资源,如时钟,serdes,RAM,LUT,IO等。在进行FPGA规划时候,应当需要知道项目设计需求,以及需求各

URAM和BRAM有哪些区别

无论是7系列FPGA、UltraScale还是UltraScale Plus系列FPGA,都包含Block RAM(BRAM),但只有UltraScale Plus芯片有UltraRAM也就是我们所说的URAM。

URAM和BRAM有什么区别

无论是7系列FPGA、UltraScale还是UltraScale Plus系列FPGA,都包含Block RAM(BRAM),但只有UltraScale Plus芯片有UltraRAM也就是我们所说的URAM。

发表于 01-27 06:55

•12次下载

FPGA实现基于Vivado的BRAM IP核的使用

定制的RAM资源,有着较大的存储空间,且在日常的工程中使用较为频繁。BRAM以阵列的方式排布于FPGA的内部,是FPGA实现各种存储功能的主要部分,是真正的双读/写端口的同步的RAM。

基于FPGA设计的BRAM内部结构

再看末级触发器对BRAM时序性能的影响,下图依次展示了7系列FPGA、UltraScale+和Versal芯片在未使用和使用末级触发器两种情形下时钟到输出的延迟。

发表于 04-25 10:42

•1283次阅读

HLS设计中的BRAM使用优势

高层次综合(HLS)是一种将高级编程语言(如C、C++或SystemC)转换为硬件描述语言(HDL)的设计方法。在FPGA设计中,设计者可以灵活地利用FPGA内部的资源,如块RAM(BRAM

FPGA的BRAM资源使用优化策略

FPGA的BRAM资源使用优化策略

评论