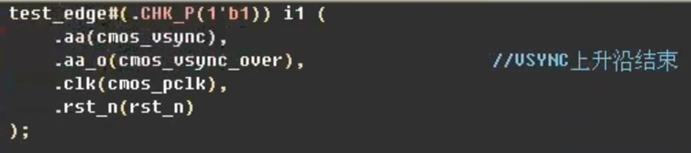

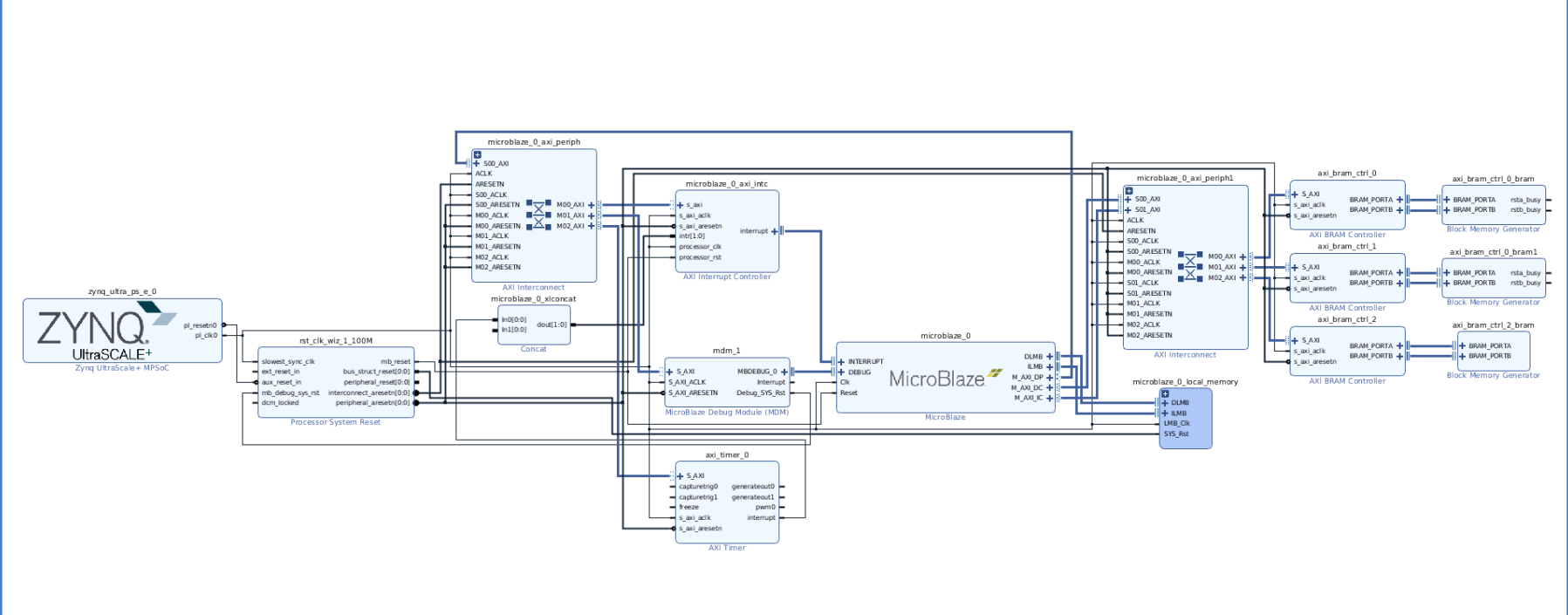

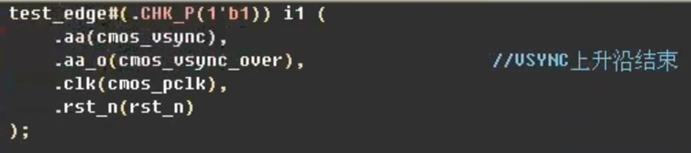

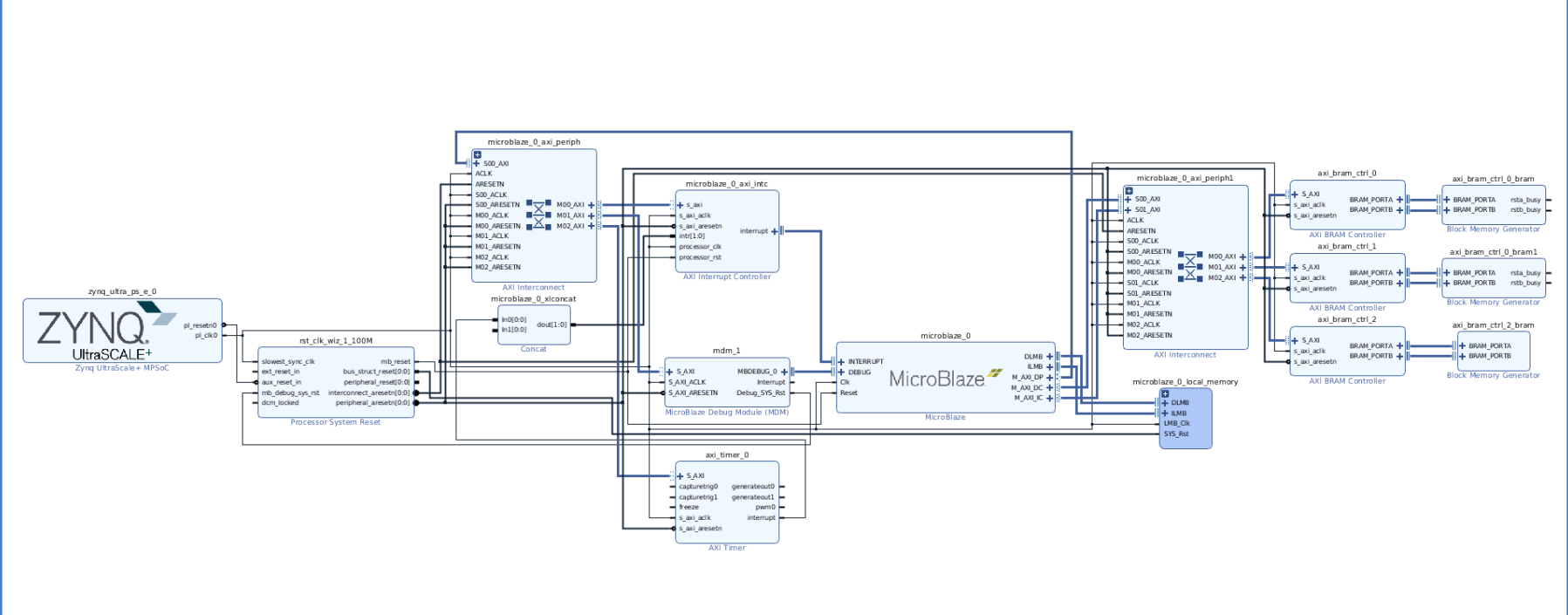

有时CPU需要与PL进行小批量的数据交换,可以通过BRAM模块,也就是Block RAM实现此要求。本章通过Zynq的GP Master接口读写PL端的BRAM,实现与PL的交互。在本实验中加入了自定义的FPGA程序,并利用AXI4总线进行配置,通知其何时读写BRAM。

2021-02-22 13:51:00 9725

9725

FPGA内嵌的存储器单元包括块RAM(BRAM)和分布式RAM。

2023-08-15 16:11:05 1820

1820

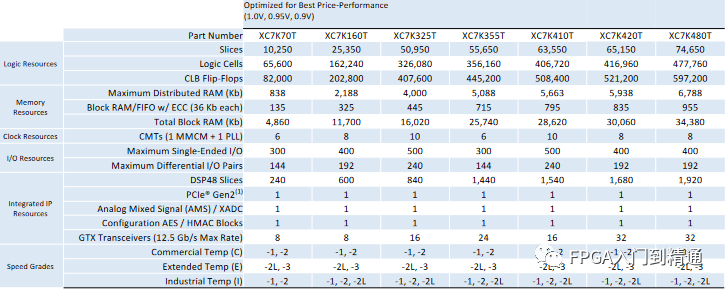

在选择FPGA时,关注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因为它们是FPGA架构中的两个核心资源,对于设计的性能和资源利用至关重要。

2023-11-21 15:03:06 4794

4794

BRAM IP核包括哪几种类型?Vivado中xilinx_BRAM IP核怎么使用?

2021-03-08 07:11:54

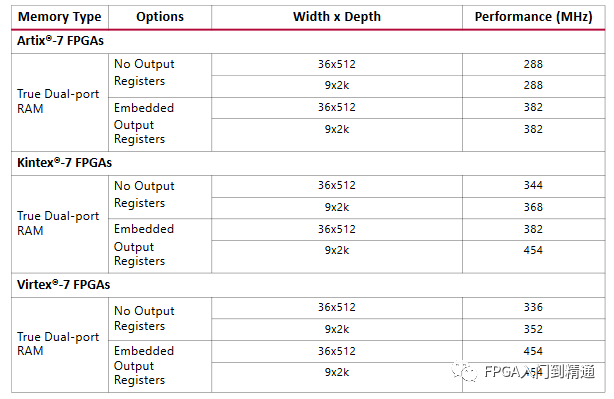

嗨,考虑到所有因素,设备BRAM的最高速度是多少,它是FPGA速度的25/50 / 75%?是的我知道外部延迟和路由将最终控制最大值,但有任何技术考虑因素表明BRAM只能以设备速度的百分比计时。C。

2020-06-02 11:57:26

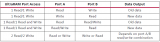

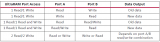

我正在使用具有真正双端口的BRAM控制器来将FPGA逻辑与微型接口连接起来。我可以在UART上读取这些内存位置。但是,BRAM的读访问似乎存在一些问题。如图所示,当我写入多个位置(WEA

2020-04-24 09:05:01

嗨,大家好,最近,在我的设计中,我正在努力解决BRAM阻塞RAMB16BWE引起的问题。给出的警告示例如下:PhysDesignRules:812- 块上的悬空引脚:: 16BWE>。组件

2019-05-27 08:35:05

亲爱的FPGA专家,美好的一天!有人可以告诉我BRAM,DRAM和DMA之间的区别吗?在什么特定情况下,每个适合使用?我们正在使用xilinx zedboard设备。非常感谢你。最好的祝福,格伦以上

2019-04-29 10:24:38

FPGA入门知识介绍近几年来,由于现场可编程门阵列(FPGA)的使用非常灵活,又可以无限次的编程,已受到越来越多的电子编程者的喜爱,很多朋友都想学习一些FPGA入门知识准备进行这个行业,现在关于

2014-08-16 10:32:45

重要组成部分,所以我们将重点介绍Vitis HLS。LUT 或 SICELUT 或 SICE是构成了 FPGA 的区域。它的数量有限,当它用完时,意味着您的设计太大了!BRAM 或 Block

2022-09-07 15:21:54

可控进程难以阻挡,国产当自强。产业链角度来看,硬件产业链中目前自主可控程度较低,尤其在高端半导体设备和材料领域,未来产业链上下游国产替代进程的推进也将助力国产 FPGA 加速发展。

硬件部分上游

2024-03-08 14:57:22

本文转载自IT之家,IT之家 3 月 17 日消息 中国科学技术协会官方微信公众号 “科普中国”昨天发文为大家科普了正确的手机充电 “姿势”,并建议给手机充电时先用充电器插电源,然后插手机。文章首先科普

2021-09-14 07:23:54

在NGDBUILD期间发现了错误ERROR :: 90 - 在网表中找不到BRAM实例'A_digital_top / A_core_12 / A_cpu_top / A_rom_wrapper / A_ram1kx32m32_wrapper_0 / A_RAMB36E1_IROM0'。让我知道如何解决这个问题。谢谢,肖恩

2020-04-23 08:53:52

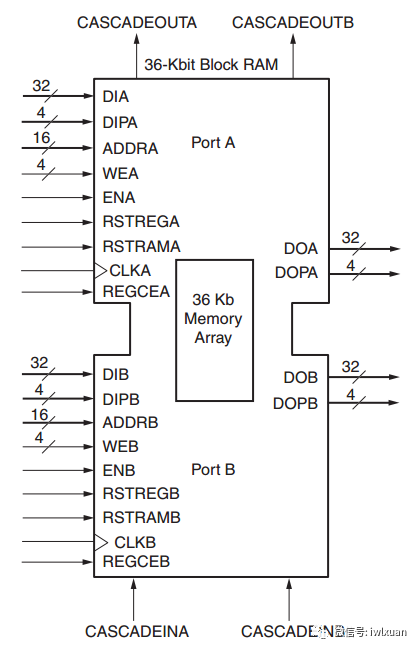

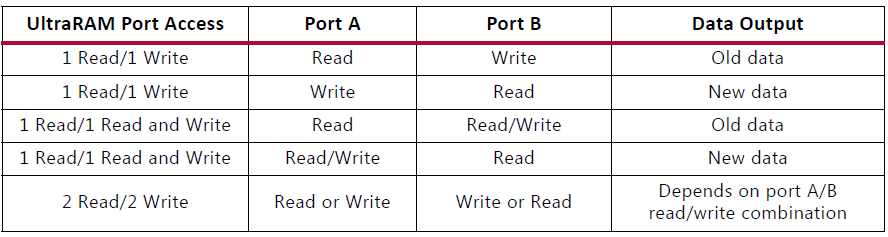

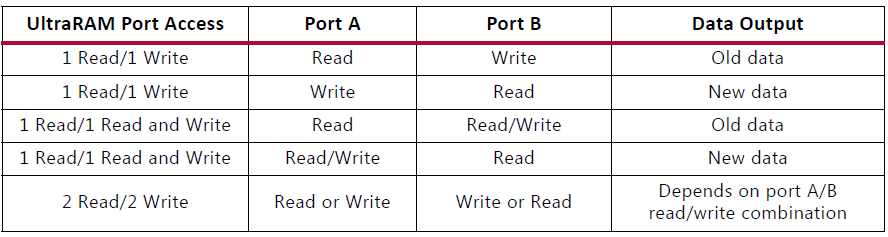

无论是7系列FPGA、UltraScale还是UltraScale Plus系列FPGA,都包含Block RAM(BRAM),但只有UltraScale Plus芯片有UltraRAM也就

2020-12-23 16:57:28

嗨,我对FPGA设计很陌生,更多的是学习如何使用所有工具。无论如何,我的论文的大部分时间都在我的论文中运作良好,这就是BRAM的最后一个难题。我使用ISE模板创建了1kx16(双端口)BRAM,并将

2019-11-01 10:12:40

VR防艾教育模拟系统里,体验者站在半开放式的模拟血管内,学习与艾滋病相关的常见科普知识问答。 科普体验完以后,我们设置了一个“VR抗艾小游戏”互动环节,寓教于乐,让学习印象更深刻。 适用群体

2018-10-15 15:04:54

模拟系统里,体验者站在半开放式的模拟血管内,学习与艾滋病相关的常见科普知识问答。科普体验完以后,我们设置了一个“VR抗艾小游戏”互动环节,寓教于乐,让学习印象更深刻。适用群体:***相关卫生职能机构

2018-10-25 17:06:46

嗨,我对Virtex-4中BRAM的工作频率有疑问。如果有人知道BRAM的最大工作频率是多少?提前致谢以上来自于谷歌翻译以下为原文hi, I have a question about

2018-10-10 11:53:12

原子公众号,获取最新资料第十四章基于BRAM的PS和PL的数据交互在ZYNQ SOC开发过程中,PL和PS之间经常需要做数据交互。对于传输速度要求较高、数据量大、地址连续的场合,可以通过AXI DMA来

2020-09-04 11:08:46

我有一个针对spartan-6(LX45)的项目,该项目在ISE 12.2中没有出现任何问题。最近升级到ISE 14.7项目不再正确构建。问题是BRAM没有正确初始化。此项目中BRAM使用的方法

2019-07-12 15:10:57

我在我的设计中使用Bram,而源和目标的clk是相同的。但我在数据路径中得到保持违规-0.068,我尝试过双同步,但它对时间没有任何影响。锄头来解决这个问题我附上了bram的道路。谢谢

2020-05-25 13:59:33

FPGA的硬核和软核有什么区别呢,有没有使用硬核的开发板,想学习关于FPGA硬核的知识,各位大神有什么建议呢?真心求教

2013-03-05 11:51:54

大家好,我搜索了几个关于初始化BRAM的线程,但我找不到答案。我使用的是Vivado 2015.4。我写了一个coe文件,想把coe文件加载到BRAM中。首先,我添加一个BRAM IP,然后加载

2019-04-17 09:47:17

如题哪位大神能给科普一下产品加密保护方面的知识?

2016-12-08 10:46:50

我目前正在使用Spartan 6板。我初衷了BRAM。我现在想通过UART将数据从BRAM发送到计算机。我还设法让UART与PC连接运行(我使用了两者的预先存在的代码)。如何将数据从BRAM发送到

2020-05-04 17:27:37

Spartan 6 BRAM显然有一个涉及双端口模式和异步时钟的错误。这个部分记录在BRAM用户指南中。我通常使用以下模板暗示在Verilog中阻止rams: reg [7:0] mem [255

2019-05-27 12:16:37

嗨,我正在开发一个项目,我们正在使用Virtex-5 FPGA从ADC捕获信号,样本存储在128K x 256 SRAM上,数据样本由PC采集。我相信Virtex-5为BRAM提供了一个选项,虽然我

2020-06-17 11:31:47

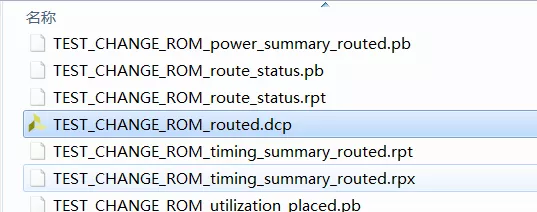

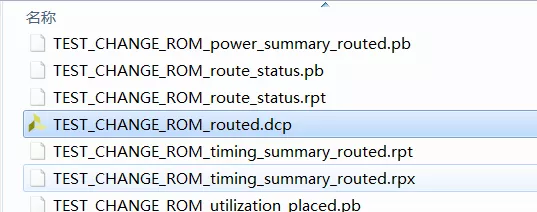

你好,我在FPGA(ISE14)中有一个部分重配置设计,它包含一个由coregen生成的BRAM存储器块。在整个设计布线后,我需要能够改变这些存储器的内容。我知道data2mem程序可以完成类似

2018-10-16 06:40:10

嗨朋友们,我正在尝试使用块内存生成器访问存储在ROM中的.coe文件。我想为此编写一个verilog代码。如何以verilog代码访问存储在BRAM中的像素值?提前致谢。以上来自于谷歌翻译以下为原文

2019-02-26 09:48:33

嗨,我能够在我们的定制板上连接到virtex 7 fpga。我的块级设计具有用于pcie的轴桥作为终点和axi bram。但我无法使用pcie链接从外部处理器访问bram。任何人都可以帮忙解决这个问题吗?大多数情况下,我猜这与地址翻译有关,我无法弄清楚。谢谢

2020-04-22 09:31:47

,DDR在设计中,但它没有被积极使用。它有趣的工作。可能是什么问题呢?有用的建议将是一件非常愉快的事情。谢谢。以上来自于谷歌翻译以下为原文Hello How can I design FPGA BRAM

2019-04-04 15:10:55

我的Vertex 4设计在将其写入外部DRAM之前使用BRAM作为累积数据的缓冲区。 BRAM在RTL代码中手动实例化。用户指南似乎表明只能在配置fpga设备期间初始化BRAM内容。在某些情况下,我的控制器希望在正常操作期间将BRAM内容返回到其初始值,而无需重置整个设计。这可能吗?我该怎么做?

2020-05-28 08:53:15

我正在使用ISE 14.7。我有一个测试项目。在XPS中,它有一个bram_block,其中两个端口用于dlmb_port,ilmb_port用于micrlaze处理器。最初,使用XPS中的“系统

2018-10-25 15:24:01

小编科普D类音频功率放大器的热耗散知识

2021-06-03 06:57:17

我有一个带有64kb BRAM的Microblaze,带有指令和数据空间(一个端口上的标准I和另一个端口上的D)。我有另一个64kb只在一个端口上连接到Microblaze并且只包含数据。第二个端口

2019-03-04 12:09:00

大家好请任何人告诉我。是否有任何方法可以从Virtex 6的FPGA中取出BRAM转储。提前致谢问候Vir_1602以上来自于谷歌翻译以下为原文Hi all would anyone please

2019-03-20 15:37:12

可以从Zynq上运行的Linux控制的额外IP。我要做的就是将一些配置数据写入PL中的BRAM。要做到这一点,根据我在其他地方得到的建议,我提出了一个axi_cdma。所以CDMA有一个

2019-04-19 07:50:52

我有一个程序文件,在模拟开始时必须存储在BRAM中。要加载BRAM,我无法重复使用我的传统测试平台任务,因为内存组织不同,因为这些任务是为ASIC RAM IP编写的。我们正在尝试使用Xilinx

2019-04-22 07:41:01

嗨,我想将数据存储到由axi_bram_controller控制的bram中。那么如何确认我传输的十进制数据而不是十六进制数据呢?问候,索菲亚

2020-05-11 09:21:52

嗨,我想在我的VHDL代码中使用fsm_style属性来在SpartanXC3S200AN设备中的BRAM中实现我的状态机。我在综合后得到的代码和警告如下:HDL代码arcihtecture bla

2019-04-01 12:36:46

嗨,我正在尝试使用自定义IP写入vhdl中的双端口BRAM,该IP生成地址并启用所有信号,但我无法正确写入双端口BRAM。 BRAM的另一个端口就是从PS Zynq读取值并且不写入。这是我写入

2019-04-17 08:15:09

,设计无法满足时序要求。 550MHz是Virtex 5数据表中规定的最大允许频率。当我使用BRAM或FIFO_BRAM实现FIFO时,设计失败。我使用了一个选项,因此未连接的元素不会被修剪(地图阶段的-u

2020-06-13 15:49:32

大家好,我们正在回读我们架构的一些BRAM(配置为双端口RAM)。为避免数据损坏,我们禁用时钟并在回读之前将启用引脚设置为“0”(在两个端口中)。我们只是在我们要回读的BRAM中这样做。但是,我们在

2020-06-11 15:29:20

,这是新型xilinx产品的基础架构,因此DSP-Slices和CLB的宽度可能相等,但我找不到确认的信息。如果有人能够提供有关7系列FPGA中CLB,DSP48E1和BRAM36K / BRAM18K之间水平关系的信息,将会非常有帮助。

2020-07-25 11:04:42

。其中存储器是功耗大户,如xilinx FPGA中的存储器单元Block RAM,因此在这边主要介绍对BRAM的一些功耗优化方法。如图5中实例,虽然BRAM只使用了7%,但是其功耗0.601W占了总

2014-08-21 15:31:23

嗨,我的设计在合成中使用141.5 BRAM瓦片。但是,在Zynq中可以使用140 BRAM瓦片。实施后,这个数量下降到133瓦。我的问题是vivado如何减少这一数量?实施?这点可以导致未来

2018-10-31 16:17:40

嗨,大家好,我想用coe文件初始化BRAM,但有两个问题。首先,当我加载coe文件时,存在文件不存在的错误。见下图:有人可以帮我解决问题吗?其次,我删除了错误文件,因为“文件组”下有两个coe文件

2019-04-18 11:27:07

嗨,大家好,我正在研究Vivado 2014.4,Xilinx KC705。我需要通过Microblaze读取存储在BRAM(coe文件)中的数据进行计算。我是微博阅读部分的新手。有人可以建议我

2020-05-20 08:38:21

我想在Virtex-5 LX50T中实现尺寸为338 KB的BRAM。我觉得V5 FPGA内没有足够的BRAM容量。除了36K和18K块之外,是否有可能使用更小容量的BRAM。是否有任何设置/选项可供设置。请帮助我这方面。JVK yadav

2020-05-27 08:05:46

数字化气象综合服务平台。通过气象科普实物,传播气象科学知识,增强青少年学生的公众气象意识,培养和提高他们防灾抗灾的技能与能力。特别是在于开拓、延伸、补充同学们的课外

2021-03-26 17:17:04

科普知识: 太阳能光伏知识1、 1、 太阳能电池发电原理: 太阳电池是一种对光有响应并能将光能转换成电力的器

2009-02-23 21:35:15 4452

4452

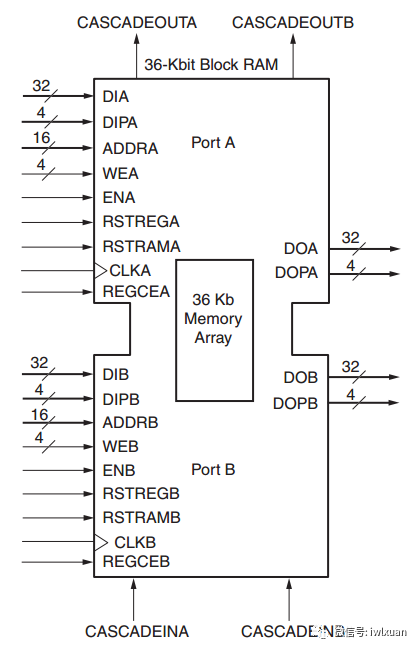

The PLB BRAM Interface Controller is a module thatattaches to the PLB (Processor Local Bus

2012-02-10 16:59:50 31

31 基于位流回读的Virtex_内嵌BRAM的测试方法研究_阎哲

2017-01-07 18:56:13 1

1 最近被这么一个工作折腾了好几天:一个非IPI的Vivado工程(需要全部Verilog手写),在Artix-7 FPGA中实现了一个ARM Cortex-M0 DesignStart软核(老版,没有

2017-02-08 05:40:32 5712

5712

本文档详细介绍的是FPGA教程之CPLD与FPGA的基础知识说明主要内容包括了:一、复杂可编程逻辑器件简介二、CPLD的组成与特点三、FPGA的组成与特点四、CPLD与FPGA的异同五、主要的PLD厂商

2019-02-27 17:09:32 40

40 BRAM和URAM都可级联,只是级联方式不同。在使用BRAM时,我们只需要设定宽度和深度,并根据时钟频率合理选择Latency,也就是选择是否需要使用BRAM自带的输出寄存器或Slice中的寄存器

2019-03-06 15:44:41 29459

29459

本文档的主要人详细介绍的是FPGA基础知识培训教程免费下载包括了:1.什么是FPGA ,2.Actel FPGA整体概述 3.Actel FPGA的性能,4.Actel FPGA的优势

2019-04-23 08:00:00 8

8 1、引言 以交换机设计为例。在交换机设计前期,转发表项是固化在交换机内部的(给FPGA片内BRAM初始值),但是在测试过程中,往往需要对表项进行修改,如果直接修改BRAM的coe文件,则需要重新综合

2020-11-30 15:37:43 3333

3333

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核

2020-12-29 15:59:39 13270

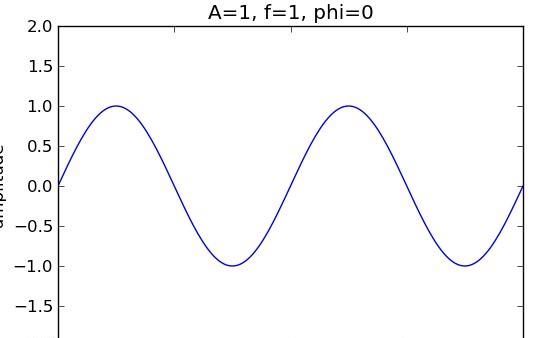

13270 1. 科普:信号与频谱知识! 1 信号简介 信号(singal)简介 我们在生活中经常遇到信号。比如说,股票的走势图,心跳的脉冲图等等。在通信领域,无论是的GPS、手机语音、收音机、互联网通信,我们

2020-10-14 15:40:06 7044

7044

RAM),其中BRAM是block ram,是存在FPGA中的大容量的RAM,DRAM是FPGA中有LUT(look-up table 查找表)组成的。当使用的容量较小会综合成DRAM,容量大的时候综合成BRAM。

2020-12-30 16:27:52 9

9 无论是7系列FPGA、UltraScale还是UltraScale Plus系列FPGA,都包含Block RAM(BRAM),但只有UltraScale Plus芯片有UltraRAM也就是我们所说的URAM。BRAM和URAM都是重要的片上存储资源,但两者还是有些显著的区别。

2022-07-25 17:54:14 7477

7477

无论是7系列FPGA、UltraScale还是UltraScale Plus系列FPGA,都包含Block RAM(BRAM),但只有UltraScale Plus芯片有UltraRAM也就是我们所说的URAM。BRAM和URAM都是重要的片上存储资源,但两者还是有些显著的区别。

2021-01-27 06:55:09 12

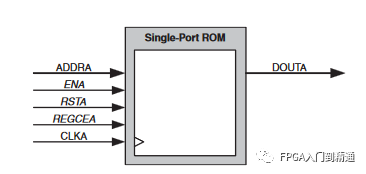

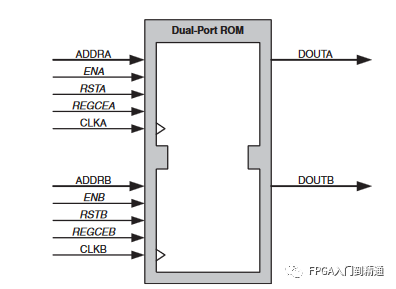

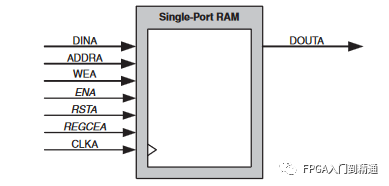

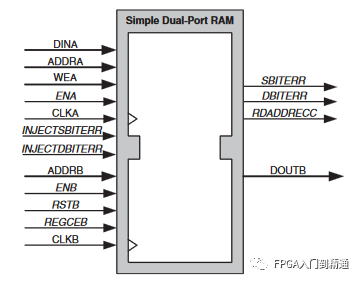

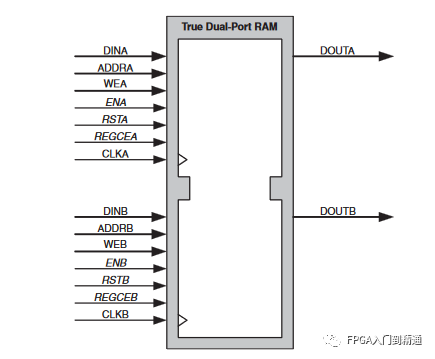

12 Vivado2017.2 中BRAM版本为 Block Memory Generator Specific Features 8.3。BRAM IP核包括有5种类型:Single-port RAM

2021-03-10 06:15:56 19

19 CPLD/FPGA的基本知识讲解。

2021-03-30 09:55:18 34

34 集成在FPGA fabric模块中的RAM,每个xilinx的FPGA中集成有多个这样的BRAM。可以被当作有以下特性的cache:1.不支持像处理器cache中那样的缓存一致性(cache

2021-03-30 10:29:34 2131

2131

FPGA 是可以先购买再设计的“万能”芯片。FPGA (Field Programmable Gate Array)现场可编程门阵列,是在硅片上预先设计实现的具有可编程特性的集成电路,它能够按照

2021-04-30 11:13:54 7393

7393

学习FPGA,笔者推崇的学习方法是先整体再局部。先对FPGA 有一个整体的认识,包括知道有哪些知识点,这些知识点所处的位置和作用。然后在此基础上再逐个突破。

2022-03-22 14:47:21 1053

1053

今天安泰小编为大家科普涡流的有关知识,如果感兴趣的话,就继续往下看吧!

2022-05-19 15:22:36 9444

9444

MicroBlaze可以使用AXI BRAM存放数据和指令。有些客户软件很大,需要把AXI BRAM的空间做到最大。AXI BRAM底层是Block RAM或者Ultra RAM。器件的Block RAM或者Ultra RAM个数,决定了AXI BRAM的大小。

2022-08-02 10:09:05 4186

4186

本篇博文旨在演示如何通过 NoC 从 Versal 应用处理单元 (APU) 访问 AXI BRAM。

2022-11-09 10:24:10 1172

1172 内容来源:美丽株所 END 原文标题:知识科普 | 沙子变“芯”计 文章出处:【微信公众号:机智云物联网】欢迎添加关注!文章转载请注明出处。

2022-11-10 11:20:03 743

743 FPGA端实现SDIO Slave功能 a.FPGA将SDIO Master发送的2KByte数据保存至BRAM。 b.SDIO Master发起读数据时,FPGA从BRAM读取2KByte通过SDIO总线传输给SDIO Master。

2022-11-10 12:22:18 2616

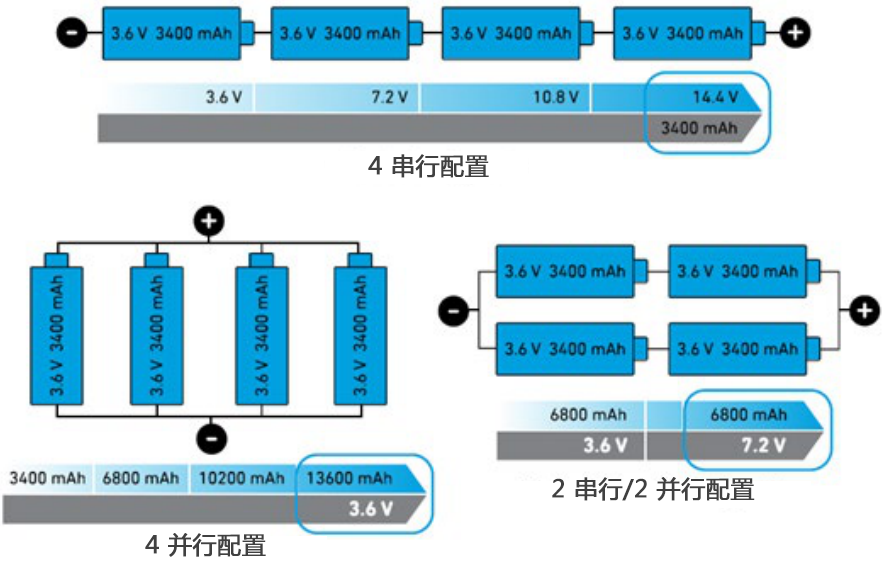

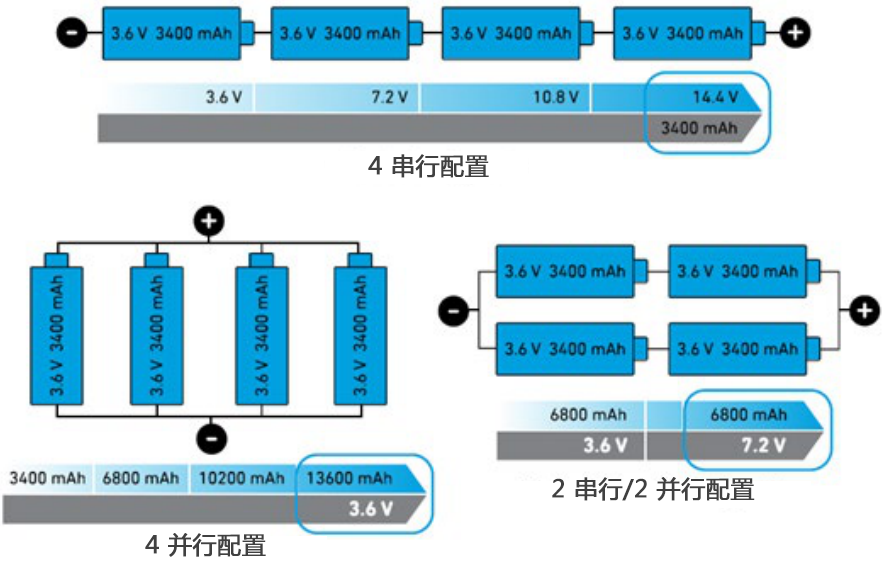

2616 成长计划 电池知识科普与DIY指南 工程师成长计划第十七期,深入电池原理、电路设计及DIY指南。 电池涉及到材料及电化学,往往在工程设计的时候,十分考验工程师的学科交叉知识储备。 电池原理 从伏

2022-11-17 08:25:11 2608

2608 以交换机设计为例。在交换机设计前期,转发表项是固化在交换机内部的(给FPGA片内BRAM初始值),但是在测试过程中,往往需要对表项进行修改,如果直接修改BRAM的coe文件,则需要重新综合、实现、生成bit文件

2023-02-02 14:03:22 1794

1794 FPGA已成为现今的技术热点之一,无论学生还是工程师都希望跨进FPGA的大门。网络上各种开发板、培训班更是多如牛毛,仿佛在告诉你不懂FPGA你就OUT啦。那么我们要玩转FPGA必须具备哪些基础知识呢?下面我们慢慢道来。

(一) 要了解什么是FPGA

既然要玩转FPGA,那我们首先最重要的当

2023-10-27 17:43:33 1410

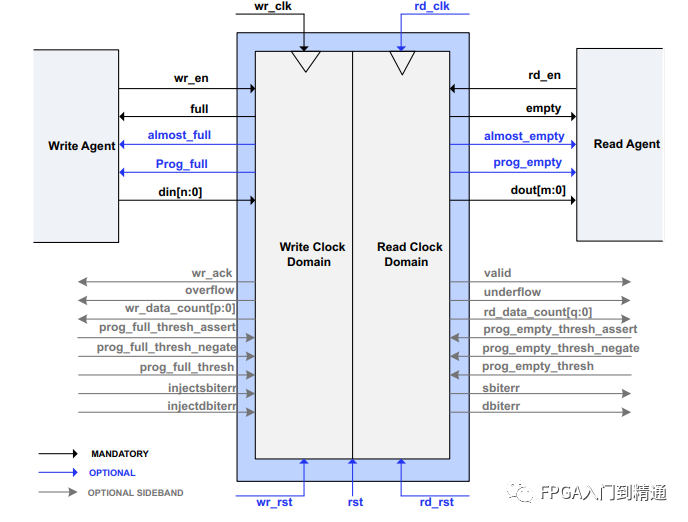

1410 FPGA开发中使用频率非常高的两个IP就是FIFO和BRAM,上一篇文章中已经详细介绍了Vivado FIFO IP,今天我们来聊一聊BRAM IP。

2023-08-29 16:41:49 10361

10361

FPGA的BRAM和LUT等资源都是有限的,在FPGA开发过程中,可能经常遇到BRAM或者LUT资源不够用的情况。

2023-08-30 16:12:04 5313

5313

电气基本知识科普

2023-09-09 10:23:27 6874

6874

PCB高速信号在当今的一个pcb设计中显然已成为主流,一名优秀的PCB工程师,除了在实战项目慢慢积累设计PCB高速信号的经验外,还需通过不断学习来提升自己的知识储存和专业技能。本文捷多邦小编就给大家科普一下PCB高速信号的一些相关布线知识。

2023-09-15 10:19:18 2087

2087 电子发烧友网站提供《基于FPGA的加速基础知识.pdf》资料免费下载

2023-09-18 10:12:20 0

0 科普|电源管理知识

2023-10-17 16:31:55 1262

1262

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 电子发烧友网站提供《FPGA基础知识介绍.pdf》资料免费下载

2024-02-23 09:45:52 34

34 再看末级触发器对BRAM时序性能的影响,下图依次展示了7系列FPGA、UltraScale+和Versal芯片在未使用和使用末级触发器两种情形下时钟到输出的延迟。

2024-04-25 10:42:46 1071

1071

本文将首先介绍FPGA的基础知识,包括FPGA的工作原理以及为什么要使用FPGA等,然后讨论设计和执行FPGA应用所需的工具。

2024-11-11 11:29:44 2486

2486

电子发烧友App

电子发烧友App

评论