引言

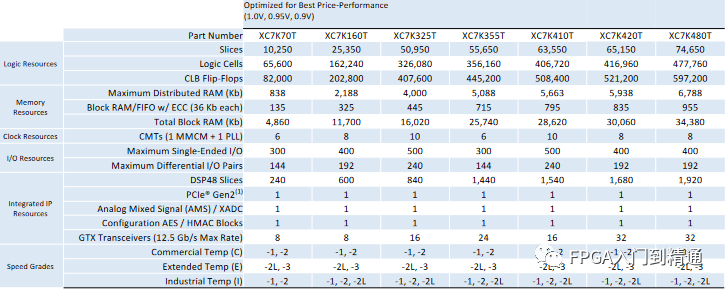

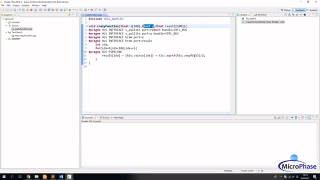

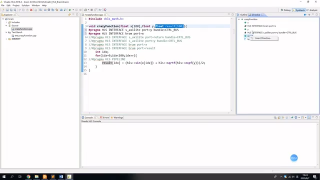

高层次综合(HLS)是一种将高级编程语言(如C、C++或SystemC)转换为硬件描述语言(HDL)的设计方法。在FPGA设计中,设计者可以灵活地利用FPGA内部的资源,如块RAM(BRAM)。虽然HLS设计的IP可以直接使用BRAM,但Block Memory Generator和AXI BRAM Controller仍然在FPGA设计中发挥着重要作用。

HLS设计中的BRAM使用

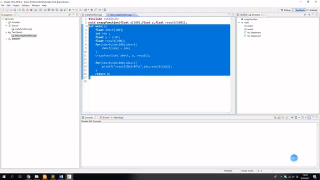

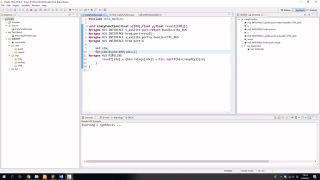

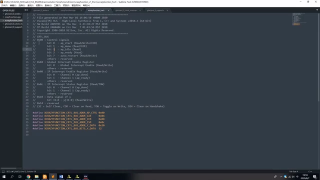

在HLS中,设计者可以使用#pragma指令来指定如何利用BRAM。这些指令可以控制内存的分配方式,优化存储器的使用。使用HLS设计的优点包括:

高层次抽象 : 设计者能够在更高的抽象级别上进行设计,而无需深入处理底层硬件细节。

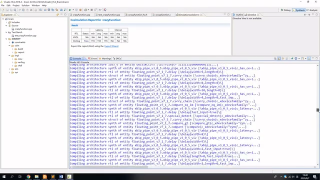

快速设计迭代 : HLS能够快速进行设计验证和迭代,适合快速原型开发和算法验证。

自动优化 : HLS工具通常会自动优化内存访问模式,从而提升设计的性能。

尽管如此,HLS设计仍然面临一些局限性,特别是在复杂系统中,可能无法充分利用AXI协议的所有优势。

Block Memory Generator的作用

Block Memory Generator是用于生成和配置BRAM的关键IP核。它的主要特点包括:

灵活性 : 允许设计者根据需求自定义BRAM的特性,如深度和宽度。支持单端口、双端口等多种类型的BRAM,适应不同应用需求。

高性能 : 生成的BRAM具有高带宽和低延迟,适合需要快速数据存取的应用场景。

Block Memory Generator的定义

Block Memory Generator是一个用于创建和配置FPGA内部块RAM的IP核。它能够生成具有可定制大小和特性的存储器块,以满足特定应用的需求。设计者可以通过Vivado的GUI或编写脚本来定制内存的参数。

Block Memory Generator的特点

灵活性 : 允许设计者根据需要自定义内存的深度和宽度,支持多种配置选项。

高性能 : 生成的块RAM具有高带宽和低延迟,适合需要快速访问的应用。

多种功能模式 : 支持多种读写模式,包括单端口、双端口和多端口模式,适应不同的数据访问需求。

简化设计流程 : 通过提供现成的内存块,减少了设计者在实现内存时的复杂性。

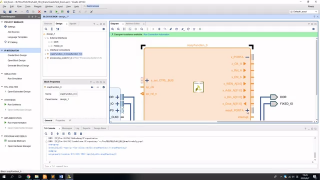

Block Memory Generator与AXI BRAM Controller的关系

Block Memory Generator和AXI BRAM Controller通常结合使用,形成一个完整的内存解决方案。它们之间的关系如下:

生成内存 : Block Memory Generator负责生成具体的块RAM实例,包括其容量和访问特性。

控制访问 : AXI BRAM Controller则作为接口,允许AXI主设备通过AXI协议访问Block Memory Generator生成的内存。

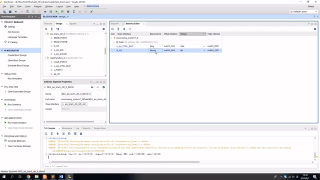

组合使用 : 在FPGA设计中,设计者通常会使用Block Memory Generator生成所需的内存块,然后通过AXI BRAM Controller进行控制和访问。这种组合利用了块RAM的高性能和AXI协议的便利性,简化了内存访问过程。

应用示例

在实际应用中,设计者可能会使用Block Memory Generator生成一个32位宽、1024深度的BRAM,并将其与AXI BRAM Controller连接,以便通过AXI接口进行读写操作。这种配置使得设计能够快速访问内存,适合实时数据处理或存储应用。

AXI BRAM Controller的功能

AXI BRAM Controller是一个中介,允许AXI主设备与BRAM之间进行高效的通信。其优势包括:

标准化接口 : 提供一致的AXI接口,使得不同的AXI主设备能够无缝访问BRAM,简化了内存访问的控制逻辑。

高效的内存访问 : 支持AXI协议的突发传输和高带宽访问功能,适合高性能应用。

AXI BRAM Controller的定义

AXI BRAM Controller是一个IP核,使AXI主设备能够通过AXI协议与FPGA内部的BRAM进行通信。它作为两者之间的桥梁,提供了标准化的接口,简化了设计流程。

存在的原因

AXI BRAM Controller的主要存在原因包括:

标准化接口 : 提供统一的AXI协议,使得不同主设备能够一致地访问BRAM,降低了设计复杂性。

简化设计 : 通过封装复杂的控制逻辑,AXI BRAM Controller减少了设计者在实现内存访问时的工作量,允许快速集成BRAM。

高效的数据访问 : 该控制器支持高带宽的数据传输,适合需要快速存取内存的应用,如信号处理和图像处理。

支持多种传输模式 : 它支持突发传输和单次传输等多种AXI传输模式,能够满足不同应用的需求。

HLS与传统方法的对比

在选择设计方法时,设计者需要考虑HLS与使用Block Memory Generator和AXI BRAM Controller的结合。HLS适合快速原型和算法验证,而Block Memory Generator和AXI BRAM Controller则适合需要高性能和灵活内存管理的复杂系统。

内存生成与配置 : Block Memory Generator提供了更强的灵活性,能够处理复杂内存结构。

接口管理 : AXI BRAM Controller简化了AXI协议的实现,降低设计复杂性。

总结

尽管HLS设计提供了一种便捷的方式来直接使用BRAM,并允许设计者使用pragma指令进行内存优化,但Block Memory Generator和AXI BRAM Controller在FPGA设计中依然发挥着重要作用。它们的结合能够有效提升设计的效率和性能,适应不同的应用需求。因此,设计者应根据具体的项目需求,灵活选择合适的方法,充分利用HLS的高层次抽象和Block Memory Generator及AXI BRAM Controller的功能优势。

-

编程语言

+关注

关注

10文章

1965浏览量

39872 -

BRAM

+关注

关注

0文章

43浏览量

11708 -

HLS

+关注

关注

1文章

135浏览量

25981

原文标题:HLS设计与BRAM的应用比较

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

FPGA设计中BRAM的知识科普

FPGA高层次综合HLS之Vitis HLS知识库简析

使用Vitis HLS创建属于自己的IP相关资料分享

HLS/HLV 流程说明及优势

Vivado中BRAM IP的配置方式和使用技巧

HLS设计中的BRAM使用优势

HLS设计中的BRAM使用优势

评论