上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下DDR模块电路的PCB设计要如何布局布线。

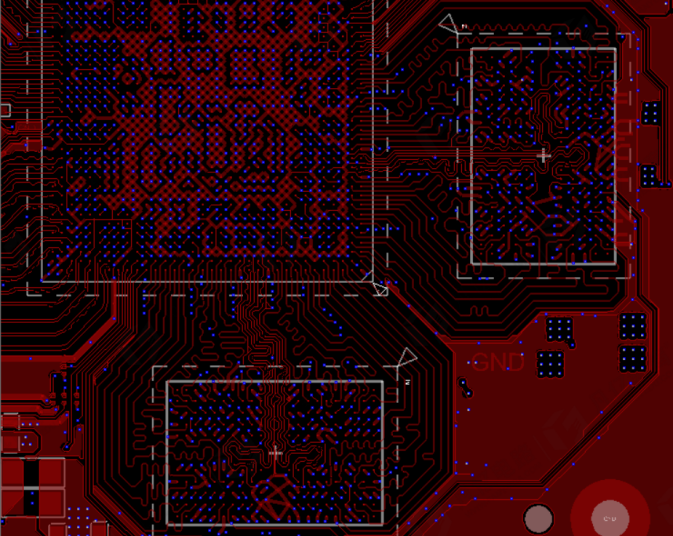

由于RK3588 DDR接口速率最高达4266Mbps,PCB设计难度大,所以强烈建议使用瑞芯微原厂提供的DDR模板和对应的DDR固件,DDR模板是经过严格的仿真和测试验证后发布的。

在单板PCB设计空间足够的情况下,优先考虑留出DDR电路模块所需要的布局布线空间,拷贝瑞芯微原厂提供的DDR模板,包含芯片与DDR颗粒相对位置、电源滤波电容位置、铺铜间距等完全保持一致。

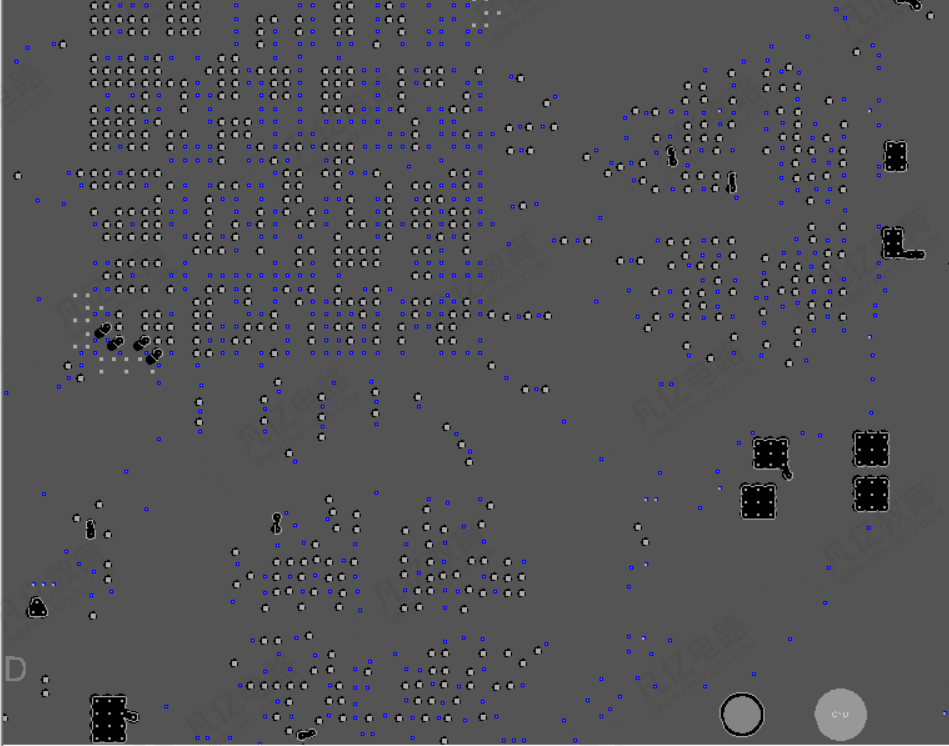

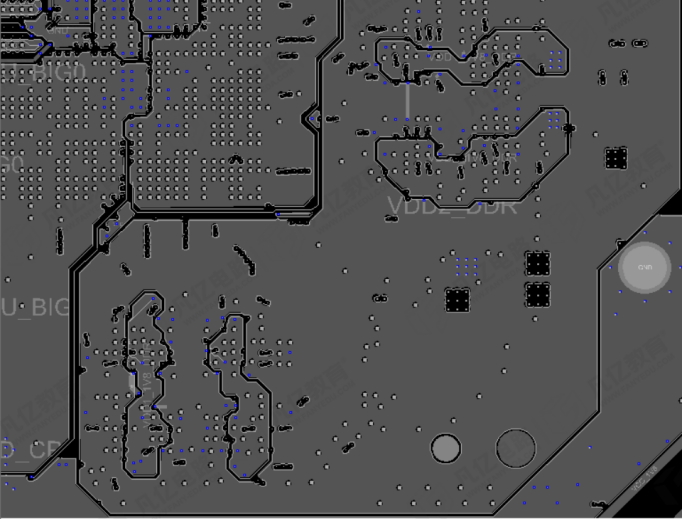

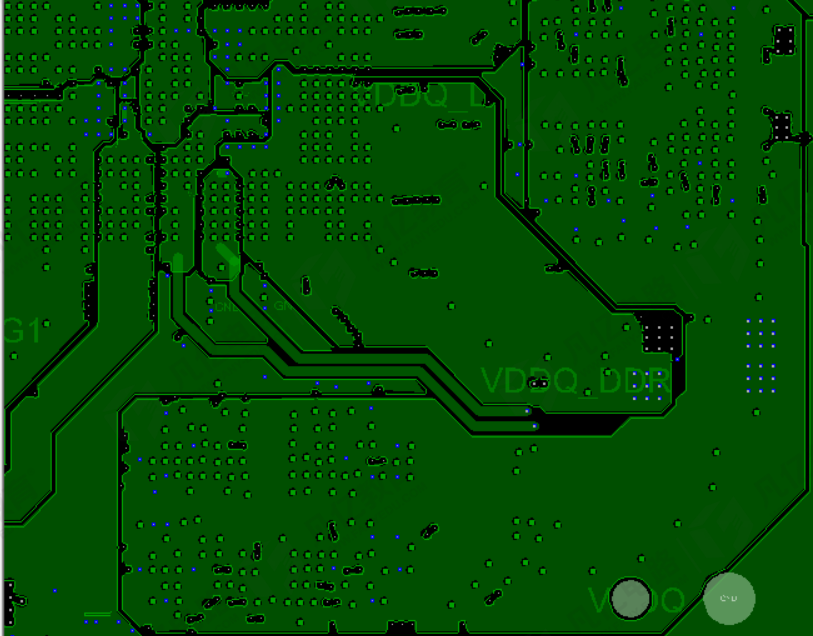

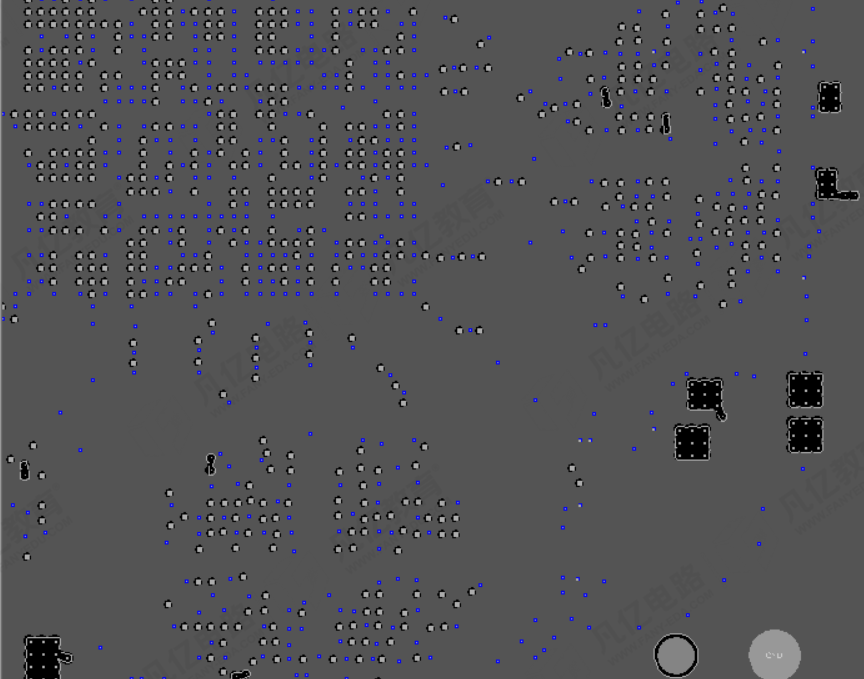

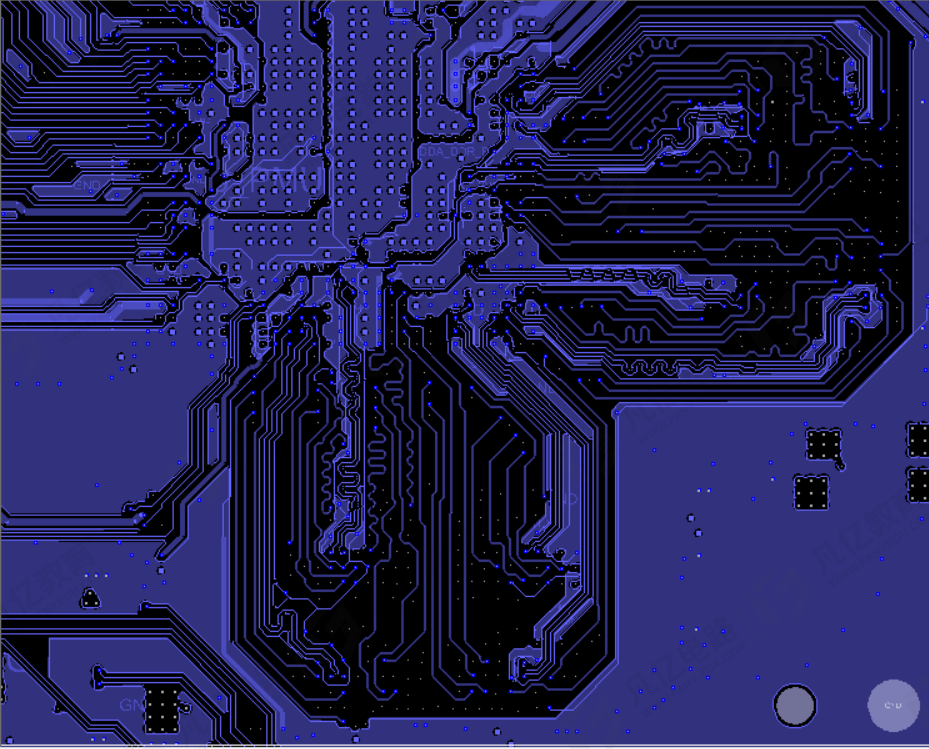

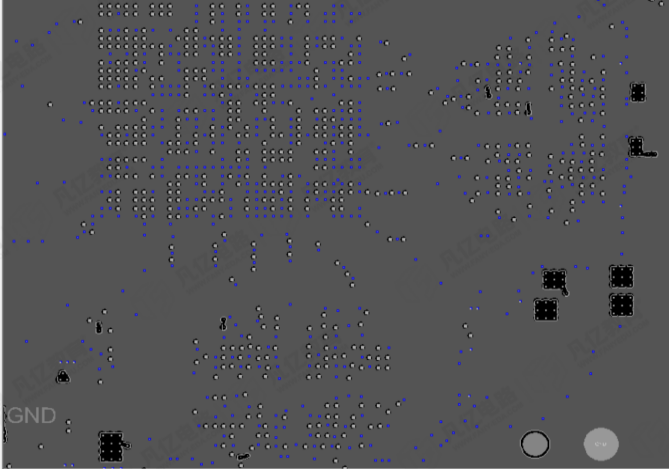

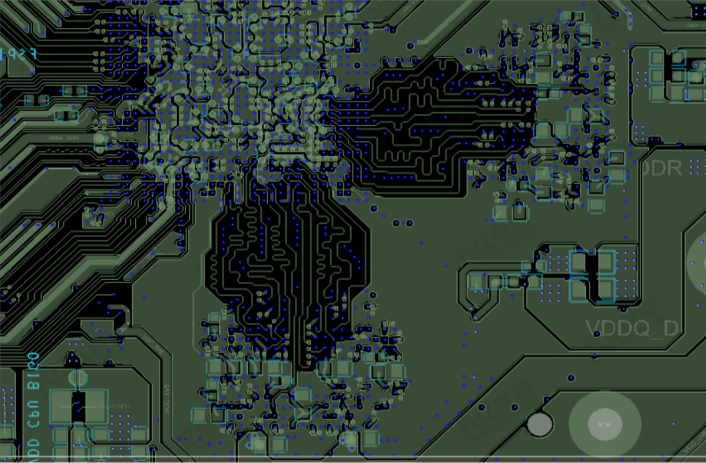

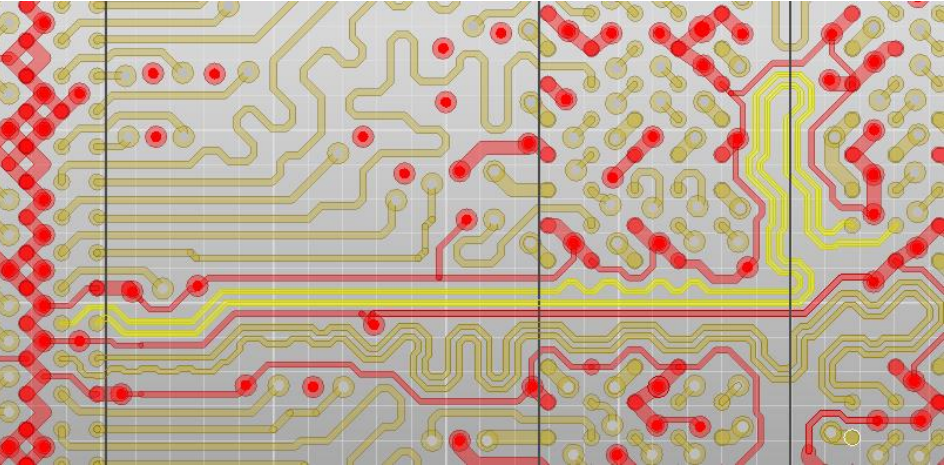

如下8张图(从左至右),分别为:L1-L8层DDR电路走线示意图。

More

如果自己设计PCB,请参考以下PCB设计建议,强烈建议进行仿真优化,然后与瑞芯微原厂FAE进行确认,确认没问题以后再进行打样调试。

Part.

1

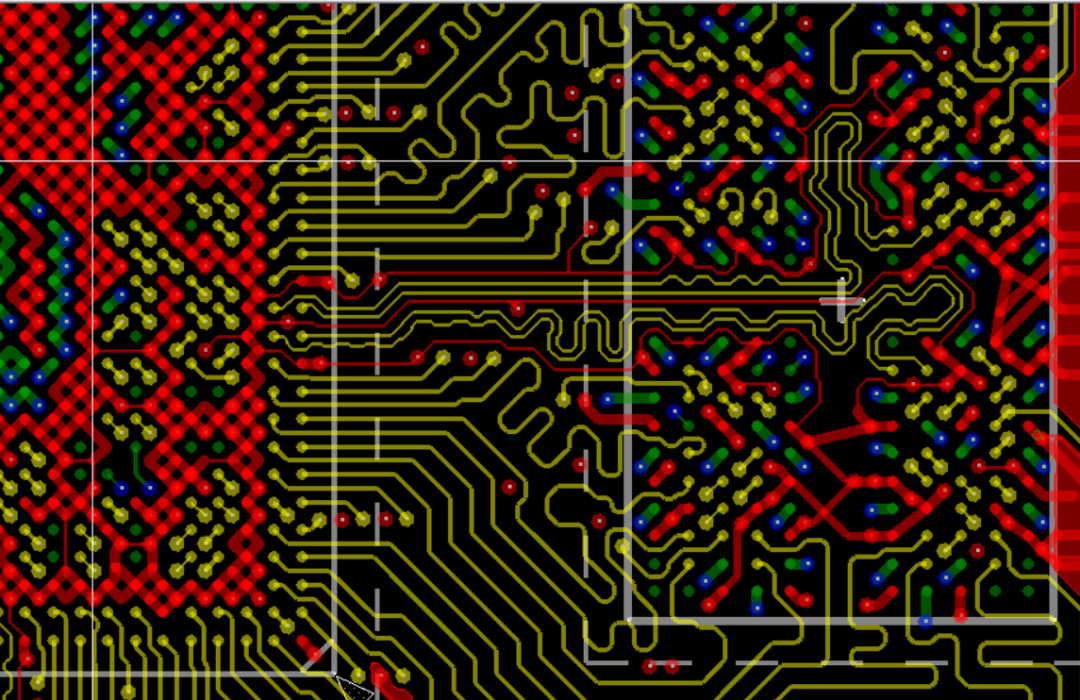

CPU管脚,对应的GND过孔数量,建议严格参考模板设计,不能删减GND过孔。8层通孔的PCB模板,CPU管脚GND过孔设计如下图所示,黄色为DDR管脚信号,地管脚为红色。

Part.

2

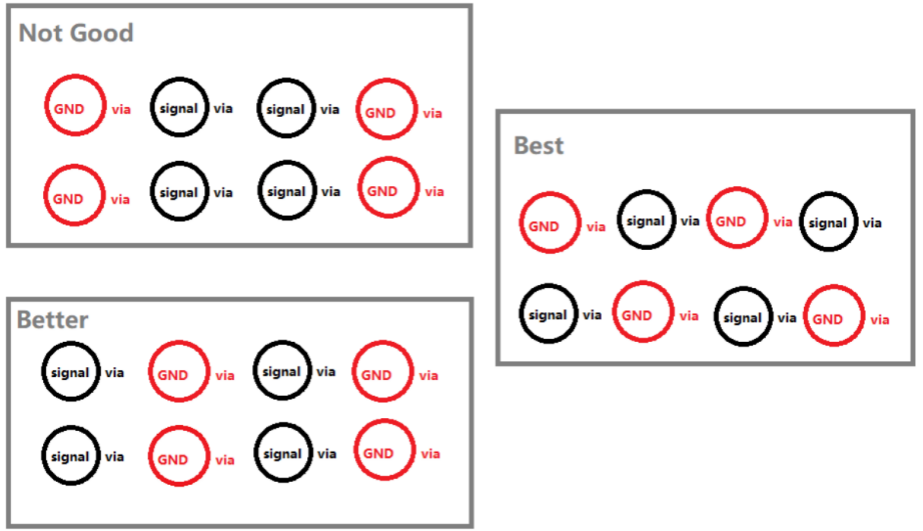

信号换层前后,参考层都为GND平面时,在信号过孔25mil(过孔和过孔的中心间距)范围内需要添加GND回流过孔(黄色为DDR信号,红色为GND信号),改善信号回流路径,GND过孔需要把信号换层前后GND参考平面连接起来。

一个信号过孔,至少要有一个GND回流过孔,尽可能增加GND回流过孔数量,可以进一步改善信号质量,如下图所示。

Part.

3

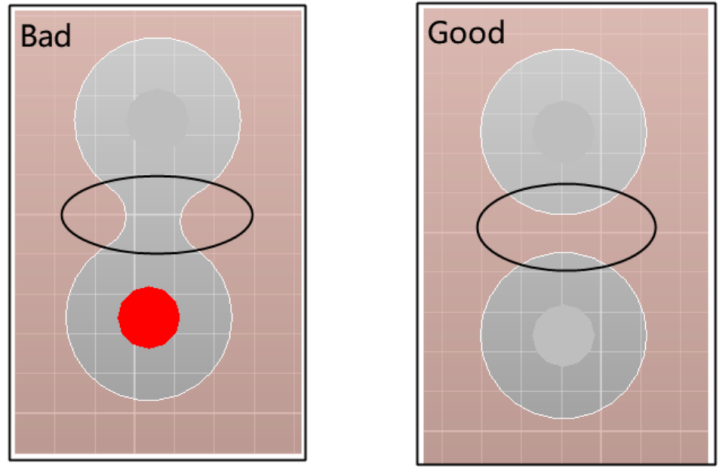

GND过孔和信号过孔的位置会影响信号质量,建议GND过孔和信号过孔交叉放置,如下图所示,虽然同样是4个GND回流过孔,4个信号过孔在一起的情况要避免,这种情况下过孔的串扰最大。

Part.

4

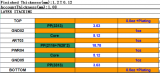

8层板建议DDR信号走第一层、第六层、第八层,DQ、DQS、地址和控制信号、CLK信号都参考完整的GND平面,如果GND平面不完整,将会对信号质量造成很大的影响。

Part.

5

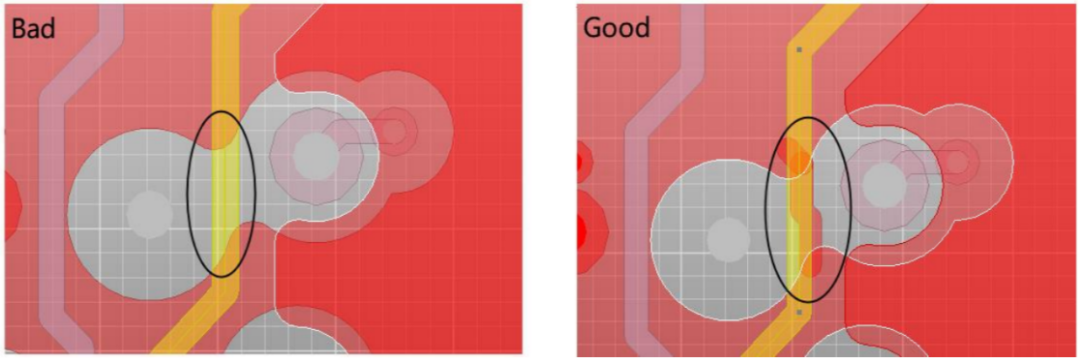

如下图所示,当过孔导致信号参考层破裂时,可以考虑用GND走线优化下参考层,改善信号质量。

Part.

6

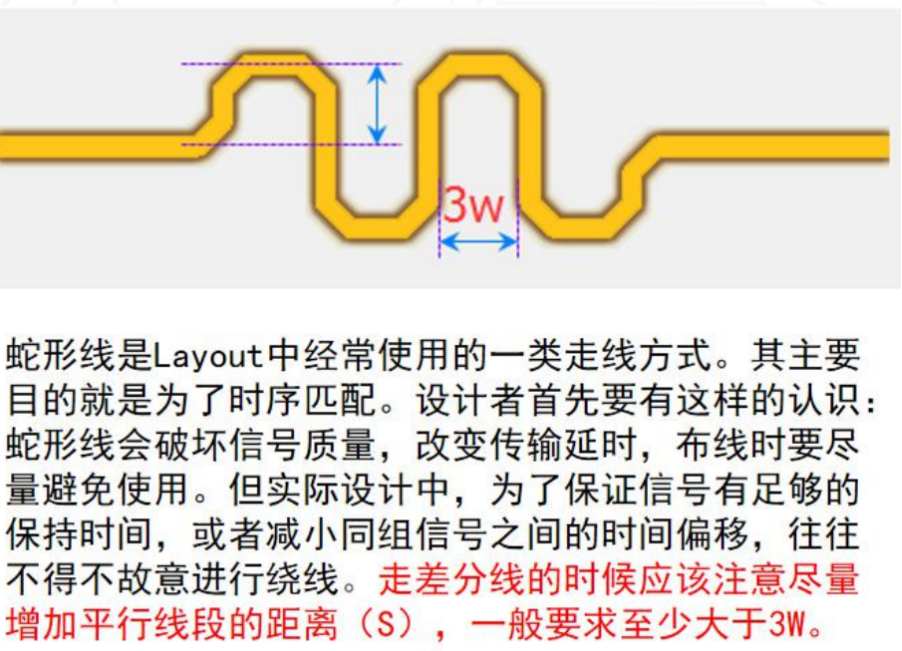

绕线自身的串扰会影响信号延时,走线绕等长时,注意按下图所示。

Part.

7

在做等长时,需要考虑过孔的延时,如下图所示。

Part.

8

非功能焊盘会破坏铜皮,以及增大过孔的寄生电容,需要删除过孔的非功能焊盘,做无盘设计。

Part.

9

走线距离过孔越近,参考平面越差,走线距离过孔钻孔距离建议≧8mil,有空间的地方增大间距。

Part.

10

调整过孔位置,优化平面的裂缝,不要造成平面割裂,起到改善回流路径的作用,如下图所示。

Part.

11

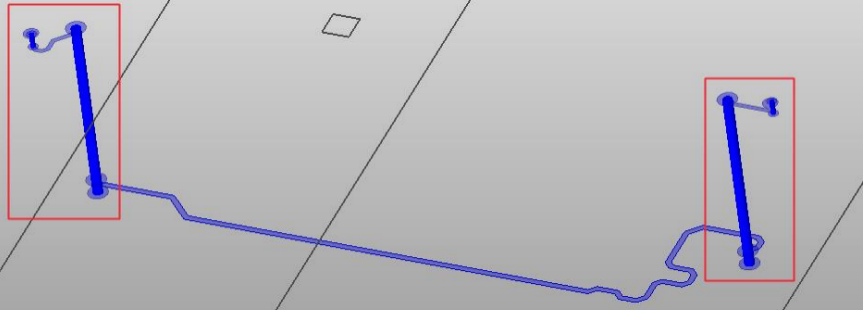

DQS、CLK、WCLK信号需要做包地处理,包地线或铜皮建议间隔≦400mil,打一个GND过孔,如下图所示。

Part.

12

对于VDD_DDR电源,DCDC区域电源换层时,建议打≧6个0503过孔。

Part.

13

对于VDDQ_DDR电源,DCDC区域电源换层时,建议打≧6个0503过孔。

Part.

14

对于VDD2_DDR电源,DCDC区域电源换层时,建议打≧6个0503过孔。

Part.

15

对于VDD1_1V8_DDR电源,电源平面换层时,建议至少打≧2个0402过孔。

Part.

16

每个电容焊盘建议至少一个过孔,对于0603或者0805封装的电容建议一个焊盘对应两个过孔,过孔的位置要靠近管脚放置,减小回路电感。

设计完PCB后,一定要做分析检查,才能让生产更顺利,这里推荐一款可以一键智能检测PCB布线布局最优方案的工具:华秋DFM软件,只需上传PCB/Gerber文件后,点击一键DFM分析,即可根据生产的工艺参数对设计的PCB板进行可制造性分析。

华秋DFM软件是国内首款免费PCB可制造性和装配分析软件,拥有300万+元件库,可轻松高效完成装配分析。其PCB裸板的分析功能,开发了19大项,52细项检查规则,PCBA组装的分析功能,开发了10大项,234细项检查规则。

基本可涵盖所有可能发生的制造性问题,能帮助设计工程师在生产前检查出可制造性问题,且能够满足工程师需要的多种场景,将产品研制的迭代次数降到最低,减少成本。

华秋DFM软件下载地址(复制到电脑浏览器打开):

https://dfm.elecfans.com/uploads/software/promoter/HQDFM%20V3.7.0_DFMGZH.zip

专属福利

上方链接下载还可享多层板首单立减50元

每月1次4层板免费打样

并领取多张无门槛“元器件+打板+贴片”优惠券

华秋电子是一家致力于以信息化技术改善传统电子产业链服务模式的产业数智化服务平台,目前已全面打通产业上、中、下游,形成了电子产业链闭环生态,致力于为行业带来“高品质,短交期,高性价比”的一站式服务平台,可向广大客户提供媒体社区平台服务、元器件采购服务、PCB制造服务及可靠性制造分析服务、SMT贴片/PCBA加工服务,如有相关业务需求,请扫码填写以下表单,我们将为您对接专属服务。

点击上方图片关注我们

原文标题:【华秋干货铺】DDR电路的PCB布局布线要求

文章出处:【微信公众号:华秋电子】欢迎添加关注!文章转载请注明出处。

-

华秋电子

+关注

关注

19文章

542浏览量

15291

原文标题:【华秋干货铺】DDR电路的PCB布局布线要求

文章出处:【微信号:huaqiu-cn,微信公众号:华秋电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

AP2813 SOP8 封装 PCB 布局 7 条黄金规则(工程师必背)

如何设置HDI PCB布局?

高速PCB工程师必看:用仿真三步法,让铺铜从“隐患”变“保障”

【「Altium Designer 25 电路设计精进实践」阅读体验】+第六章节 PCB设计

深入探讨PCB布局布线的专业设计要点与常见挑战

PCB布局布线的相关基本原理和设计技巧

深度解读PCB设计布局准则

如何理解芯片设计中的后端布局布线

高速PCB铺铜到底怎么铺

高速PCB布局/布线的原则

Allegro Skill布线功能之切线、切铜、连接布线介绍

【华秋干货铺】DDR电路的PCB布局布线要求

【华秋干货铺】DDR电路的PCB布局布线要求

评论