声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

463文章

54440浏览量

469405 -

IC

+关注

关注

36文章

6479浏览量

186375 -

测试座

+关注

关注

0文章

28浏览量

7727

发布评论请先 登录

相关推荐

热点推荐

芯片的“第一道体检”:一文读懂CP测试,半导体人必看!

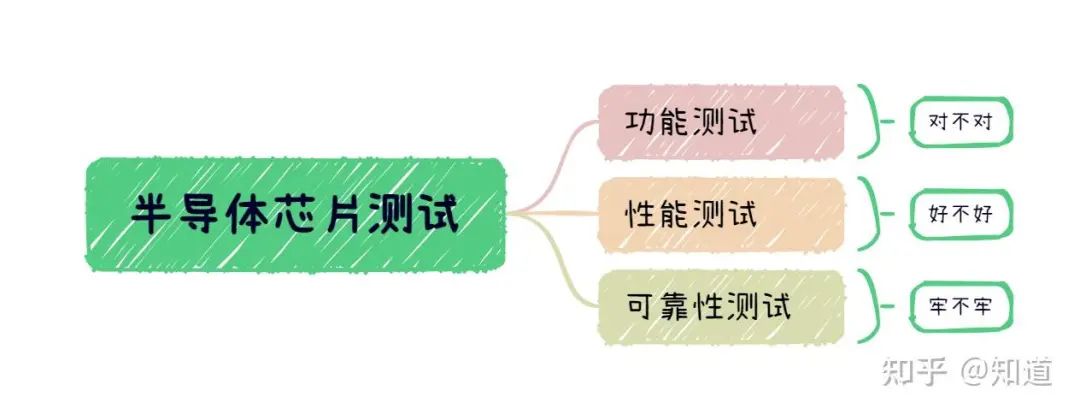

在芯片从晶圆到成品的漫长旅程里,有一道看不见却至关重要的关卡——CP测试。它被称为芯片良率的“守门员”、封装成本的“节流阀”,更是半导体产业链里前端制造与后端封测之间的关键枢纽。今天这篇,用通俗

芯片烧录与芯片测试的关联性:为什么封装后必须进行IC测试?

烧录良率 97%、测试良率仅 82%,根源在于二者工序本质不同:烧录只验证程序写入是否成功,测试则校验芯片电气与功能是否合格。封装过程易引入微裂纹、ESD 损伤等问题,必须通过 FT 终测把关。OTP 等特殊

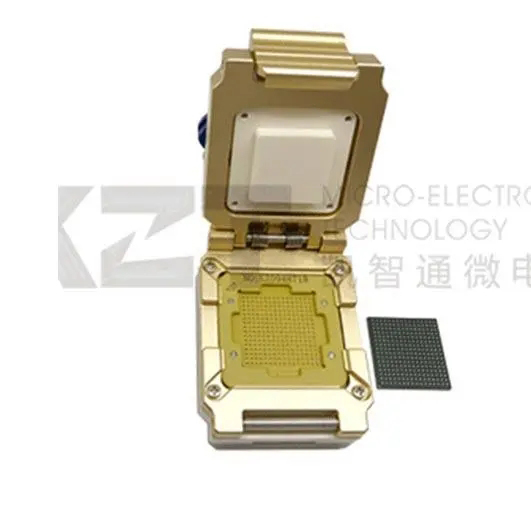

芯片CP测试与FT测试的区别,半导体测试工程师必须知道

个体终检,通过测试座连接引脚,在全温域下全面验证性能参数,保障产品交付质量。二者在测试阶段、对象、目的及技术实现上截然不同,结合两者数据可优化芯片制造良率。

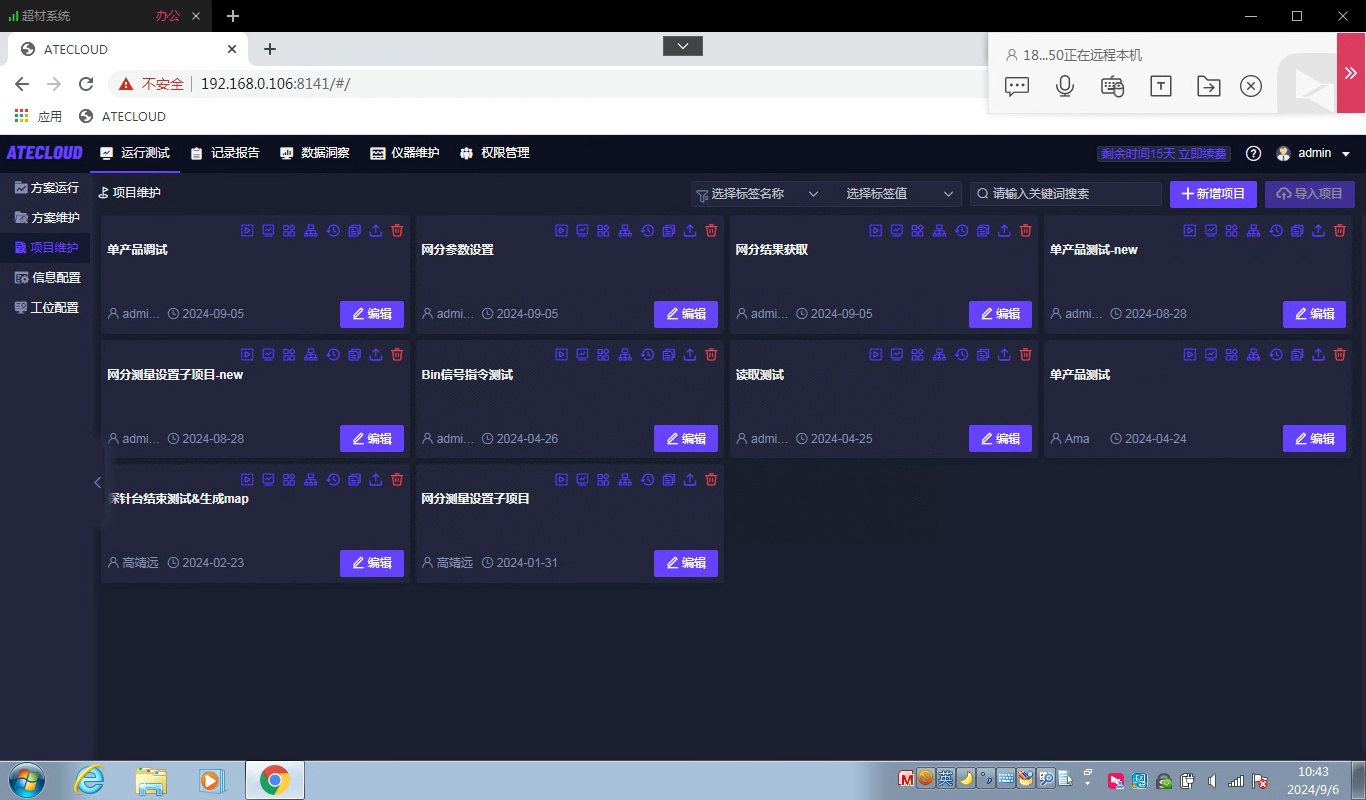

IC测试座定制指南:如何设计高兼容性的芯片测试治具?

IC测试座并非简单标准化连接件,其设计优劣直接影响测试信号完整性、效率与成本。高兼容性测试治具设计需立足“系统匹配”:先明确芯片封装、电气等

用LabVIEW开发的测试软件,支持自定义测试内容,分享给大家。

用LabVIEW开发的测试软件,支持自定义测试内容,分享给大家。链接自取

链接: https://pan.baidu.com/s/14KtGsFmeFJ9ZkeVPygz2YQ?pwd=v8q7 提取码: v8q7

发表于 10-22 10:35

射频芯片该如何测试?矢网+探针台实现自动化测试

射频芯片的研发是国内外研发团队的前沿选题,其优秀的性能特点,如高速、低功耗、高集成度等,使得射频芯片在通信、雷达、电子对抗等领域具有广泛的应用前景。面对射频芯片日益增长的功能需求,针对射频芯片

现代晶圆测试:飞针技术如何降低测试成本与时间

半导体器件向更小、更强大且多功能的方向快速演进,对晶圆测试流程提出了前所未有的要求。随着先进架构和新材料重新定义芯片布局与功能,传统晶圆测试方法已难以跟上发展步伐。飞针

软件定义架构如何满足GNSS模拟测试的开放性需求?

从汽车HIL到5G融合测试,GNSS技术正面临前所未有的复杂需求。如何应对多样化测试挑战?基于软件定义架构(SDA)的Skydel GNSS模拟器,提供灵活扩展、多设备兼容、高效编程控制等能力,让

芯片测试座的定义

芯片测试座的定义

评论