在芯片从晶圆到成品的漫长旅程里,有一道看不见却至关重要的关卡 ——CP 测试。它被称为芯片良率的 “守门员”、封装成本的 “节流阀”,更是半导体产业链里前端制造与后端封测之间的关键枢纽。

今天这篇,用通俗、好懂、能直接拿去用的方式,把 CP 测试讲透

一、先搞懂:CP 测试到底是什么?

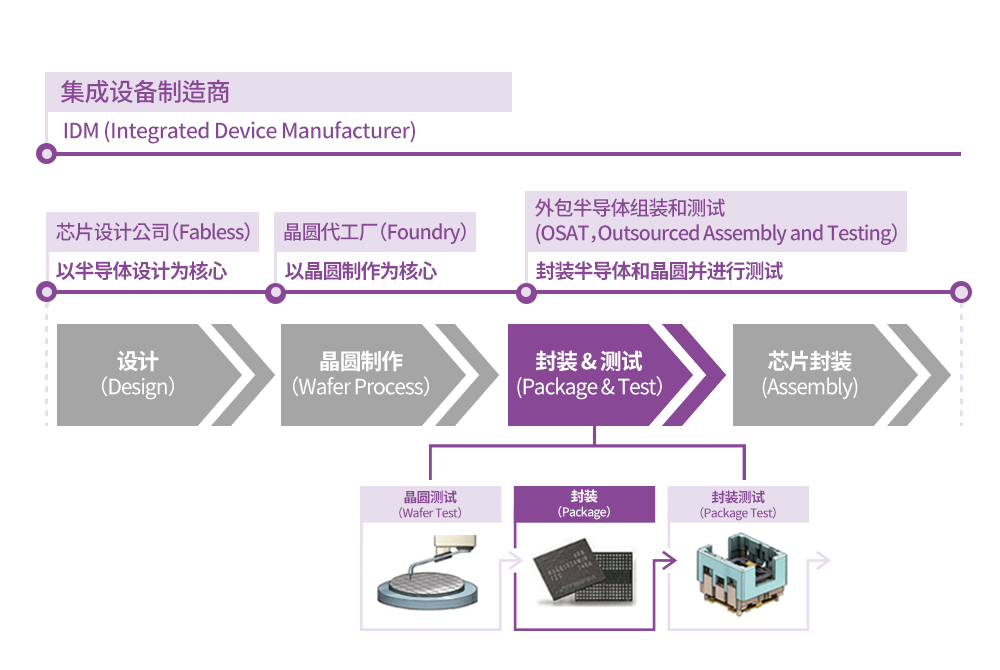

CP = Chip Probing,也叫晶圆测试/中测/Wafer Sort。一句话定义:在晶圆完成制造、还没切割、没封装之前,用探针直接接触每一颗裸片(Die)的 Pad,做全面电性与功能检测,提前筛出坏片,只让好片进入封装。它的位置非常关键:前道工艺(光刻 / 蚀刻 / 沉积) → CP 测试 → 切割 → 封装 → FT 终测 → 成品没有 CP 测试,大量坏片会直接冲进高成本封装环节,钱白花、良率崩、交付拖。

二、CP 测试到底在测什么?

CP 不是简单 “通不通电”,而是一套标准化、自动化、可量化的 ATE 结构化测试,主要分两大类:

1. 参数类测试(Parametric Test)

看电性能是否达标,输出具体数值,用 Spec 判断 P/F:

2. 功能类测试(Functional Test)

只给 Pass/Fail,验证芯片能不能用:

- Logic 逻辑测试:Scan/Stuck/Transition

- MBIST 存储器内建自测试:SRAM/Flash 等读写、修复

- Bscan 边界扫描:IO 管脚与链路完整性

- IP 功能测试:接口、模拟、射频等模块验证

简单说:参数测 “体质”,功能测 “智商”,两项都过才算合格 Die。

三、CP 测试怎么跑?一套流程讲清楚

整个过程高度自动化,人几乎不用插手:

- 晶圆上片 → 光学对准(Al-mark)

- 探针台移动 → 探针卡扎针 Pad

- ATE 发信号 → 芯片回传电信号

- 软件判 Pass/Fail → 分 Bin 标记

- 整片测完 → 输出 Datalog + Wafer Map

- 坏片标记墨水 → 封装直接跳过坏 Die

关键设备 “三巨头”

CP 测试离不开这套黄金组合:

- ATE 测试机:大脑,发指令、判结果、跑向量

- Prober 探针台:定位平台,移动 Wafer、控温

- Interface(PCB+Probe Card):桥梁,信号从机台到芯片的通路

工程常用单 Die 针卡,便宜灵活;量产用多 Site 并行,速度拉满。

四、最实用的知识点:Bin 是什么?

测试结果会用Bin ID给每颗 Die “贴标签”:·Hard Bin:大分类, 例如

- Bin1:Pass(良品,绿色)

- Bin2:接触不良

- Bin3:功耗 / IDDQ

- Bin4:DC 参数

- Bin5:Logic 功能

- Bin6:Memory 异常

- Bin7:IP 功能异常

·Soft Bin:细分失效位,4 位数字,精准定位问题点最后生成的Wafer Map,就是整片晶圆的 “体检报告”,哪里集中坏、边缘坏还是中心坏、工艺问题还是测试问题,一目了然。

·Soft Bin:细分失效位,4 位数字,精准定位问题点最后生成的Wafer Map,就是整片晶圆的 “体检报告”,哪里集中坏、边缘坏还是中心坏、工艺问题还是测试问题,一目了然。

如何看CP的wafer map?

假设一片 Wafer 有 1000个 Die,一个 Die 有 1000 个测试参数,每个测试参数给它一个 ID。假设从第一项测试到第 1000 项:

假设测试到419 Fail,就标示 Bin 419+1,后面不测试

假设测试到410 Fail,就标示 Bin 410+1,后面不测试

以此类推,如果测试1,000 项完毕,就标示 Bin 1,代表 Good Bin,通常是绿色。下图则是用 Bin ID,产生 Wafer Map的Bin 视图,绿色表示Good Bin, 其他颜色分别表示测到X-1个测试参数时Fail的die。

五、CP 测试为什么非做不可?3 个核心理由

1. 省大钱!拒绝为坏芯片买单

封装成本远高于测试成本。CP 提前筛坏片 = 不把钱浪费在废品上,百万颗芯片就是几百万真金白银。

2. 盯良率!给 Fab 工艺 “看病”

Wafer Map + Bin 分布 = 工艺缺陷 X 光片。

- 边缘集中坏 → 制程均匀性问题

- 随机坏 → 颗粒污染、微缺陷

- 某类 Bin 暴增 → 向量 / 针卡 / 机台异常

直接指导工艺改善,拉高产线良率。

3. 保品质!给芯片 “分级定价”

不是所有 Pass 片性能都一样。CP 可按频率、功耗、Vmin 分级,高端卖高价、低端走性价比,价值最大化。

六、CP vs FT:别再傻傻分不清

很多人刚入行都会搞混这两个,一张表看懂: 一句话:CP 是 “产前筛查”,FT 是 “出厂体检”,缺一不可。

一句话:CP 是 “产前筛查”,FT 是 “出厂体检”,缺一不可。

七、低良率怎么破?PDE/PIE 分工一目了然

CP 良率崩了,谁来扛?行业标准分工:

- PDE:测问题、向量问题、针卡 / 机台硬件、Spec 合理性、Vmin 抬压、BSL 诊断

- PIE:工艺缺陷、失效模型、PFA、产线 Excursion 改善

先排除 Test issue,再盯 Spec/Vmin,最后查 Process。

八、总结:CP 测试的真正价值

对半导体行业来说,CP 测试不只是一道工序,它是:

- 成本控制的第一道防线

- 良率提升的最重要数据源

- 芯片品质的准入通行证

- 设计与工艺之间的沟通语言

没有 CP,就没有稳定的良率、可控的成本、可靠的芯片。

-

芯片

+关注

关注

463文章

54377浏览量

468987 -

测试

+关注

关注

9文章

6373浏览量

131639 -

半导体

+关注

关注

339文章

31192浏览量

266320

发布评论请先 登录

从原理到应用,一文读懂半导体温控技术的奥秘

优必选防疫机器人助力深圳 筑起战疫第一道防线

GRGTEST | 一文带你了解半导体检测与量测技术区别

芯片的“第一道体检”:一文读懂CP测试,半导体人必看!

芯片的“第一道体检”:一文读懂CP测试,半导体人必看!

评论