首先开门见山的回答这个问题——LUT的作用是 实现所有的逻辑函数 ,也就是类似于计算Y=A&B+C+D之类的算式结果!

LUT是什么构成的?

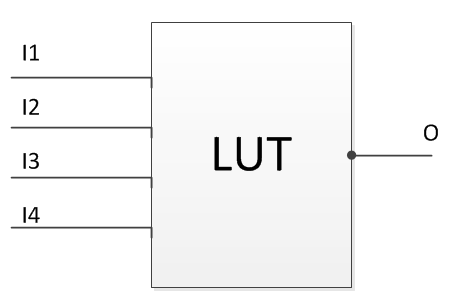

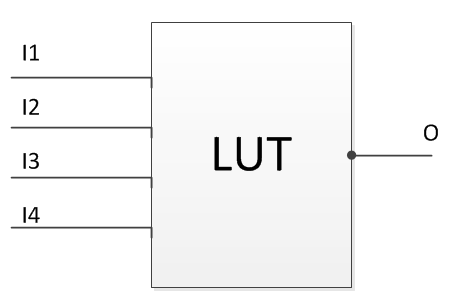

xilinx的LUT是4输入1输出的 RAM ,也就是4根地址线的,一根数据线的RAM,并且I1是高地址位,I4是低地址位,样子参考下图。I1到I4就是地址线,O是输出数据线。

RAM怎么实现逻辑运算?

假设要实现运算Y=A&B+C+D。假设I1代表A,I2代表B,I3代表C,I4代表D,O代表Y。此时将下表存入LUT中。从下表可以看出,LUT存储的就是函数Y=A&B+C+D的真值表。 **4个输入信号的地址对应的位置上存储的就是4个地址进行逻辑运算后的真值!** 这样任何4输入的所有逻辑运算都可以通过存取真值表的方法实现。一旦输入地址中的任何一个数,立马就会输出存储位置上对应的结果。

verilog怎么实现上面的函数呢?

reg Y;

reg [3:0] I ;

always@(*)begin Y=(I[0] & I1) | I2 | I3;end

请注意( )里面是 ,代表不需要时钟,实现的是组合逻辑。如果最后一行变成如下:

always@(posedge clk)begin Y=(I[0] & I1) | I2 | I3;end

则生成的不是一个LUT是一个LUT加一个触发器FF。如下图。

-

RAM

+关注

关注

8文章

1398浏览量

119823 -

触发器

+关注

关注

14文章

2050浏览量

63042 -

LUT

+关注

关注

0文章

52浏览量

13074 -

FPGA系统

+关注

关注

0文章

11浏览量

7237 -

Verilog语言

+关注

关注

0文章

113浏览量

8723

发布评论请先 登录

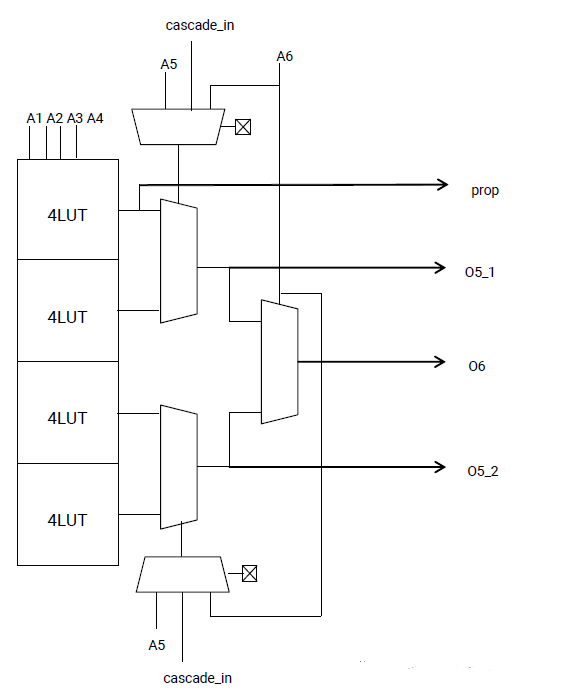

初识FPGA CLB之LUT实现逻辑函数

FPGA中LUT设计

使用的LUT触发器对的数量与Slice Register和Slice LUT的关系是什么?

LUT实现的逆变器真的是FPGA上的逆变器吗?

LUT和Kintex 7 FPGA芯片中的FF所需的资源

Spartan 6 FPGA LUT中是否有pmos和nmos transisors?

LUT名字的数字含义是什么?

LUT如何构成逻辑函数

FPGA中实现LUT设计的简介

FPGA——LUT/FDRE/FDCE/FDSE/FDPE

FPGA中的LUT有什么作用

LUT是什么构成的?FPGA里的LUT有什么作用?

LUT是什么构成的?FPGA里的LUT有什么作用?

评论