查找表(Look-Up-Table)

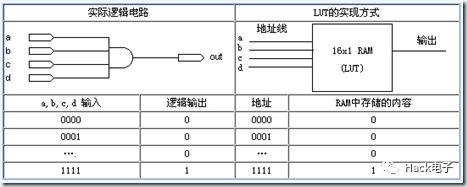

LUT就是查找表,对于4输入的LUT而言,实际上就是4位地址位,一位数据位的存储器,能够存储16位数据,所以我们在FPGA设计中可以用LUT组建分布式的RAM。

LUT的一个重要功能是逻辑函数发生器。本质上,逻辑函数发生器存储的是真值表(Truth Table)的内容,而真值表则是通过布尔表达式获得。在vivado中,打开网表文件,选择相应的LUT,在property窗口中可以看到真值表。

如果用6输入的LUT实现4输入LUT的功能,那么就浪费了1-16/64=75%的资源,所以采用少输入的LUT可以更好的节省面积和资源

因为当输入数据的位数远大于一个LUT的输入时,就需要用多个LUT级联来实现逻辑,那么级联产生的延时也就不可避免了,这样就会制约系统的运行频率。那么为了避免级联数过于多,就采用插入寄存器的方法来实现

通过LUT代替组合逻辑,而LUT中的值只和输入有关,因此组合逻辑的功能由输入决定,不在和复杂度有关;

CLB可配置逻辑快

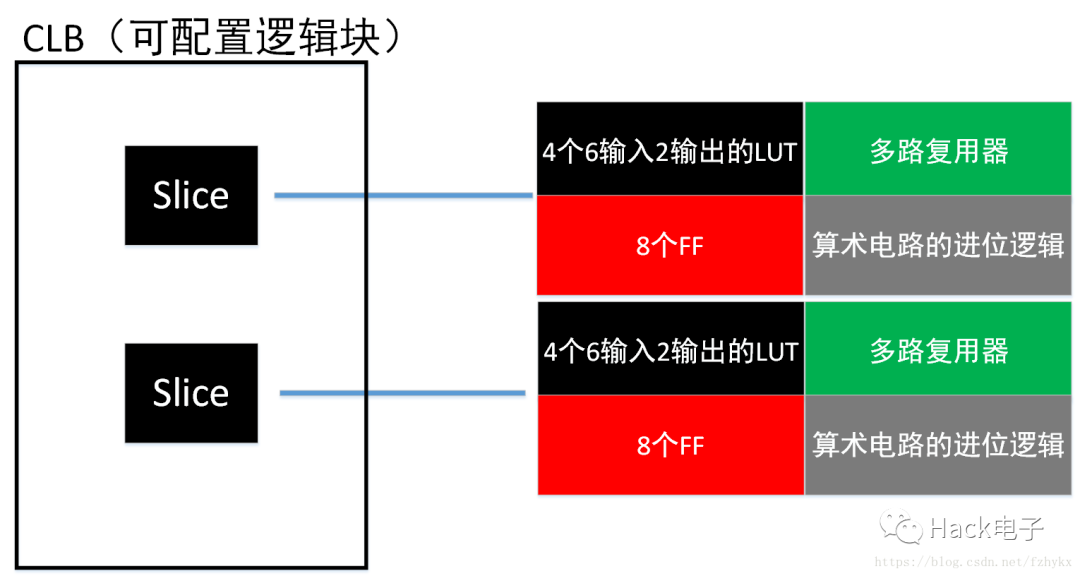

CLB是xilinx基本逻辑单元,每个CLB包含两个slices,每个slices由4个(A,B,C,D)6输入LUT和8个寄存器组成(中间应该还有一些选择器、与非门、或非门之类的东西)。

”logic cells” 是 Xilinx 创造出来的一个市场用的刻度,可以用来衡量不同内部结构甚至不同厂商的资源情况。

LC逻辑单元

“logic cells”代表的是一个没有其他任何功能的4输入LUT,在老一些的Xilinx的FPGA中,他们使用LUT的数目乘以1.2来计算LC的数目,因为一个LUT中还有一个进位链和MUX。

在较新的FPGA中,Xilinx采用了6输入LUT,这时他们采用系数1.6。

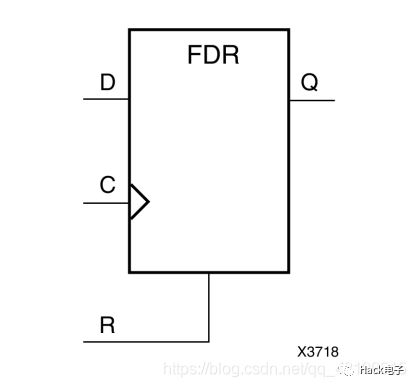

FDR : D Flip-Flop with Synchronous Rsest

同步清除D触发器。FDR 拥有一个时钟输入接口,一个D触发器数据接口,一个同步复位接口和一个触发器输出接口,当同步复位接口为高电平时,时钟的上升沿触发寄存器复位(置0);当同步时钟接口为低电平时,时钟的上升沿触发寄存器装载数据接口的数据。

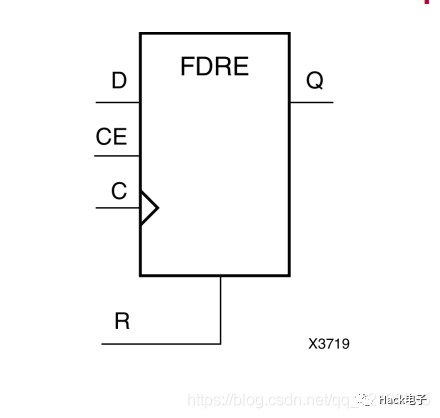

FDRE:D Flip-Flop with Clock Enable and Synchronous Reset 带使能功能的同步清除D触发器,相比与FDR多了一个使能接口,当同步复位接口为高电平时覆盖所有其他输出,时钟的上升沿触发寄存器复位(置0);当同步时钟接口为低电平且使能接口为高电平时,时钟的上升沿触发寄存器装载数据接口的数据。

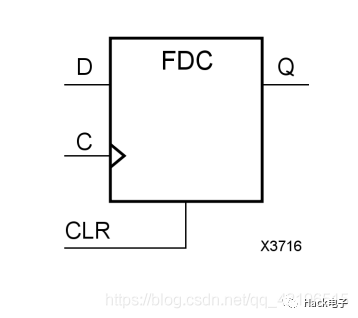

FDC :: D Flip-Flop with Asynchronous Clear 带异步清除D触发器 ,与 FDR的区别是。当CLR置为高电平时,不需要等到下一个时钟的上升沿就可以复位寄存器。

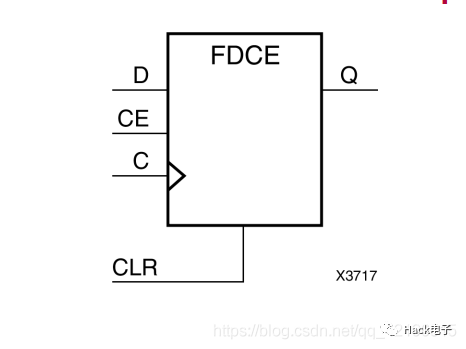

FDCE:D Flip-Flop with Clock Enable and AsynchronousReset 带使能功能的异步清除D触发器,相比与FDRE将同步复位变化成异步复位,当同步复位接口为高电平时,直接触发寄存器复位(置0);当同步时钟接口为低电平且使能接口为高电平时,时钟的上升沿触发寄存器装载数据接口的数据。

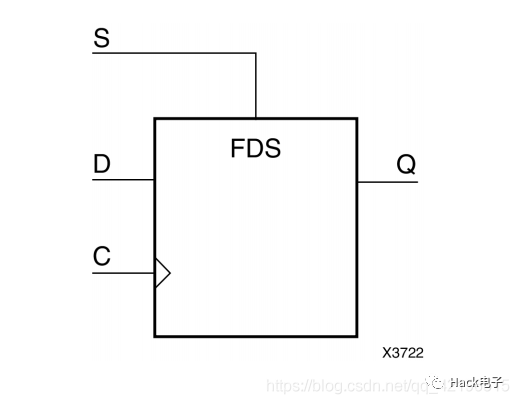

FDS:D Flip-Flop with Synchronous Set 带同步置位的D触发器 当置为端为低电平时,在时钟的上升沿触发数据保存在触发器中,当置位端为低电平时,在一个时钟的上升沿触发导致触发器清0

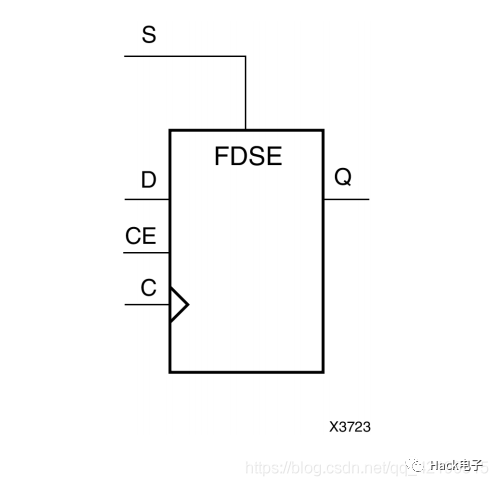

FDSE:D Flip-Flop with Clock Enable and Synchronous Set 带时钟使能和同步置位的D触发器。当置位端为高电平是覆盖所有输出,一个时钟的上升沿触发导致寄存器置位,当置位端为低电平和时钟使能位为高电平时,在一个时钟的上升沿触发导致寄存器装载数据口的数据。

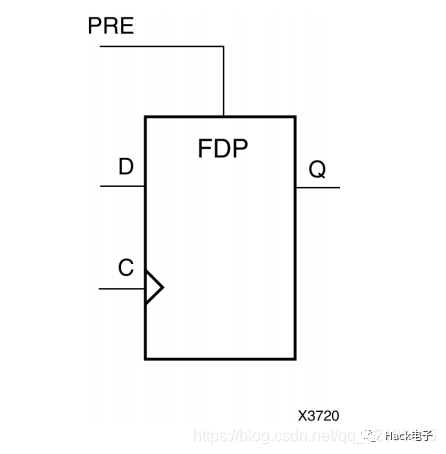

FDP:D Flip-Flop with Asynchronous Preset 带有异步预置的D触发器 相比FDS不需要等到时钟的上升沿,即刻可进行置位。

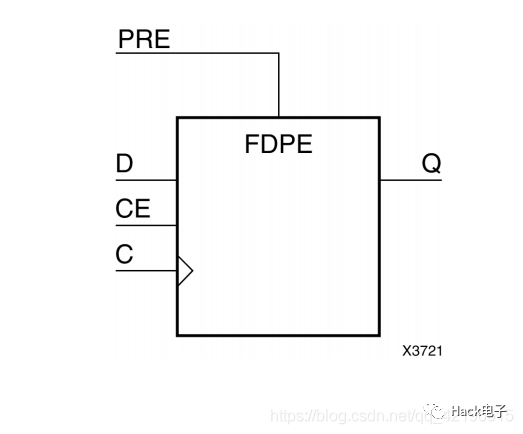

FDPE:D Flip-Flop with Clock Enable and Asynchronous Preset 带有时钟使能和异步置位的D触发器 相比于FDSE不需要等到时钟的上升沿,即刻可进行置位。

使用always块综合实现各种触发器

module exp(

input clk,

input rst,

input A,

input B,

output reg Q,

output reg Q1,

output reg Q2,

output reg Q3

);

//or posedge rst

always @(posedge clk or posedge rst) begin //异步复位 综合出FDCE

if(rst)

Q<=0;

else begin

Q<=A|B;

end

end

always @(posedge clk ) begin //同步复位 综合出FDRE

if(rst)

Q1<=1;

else begin

Q1<=A|B;

end

end

always @(posedge clk or posedge rst) begin//异步置位 综合出FDPE

if(rst)

Q2<=1;

else begin

Q2<=A|B;

end

end

always @(posedge clk) begin//同步置位 综合出FDSE

if(rst)

Q3<=1;

else begin

Q3<=A|B;

end

end

endmodule

审核编辑 :李倩

-

FPGA

+关注

关注

1664文章

22502浏览量

639149 -

存储器

+关注

关注

39文章

7756浏览量

172187 -

触发器

+关注

关注

14文章

2065浏览量

63549

原文标题:FPGA——LUT/FDRE/FDCE/FDSE/FDPE

文章出处:【微信号:Hack电子,微信公众号:Hack电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

工程师高培解读XilinxVivadoFPGA设计进阶与AI自动编程

京微齐力HME-P2飞马系列FPGA产品概述

深入解析IGLOO2 FPGA与SmartFusion2 SoC FPGA:性能、规格与应用考量

深入解析IGLOO2 FPGA和SmartFusion2 SoC FPGA:特性、参数与应用

【黑金云课堂笔记】第一~二期知识点总结

探索IGLOO2 FPGA与SmartFusion2 SoC FPGA的电气特性与应用潜力

Microsemi IGLOO2 FPGA与SmartFusion2 SoC FPGA深度剖析

【ALINX选型】AMD Kintex UltraScale+ 系列 FPGA 开发板速选

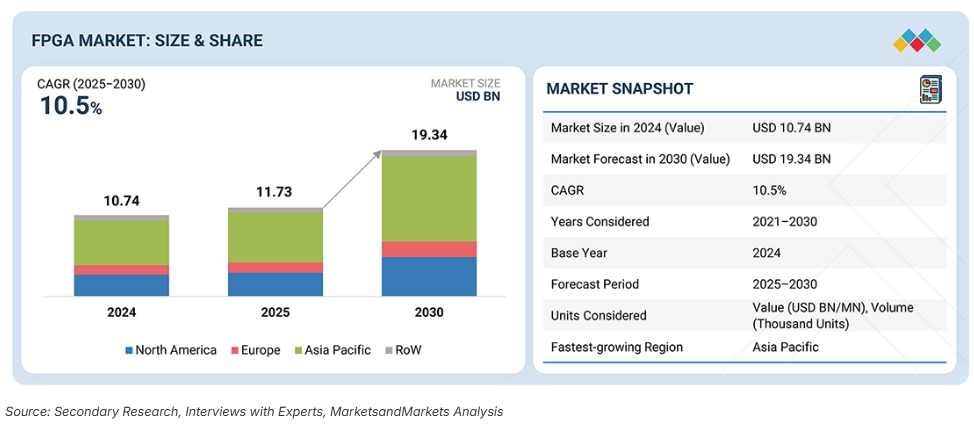

MarketsandMarkets FPGA行业报告,2026~2030 FPGA市场洞察

使用Xilinx 7系列FPGA的四位乘法器设计

Altera Agilex™ 3 FPGA和SoC FPGA

FPGA——LUT/FDRE/FDCE/FDSE/FDPE

FPGA——LUT/FDRE/FDCE/FDSE/FDPE

评论